IDDQ测试原理及方法

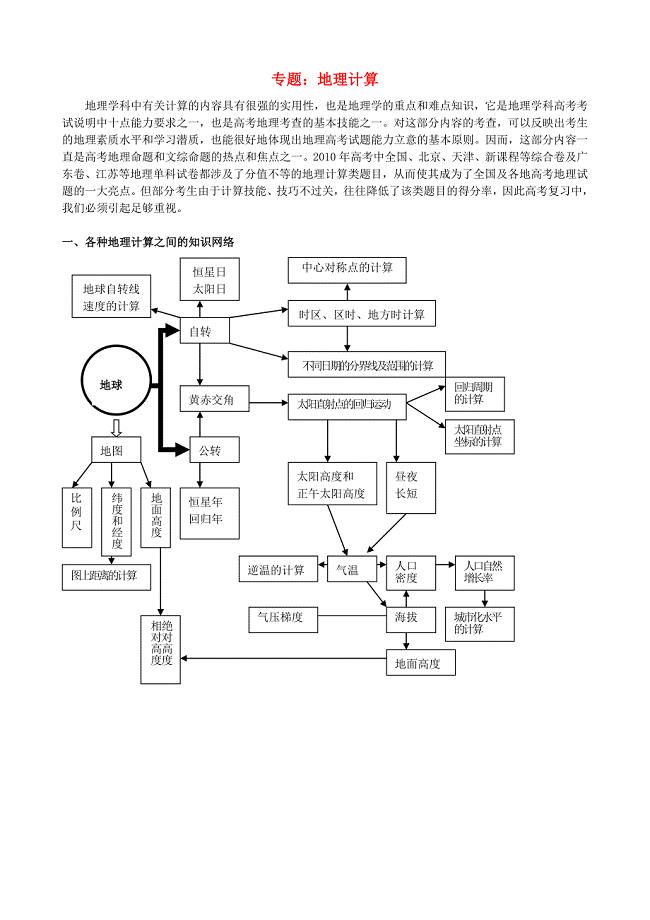

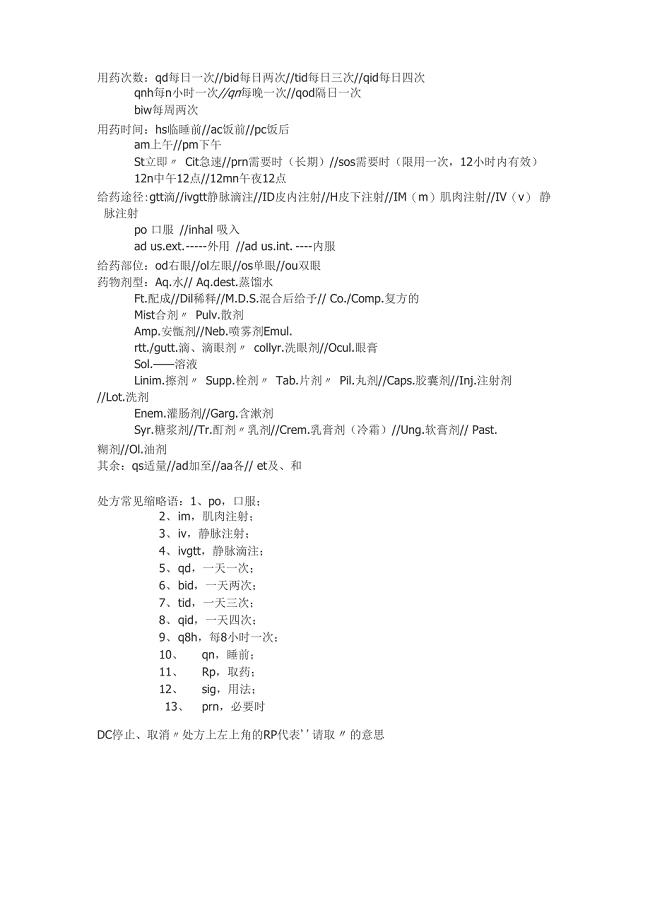

13页1、真诚为您提供优质参考资料,若有不当之处,请指正。电流测试1 电流测试简介 功能测试是基于逻辑电平的故障检测,逻辑电平值通过测量原始输出的电压来确定,因此功能测试实际上是电压测试。电压测试对于检测固定型故障特别是双极型工艺中的固定型故障是有效的,但对于检测CMOS 工艺中的其他类型故障则显得有些不足,而这些故障类型在CMOS 电路测试中是常见的对于较大电路,电压测试由于测试图形的生成相当复杂且较长,因而电流测试方法被提出来电流测试的测试集相当短,这种测试方式对于固定型故障也有效。 CMOS 电路具有低功耗的优点,静态条件下由泄漏电流引起的功耗可以忽略,仅在转换期间电路从电源消耗较大的电流。电源电压用VDD表示,Q 代表静态(quiescent) ,则IDDQ 可用来表示MOS电路静态时从电源获取的电流,对此电流的测试称为IDDQ 测试,这是一种应用前景广泛的测试。 IDDQ 测试概念的提出时间并不很长,但自半导体器件问世以来,基于电流的测量一直是测试元器件的一种方法,这种方法即所谓的IDDQ 测试,用在常见的短接故障检测中。自从Wanlsaa 于1961 年提出CMOS 概念, 1968

2、 年RCA 制造出第一块CMOS IC 和1974 年制造出第一块MOS 微处理器以来,科研人员一直研究CMOS 电路的测试,而静态电流测试则作为一项主要的参数测量1975 年Nelson 提出了IDDQ 测试的概念和报告,1981 年M.W Levi 首次发表了关于VLSI CMOS 的测试论文,这就是IDDQ 测试研究的开端。其后,IDDQ 测试用来检测分析各种DM0S 缺陷,包括桥接故障和固定型故障1988 年W.Maly 首次发表了关于电流测试的论文, Levi, Malaiya, C.Crapuchettes, M.Patyra , A .Welbers 和S.Roy 等也率先进行了片内电流测试的研究开发工作,这些研究奠定了IDDQ 测试的基础、1981 年Philips semiconductor 开始在SRAM 产品测试中采用片内IDDQ 检测单元,其后许多公司把片内IDDQ 检测单元用在ASIC产品中,但早期的IDDQ 测试基本上只为政府、军工资助的部门或项目所应用。 直到20 世纪80 年代后期,半导体厂商认识到IDDQ 测试是检测芯片物理缺陷的有效方法,IDDQ 测

3、试才被普遍应用, CAD 工具也开始集成此项功能。目前,IDDQ 测试也逐渐与其他DFT结构,例如扫描路径测试、内建自测试、存储器测试等,结合在一起应用。20 世纪80 年代,电流测量基本上是基于片外测量电路的,80 年代末片上电流传感器的理论和设计方法得以提出,随后这方面所开展的理论和方法研究纷纷出现,IEEE Technical Committee on Test Technology 于1994 年成立一个称做QTAG ( Quality Test Action Group ) 的技术组织,其任务是研究片上电流传感器的标准化问题,但该组织得出了电流传感器不经济的结论,因此,1996 年结束标准化研究工作,目前电流传感器的研究主要针对高速片外传感器。 IDDQ 测试是源于物理缺陷的测试,也是可靠性测试的一部分1996 年SRC (Semiconductor Research Corporation )认定IDDQ 测试是20 世纪90 年代到21 世纪主要的测试方法之一。IDDQ 测试已成为IC 测试和CAD 工具中一个重要内容,许多Verilog/HDL 模拟工具包含IDDQ 测

4、试生成和故障覆盖率分析的功能。 IDDQ 测试引起重视主要是测试成本非常低和能从根本上找出电路的问题(缺陷)所在。例如,在电压测试中,要把测试覆盖率从80提高10% ,测试图形一般要增加一倍,而要从95 每提高一个百分点,测试图形大约要在前面的基础上提高一倍,但若在电压测试生成中加入少量的IDDQ 测试图形,就可能达到同样的效果。另外,即使电路功能正常,IDDQ 测试仍可检测出桥接、短路、栅氧短路等物理缺陷。但是IDDQ 测试并不能代替功能测试,一般只作为辅助性测试。IDDQ 测试也有其不足之处,一是前面提到的需要选择合适的测量手段,二是对于深亚微米技术,由于亚阂值元件的增加,静态电流已高得不可区分。 IDDQ 测试的原理就是检测CMOS电路静态时的漏电流,电路正常时静态电流非常小(nA 级),而存在缺陷时(如栅氧短路或金属线短接)静态电流就大得多如果用IDDQ 法测出某一电路的电流超常,则意味着此电路可能存在缺陷。图1 以CMOS 反相器中栅氧短路和金属线桥接形成的电流通道为例,对这一概念进行了进一步阐述对于正常的器件,因制造工艺的改变或测量的不准确,也可能得出IDDQ 电流过大的判

《IDDQ测试原理及方法》由会员新**分享,可在线阅读,更多相关《IDDQ测试原理及方法》请在金锄头文库上搜索。

西北工业大学21秋《电力系统自动装置》平时作业一参考答案6

西北工业大学21秋《电力系统自动装置》平时作业一参考答案6

2023-05-18 14页

东北财经大学22春《工程安全与环境管理》综合作业二答案参考10

东北财经大学22春《工程安全与环境管理》综合作业二答案参考10

2023-08-03 15页

南开大学21春《工程项目管理》在线作业二满分答案33

南开大学21春《工程项目管理》在线作业二满分答案33

2023-02-26 14页

中国质量认证中心(CQC)检查表

中国质量认证中心(CQC)检查表

2022-08-09 13页

2011年湖南省普通高中学业水平考试化学试卷及答案

2011年湖南省普通高中学业水平考试化学试卷及答案

2023-04-27 5页

五年级下册语文第18课教材分析

五年级下册语文第18课教材分析

2023-03-08 5页

大连理工大学21秋《电力电子技术》在线作业二答案参考86

大连理工大学21秋《电力电子技术》在线作业二答案参考86

2023-04-14 13页

中国医科大学21春《药剂学》在线作业二满分答案100

中国医科大学21春《药剂学》在线作业二满分答案100

2022-11-08 13页

独立学院设置与管理办法

独立学院设置与管理办法

2023-10-16 7页

南开大学21春《公司财务》在线作业二满分答案11

南开大学21春《公司财务》在线作业二满分答案11

2023-09-29 17页