VHDL语言与EDA课程设计数字频率计

18页1、湖南人文科技学院课程设计报告课程名称:VHDL语言与EDA课程设计设计题目: 数字频率计 系 别: 通信与控制工程系 专 业: 电子信息工程 班 级: 08级电信二班 学生姓名: 学 号: 起止日期: 11年6月13日 11年6月23日 指导教师: 教研室主任: 3指导教师评语: 指导教师签名: 年 月 日成绩评定项 目权重成绩周杰卢欧1、设计过程中出勤、学习态度等方面0.22、课程设计质量与答辩0.53、设计报告书写及图纸规范程度0.3总 成 绩 教研室审核意见:教研室主任签字: 年 月 日教学系审核意见: 主任签字: 年 月 日摘 要数字频率计是直接用十进制数字来显示被测信号频率的一种测量装置,是计算机,通讯设备、音频设音频视频等科研生产领域不可缺少的测量仪器。本次课程设计设计以EDA工具作为开发手段,运用VHDL语言,将使整个系统大大简化,提高整体的性能和可靠性。EDA(Electronic Design Automation)即电子设计自动化。EDA技术指的是以计算机硬件和系统软件为基本工作平台,以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统设计的主要表达方式,自动完成

2、集成电子系统设计的一门新技术。本设计用VHDL在CPLD器件上实现一种8 位十进制数字频率计测频系统,能够用十进制数码显示被测信号的频率,能够测量正弦波、方波和三角波等信号的频率,具有体积小、可靠性高、功耗低的特点,设计出的频率计能够准确的测出输入信号的频率,最后通过系统仿真,下载、验证和调试运行,实现了一个性能良好的8位数字频率计初步实现了设计目标。其基本原理是使用一个频率稳定性高的频率作为基准,对比测量其他信号的频率,即计算每秒钟内待测信号的脉冲个数。该数字频率计可以在不更改硬件电路的基础上,对系统进行各种改进还可以进一步提高系统的性能,而且整个系统非常精简,具有高速、精确、可靠、抗干扰性强和现场可编程等优点,实用性极高。本文详细描述了数字频率计的设计流程及正确实现。关键词:数字频率计;EDA;VHDL;Quartus目 录设计要求11、方案论证与对比11.1方案对比11.2方案选择22.总体模块设计23.单元模块设计33.1 顶层模块设计33.2 测频控制模块43.3十进位计数模块53.4 测频锁存模块74.系统仿真85.硬件下载测试96.总结与致谢10参考文献11附录12数字频

3、率计 设计要求1能够显示的频率为8位10进制;2测量的波形的电压最大值小于5V;3能测量正弦波、三角波、方波或其他周期性波形的频率;3用数码管显示测试的结果。 1、方案论证与对比1.1方案对比方案一:使用ATMEL公司的AT89C51实现一基于单片机的设计,用单片机定时器和计数器来实现对频率的测量,直接用十进制数字显示被测信号频率的一种测量装置。它以用测量频率的方法对TTL方波频率进行自动测量,使用该单片作为控制器件使被测频率信号通过信号处理电路,闸门时间与被测信号与非处理,产生信号脉冲,经过分频电路,然后送入单片机进行运算和处理,单片机将处理的数据通过显示器显示。其方案方案设计框图如图1所示: 整形电路计数器寄存器显示器同步检测自动换挡量程选择分频器时钟 图1 整体方案设计图方案二:基于EDA技术和VHDL语言为程序设计语言在器件上实现数字频率计测频系统,其基本原理是使用一个频率稳定性高的频率作为基准,对比测量其他信号的频率,即计算每秒钟内待测信号的脉冲个数。该数字频率计可以在不更改硬件电路的基础上,对系统进行各种改进还可以进一步提高系统的性能,然后用8位十进制数码显示被测信号的频率

《VHDL语言与EDA课程设计数字频率计》由会员博****1分享,可在线阅读,更多相关《VHDL语言与EDA课程设计数字频率计》请在金锄头文库上搜索。

公司员工规章制度有哪些

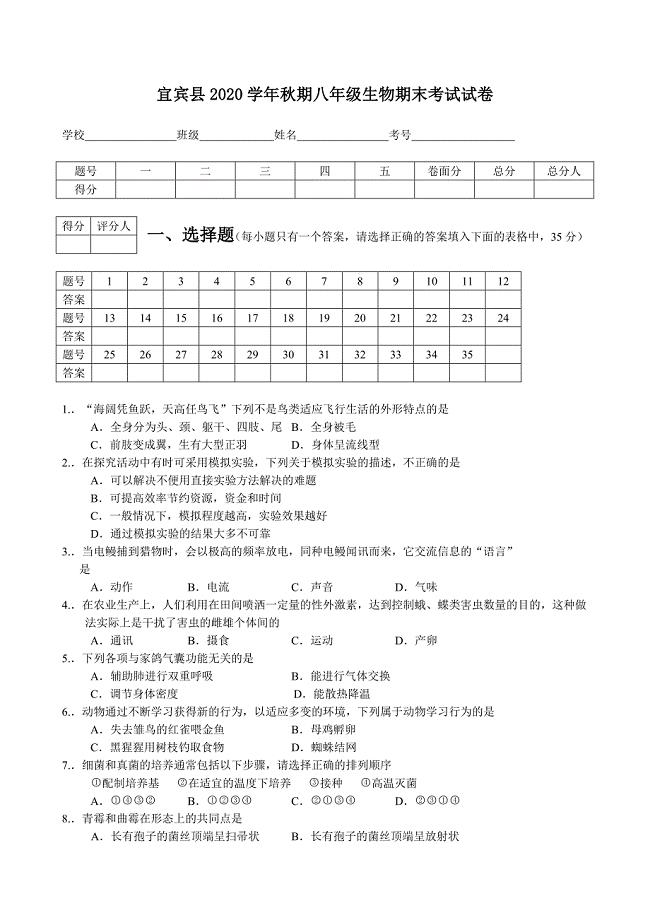

四川省宜宾县期八年级生物期末考试试卷

计算机硬件专业个人求职信范文.doc

食品安全工作总结范文县食品药品监督管理局食品安全工作总结

班主任年度考核总结归纳

2023年二年级小学数学复习计划书

苏教版六年级下册数学正比例反比例单元测试(含答案)

企业业务合作协议模板

区工信局2022年度社会评价意见整改结果总结

医院保安工作总结.doc

年产60万只洁具生产项目可行性研究报告

个人宅基地转让协议书

位育初级中学 宗岱 个人年度考核登记表

2023年8月农技指导员工作总结范文(2篇).doc

六级数学圆锥的体积计算教案设计

全国物流园区运营分析报告报告材料

春天来了周记15篇

河南关于成立电池公司可行性研究报告(DOC 87页)

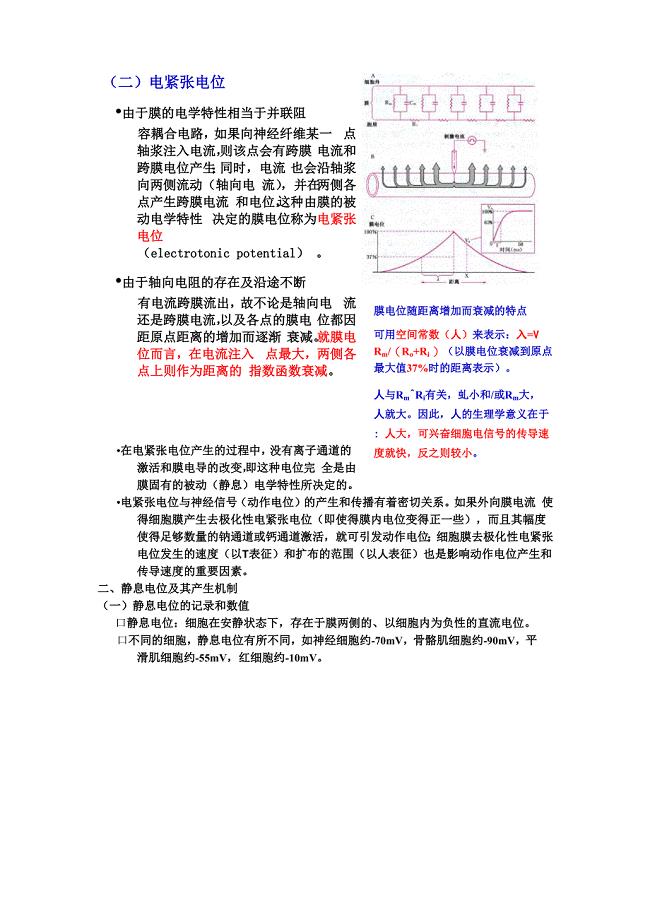

在电紧张电位产生的过程中

折纸夏天的知了

家长会家长的心得体会

家长会家长的心得体会

2023-03-14 33页

2022年婚庆司仪主持词范文七篇

2022年婚庆司仪主持词范文七篇

2022-09-19 37页

实用的说课稿模板合集8篇

实用的说课稿模板合集8篇

2022-09-11 47页

2003年经济师初级经济基础试题及答案

2003年经济师初级经济基础试题及答案

2023-05-15 22页

斜拉桥-桥梁说明典尚设计

斜拉桥-桥梁说明典尚设计

2022-09-01 5页

2022年教师个人工作计划汇总4篇

2022年教师个人工作计划汇总4篇

2024-02-09 15页

保安年终工作总结15篇

保安年终工作总结15篇

2023-06-04 43页

2022企业文化演讲稿合集6篇

2022企业文化演讲稿合集6篇

2023-09-28 18页

证券实习报告5篇

证券实习报告5篇

2023-08-15 29页

健康工作计划3篇【新版】

健康工作计划3篇【新版】

2022-08-19 14页