数电 第四章 组合逻辑电路

83页1、第四章 组合逻辑电路 4.1 概述 一、组合逻辑电路的特点 从功能上 从电路结构上 任意时刻任意时刻的输出仅的输出仅 取决于该时刻的输取决于该时刻的输 入入 不含记忆(存储不含记忆(存储 )元件)元件 二、逻辑功能的描述 组合逻辑 电路 组合逻辑电路的框图 逻辑图 逻辑表 达式 1 最简与或 表达式 化简 2 从输入到输出 逐级写出 4.2.1 组合逻辑电路的分析方法 最简与或 表达式 3 真值表 4 电路的逻 辑功能 分析图所示电路的逻辑功能,指出该电路的用途。 解:逻辑式 一、逻辑抽象 分析因果关系,确定输入/输出变量 定义逻辑状态的含意(赋值) 列出真值表 二、写出函数式 三、选定器件类型 四、根据所选器件:对逻辑式化简(用门) 五、画出逻辑电路图 六、工艺设计 4.2.2 组合逻辑电路的设计方法 设计举例: 设计一个监视交通信号灯状态的逻辑电路 如果信号灯 出现故障, Z为1 R A G Z 1. 抽象 输入变量: 红(R)、黄(A)、绿(G) 亮为1,不亮为0 输出变量: 故障信号(Z) 故障为1,正常为0 2. 写出逻辑表达式 输输入变变 量 输输 出 R AG Z 000

2、1 0010 0100 0111 1000 1011 1101 1111 3. 选用小规模SSI器件 4. 化简 5. 画出逻辑图 4.3 若干常用组合逻辑电路 编码器,译码器,数据选择器,加法器,数值比较器 4.3.1 编码器 编码:将输入的每个高/低电平信号变成 一个对应的二进制代码 普通编码器 优先编码器 一、普通编码器 特点:任何时刻 只允许输入一个 编码信号。 例:3位二进制 普通编码器 输输 入输输 出 I0I1I2I3I4I5I6I7Y 2 Y 1 Y 0 10000000000 01000000001 00100000010 00010000011 00001000100 00000100101 00000010110 00000001111 利用无关项化简, 输输 入输输 出 I0I1I2I3I 4 I5I6I7Y 2 Y 1 Y 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0

3、0 1 0 0 1 0 1 0 0 0 0 0 0 1 0 1 1 0 0 0 0 0 0 0 0 1 1 1 1 二、优先编码器 特点:允许同时 输入两个以上的 编码信号,但只 对其中优先权最 高的一个进行编 码。 例:8线-3线优 先编码器 (设I7优先权最 高I0优先权最 低) 输 入输 出 I0I1I2I3I4I5I6I7Y2Y1Y0 XXXXXXX1111 XXXXXX10110 XXXXX100101 XXXX1000100 XXX10000011 XX100000010 X1000000001 10000000000 低电 平 实例: 74HC148 选通输出端 扩展输出端 选通输 入端 选 通 信 号 选通信号 附 加 输 出 信 号 为0时,电路工作 无编码输入 为0时,电路工作 有编码输入 输 入输 出 1XXXXXXXX11111 01111111111101 0XXXXXXX000010 0XXXXXX0100110 0XXXXX01101010 0XXXX011101110 0XXX0111110010 0XX01111110110 0X01111111101

4、0 00111111111110 不可能出现00 工作,且有输入01 工作,但无输入10 不工作 11 状态 附加输出信号的状态及含意 S YEX YS 控制端扩展功能举例: 例:用两片8线-3线优先编码器 16线-4线优先编码器 其中, 的优先权最高 状态 11 不工作 01 工作,但无输输入 10 工作,且有输输入 00 不可能出现现 第一片为高优先权 只有(1)无编码输入时,(2)才允许工作 第(1)片 时表示对 的编码 低3位输出应是两片的输出的? 三、二-十进制优先编码器 将 编成0110 1110 的优先权最高, 最低 输入的低电平信号变成一个对应的十进制 的编码 4.3.2 译码器 译码:将每个输入的二进制代码译成对应的输出高、低 电平信号。 常用的有:二进制译码器,二-十进制译码器,显示译码 器等 一、二进制译码器 例:3线8线译码器 输 入输 出 A2A1A0Y7Y6Y5Y4Y3Y2Y1Y0 00000000001 00100000010 01000000100 01100001000 10000010000 10100100000 11001000000 11110

《数电 第四章 组合逻辑电路》由会员我**分享,可在线阅读,更多相关《数电 第四章 组合逻辑电路》请在金锄头文库上搜索。

高三世界地理专题复习总论4天气与气候汇编

云南大学分析化学第五章 酸碱滴定

南京大学 刘金源教授多元新史观与世界史教学

南大门之不夜城

海南大学 食品分析七 2014

东南大学功放电路和直流电源(第29讲)2014

步步高·2015高三物理总复习(江苏专用)【配套课件】:第4章 曲线运动万有引力与航天 第1课时 曲线运动.

必修2:4.1曲线运动 运动的合成与分解【2015《物理复习方略》一轮复习课件沪科版】.

济南大学电工习题答案.

金版学案13-14物理(人教版)选修3-2课件:5.3电感和电容对交变电流的影响.

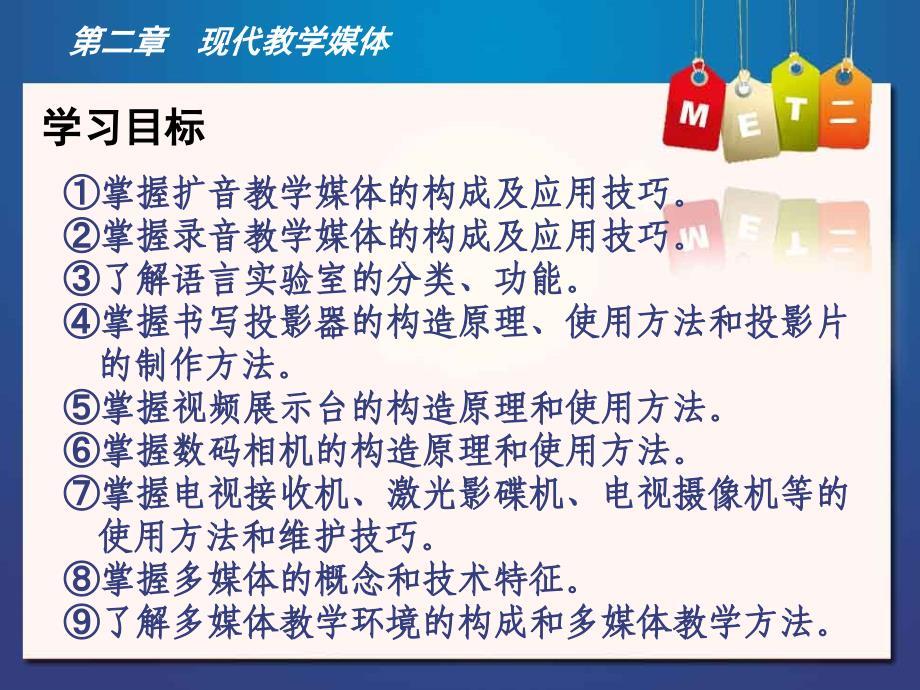

现代教学媒体.

教案4(火警报警系统).

湖南大学-物理 课程指导八.

语s版六年级下册语文百花园四课件剖析

世纪金榜2018版复习方略物理课件31.

人教新课标二年级语文下册《我不是最弱小的_5》PPT课件.

楼宇自动化 课件 教学PPT 作者 傅海军 第5章.

暨南大学-管理学-第11章-控制.

海南大学 食品分析十二 2014.

北师大八年级数学下册-第2课时-分式的基本性质.

应对行业变革挑战策略

应对行业变革挑战策略

2024-04-11 25页

应对经济环境变化的策略布局(资料)

应对经济环境变化的策略布局(资料)

2024-04-11 37页

并购重组项目总结与反思

并购重组项目总结与反思

2024-04-11 28页

年度财务审计报告解读(资料)

年度财务审计报告解读(资料)

2024-04-11 31页

年度品牌影响力报告(资料)

年度品牌影响力报告(资料)

2024-04-11 36页

市场趋势分析与预测会议

市场趋势分析与预测会议

2024-04-11 29页

市场调研报告及趋势预测(资料)

市场调研报告及趋势预测(资料)

2024-04-11 22页

市场调研中的伦理与法律问题

市场调研中的伦理与法律问题

2024-04-11 27页

市场营销趋势与消费者行为分析会议

市场营销趋势与消费者行为分析会议

2024-04-11 34页

市场营销扩大商业影响力

市场营销扩大商业影响力

2024-04-11 32页