通信的 SPI 概念

6页1、二、通信的SPI概念21、SPI:高速同步串行口SPI :高速同步串行口。是一种标准的四线同步双向串行总线。SPI,是英语Serial Peripheral in terface 的缩写,顾名思义就是串 行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。 SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信 号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通 信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为 PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越 来越多的芯片集成了这种通信协议,比如 AT91RM9200.SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备 以串行方式进行通信以交换信息。外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的 多种标准外围器件直接接口,该接口一般使用 4条线:串行时钟线(SCK)、 主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平 有效

2、的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接 口芯片没有主机输出/从机输入数据线MOSI)。SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设 备和一个或多个从设备,需要至少 4根线,事实上3根也可以(用于单向 传输时,也就是半双工方式)。也是所有基于 SPI的设备共有的,它们是 SDI (数据输入),SDO (数据输出),SCK (时钟),CS (片选)。(1)SDO -主设备数据输出,从设备数据输入(2)SDI -主设备数据输入,从设备数据输出(3)SCLK -时钟信号,由主设备产生(4)CS -从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定 的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在 同一总线上连接多个SPI设备成为可能。接下来就负责通讯的3根线了。通讯是通过数据交换完成的,这里先 要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是 SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完 成数据传输。数据输出通过 SDO线,数据在时钟上升沿

3、或下降沿时改变, 在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样 原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以 完成8位数据的传输。要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。同 样,在一个基于SPI的设备中,至少有一个主控设备。这样传输的特点: 这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一 次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂 停,因为SCK时钟线由主控设备控制,当没有时钟跳变时,从设备不采集 或传送数据。也就是说,主设备通过对 SCK时钟线的控制可以完成对通讯 的控制。SPI还是一个数据交换协议:因为SPI的数据输入和输出线独立, 所以允许同时完成数据的输入和输出。不同的SPI设备的实现方式不尽相同,主要是数据改变和采集的时间不同,在时钟信号上沿或下沿采集有不 同定义,具体请参考相关器件的文档。在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信, 显得简单高效。在多个从设备的系统中,每个从设备需要独立的使能信号, 硬件上比I2C系统要稍微复杂一些。22、接口包括以下

4、四种信号:(1) MOSI -主器件数据输出,从器件数据输入(2) MISO -主器件数据输入,从器件数据输出(3) SCLK -时钟信号,由主器件产生(4) /SS -从器件使能信号,由主器件控制在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显 得简单高效。23、接口的硬件连接示意图在多个从器件的系统中,每个从器件需要独立的使能信号,硬件上比 I2C系统要稍微复杂一些。SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8 位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低 位在后。如下图所示,在SCLK的下降沿上数据改变,同时一位数据被存入移位寄存器。24、性能特点AT91RM9200的SPI接口主要由4个引脚构成:SPICLK、MOSI、MISO及 /SS,其中SPICLK是整个SPI总线的公用时钟,MOSI、MISO作为主机,从 机的输入输出的标志,MOSI是主机的输出,从机的输入,MISO是主机的输 入,从机的输出。/SS是从机的标志管脚,在互相通信的两个 SPI总线的器 件,/SS管脚的电平低的是从机,相反/SS管脚的电平高的是

《通信的 SPI 概念》由会员鲁**分享,可在线阅读,更多相关《通信的 SPI 概念》请在金锄头文库上搜索。

重庆某水库导流洞施工组织设计

大连理工大学21春《ACAD船舶工程应用》离线作业2参考答案89

公司员工安全协议书

高中数学教学中应用体验式教学的价值优秀获奖科研论文

九年级物理第一学期期终考试质量分析

人事行政的工作总结报告(2篇).doc

借款抵押合同书样本(14篇)

散客行李寄存处理程序精

小学优秀家长会发言稿

防屈曲消能支撑

2023年后勤工作计划3篇

管理培训生培养项目计划书

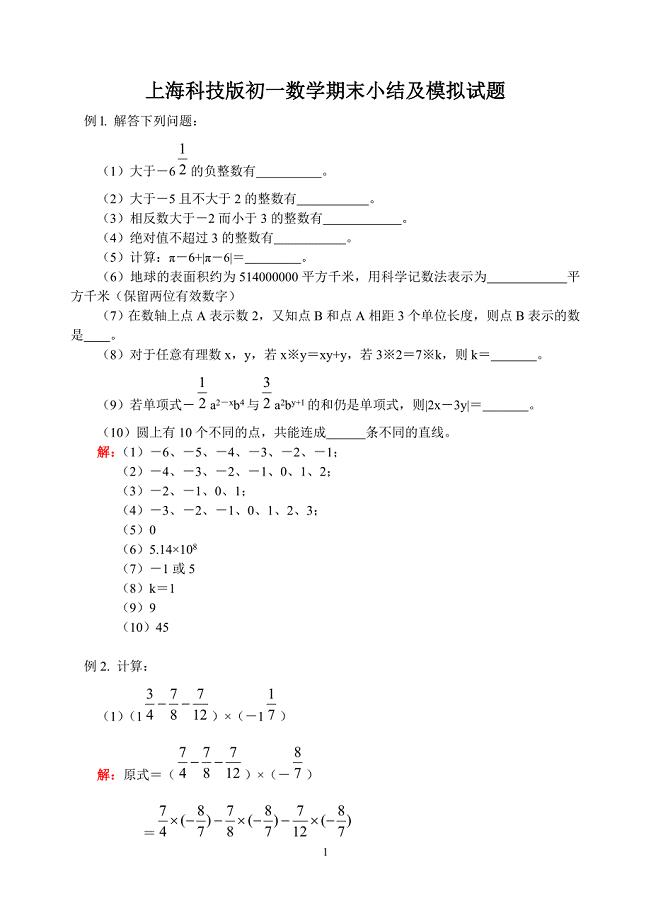

上海科技版初一数学期末小结及模拟试题

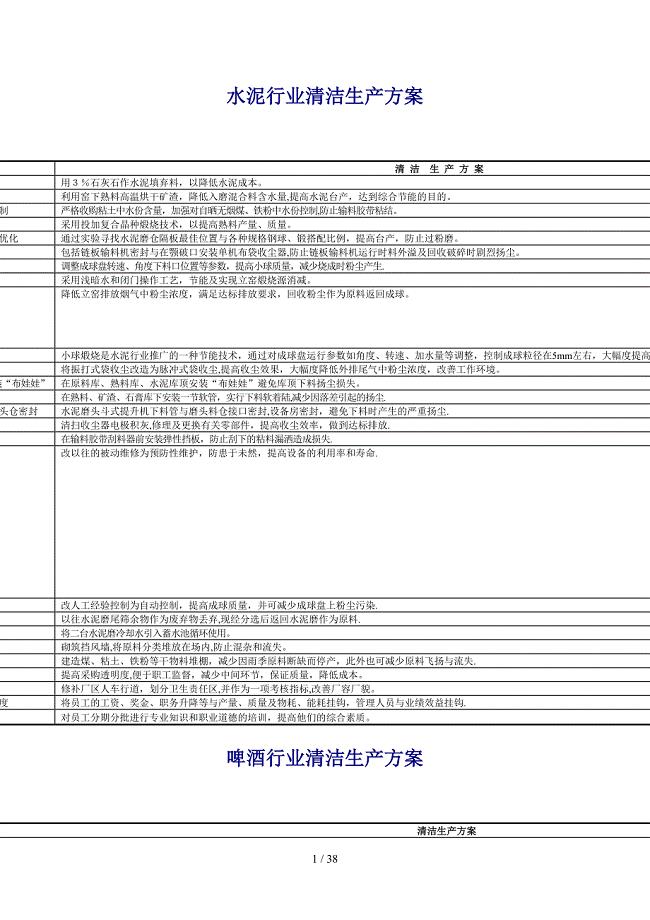

水泥行业清洁生产方案

质控办对临床科室月考核评分表

土木工程施工课程设计

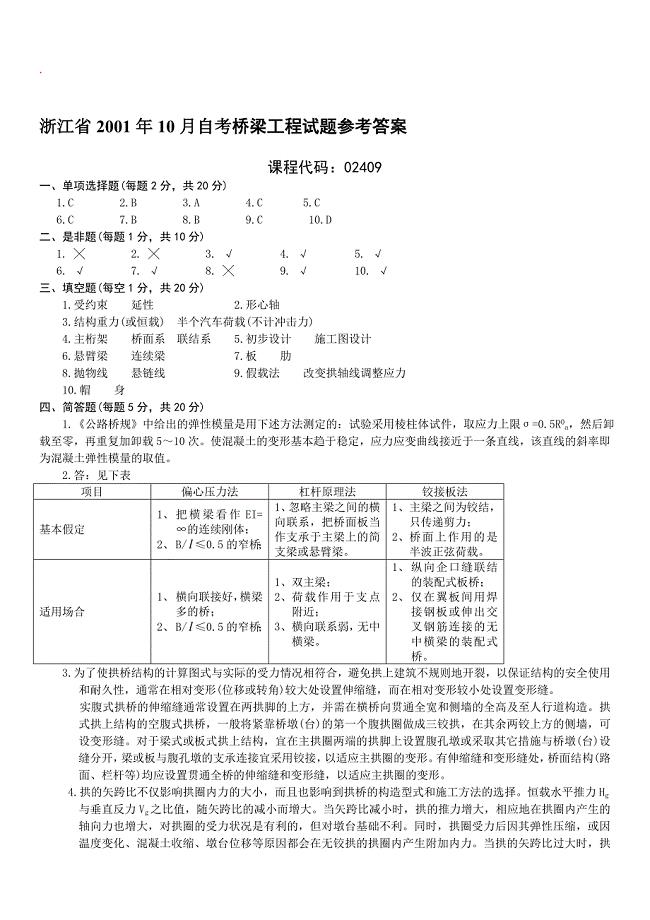

桥梁工程自考试题1

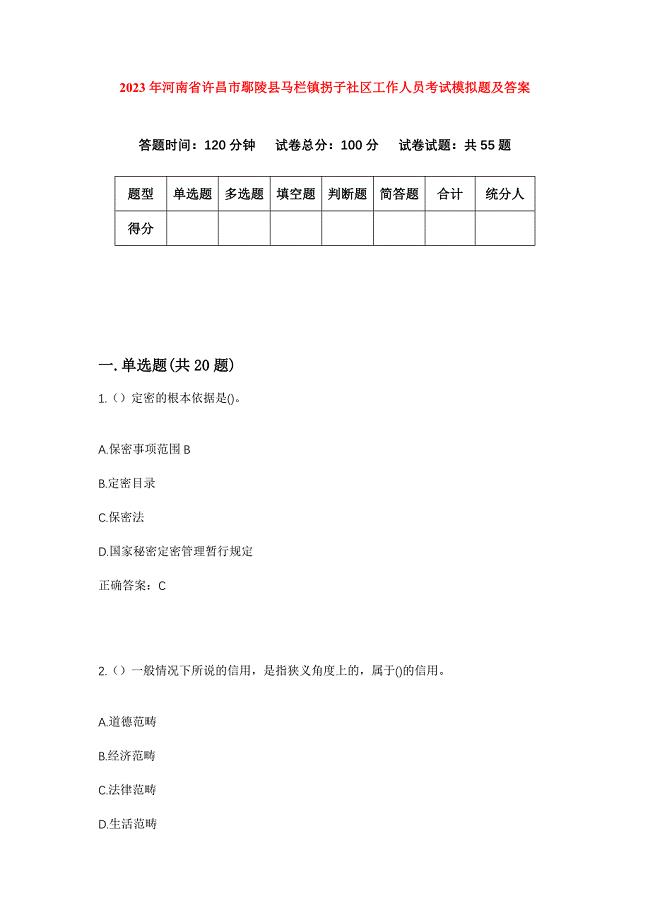

2023年河南省许昌市鄢陵县马栏镇拐子社区工作人员考试模拟题及答案

2023年有关个人授权委托书模板锦集七篇

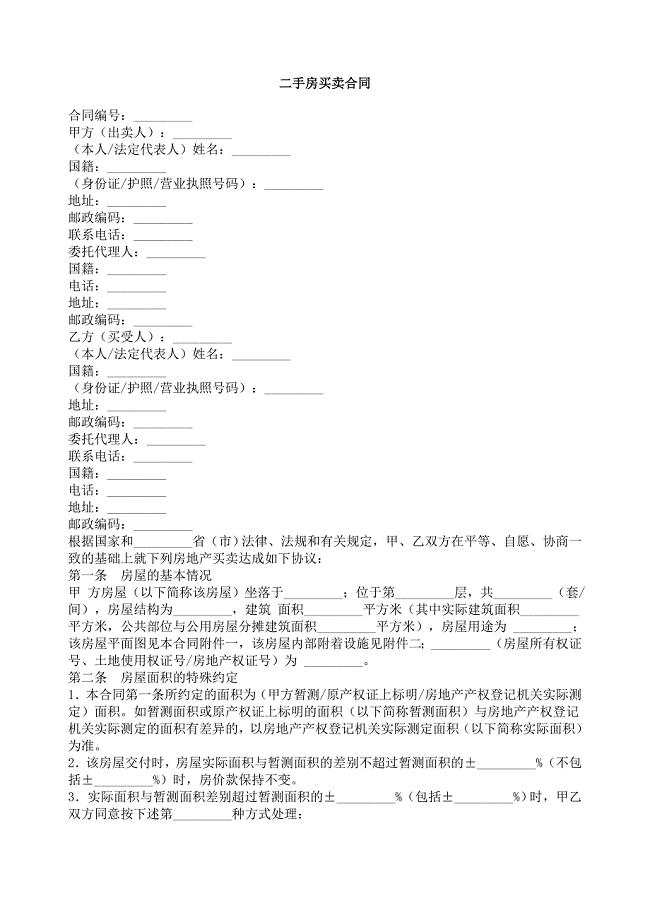

二手房买卖合同02

十大传统习俗

十大传统习俗

2023-02-21 3页

八年制多器官衰竭讲义0704

八年制多器官衰竭讲义0704

2023-09-30 7页

天衡技术检验报告

天衡技术检验报告

2023-09-23 2页

公司员工晋升报告书

公司员工晋升报告书

2023-05-05 4页

分析方法的选择

分析方法的选择

2022-08-19 5页

漳州职业学院办学质量报告

漳州职业学院办学质量报告

2022-12-04 52页

科学技术档案案卷构成的一般要求1

科学技术档案案卷构成的一般要求1

2023-05-30 10页

混凝土强度的评定的方法

混凝土强度的评定的方法

2023-09-22 1页

矿井防治水管理制度

矿井防治水管理制度

2023-05-18 17页

对境外PEVC的影响与分析

对境外PEVC的影响与分析

2024-01-23 6页