北邮电子院专业实验报告材料

47页1、word电子工程学院ASIC专业实验报告班级:某某: 学号:班内序号:第一局部 语言级仿真LAB 1:简单的组合逻辑设计一、 实验目的掌握根本组合逻辑电路的实现方法。二、 实验原理本实验中描述的是一个可综合的二选一开关,它的功能是当sel = 0时,给出out = a,否如此给出结果out = b。在Verilog HDL中,描述组合逻辑时常使用assign结构。equal=(a=b)?1:0是一种在组合逻辑实现分支判断时常用的格式。parameter定义的size参数决定位宽。测试模块用于检测模块设计的是否正确,它给出模块的输入信号,观察模块的内部信号和输出信号。三、 源代码module scale_mux(out,sel,b,a);parameter size=1;outputsize-1:0 out;inputsize-1:0b,a;input sel;assign out = (!sel)?a: (sel)?b: size1bx;endmoduledefine width 8timescale 1 ns/1 nsmodule mux_test; regwidth:1a,b; w

2、irewidth:1out; reg sel; scale_mux#(width)m1(.out(out),.sel(sel),.b(b),.a(a); initial begin $monitor($stime,sel=%b a=%b b=%b out=%b,sel,a,b,out); $dumpvars(2,mux_test); sel=0;b=width1b0;a=width1b1; #5sel=0;b=width1b1;a=width1b0; #5sel=1;b=width1b0;a=width1b1; #5sel=1;b=width1b1;a=width1b0; #5 $finish; endendmodule四、 仿真结果与波形LAB 2:简单时序逻辑电路的设计一、 实验目的掌握根本时序逻辑电路的实现。二、 实验原理在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综合的Verilog HDL模型中,我们常使用always块和(posedge clk)或(negedge clk)的结构来表述时序逻辑。在always块中,被赋值的信号都必须定

3、义为reg型,这是由时序逻辑电路的特点所决定的对于reg型数据,如果未对它进展赋值,仿真工具会认为它是不定态。为了正确地观察到仿真结果,在可综合的模块中我们通常定义一个复位信号rst-,当它为低电平时对电路中的存放器进展复位。三、 源代码timescale 1 ns/100 psmodule counter(t,clk,data,rst_,load);output4:0t ;input 4:0data;input clk;input rst_;input load;reg 4:0t; always(posedge clk or negedge rst_) if(!rst_) #1.2 t=0; else if(load) t=#3 data; else t=#4 t + 1; endmoduletimescale 1 ns/1 nsmodule counter_test; wire4:0t; reg 4:0data; reg rst_; reg load; reg clk; counter c1 ( .t (t), .clk (clk), .data(data), .rst_(rst_

《北邮电子院专业实验报告材料》由会员re****.1分享,可在线阅读,更多相关《北邮电子院专业实验报告材料》请在金锄头文库上搜索。

从入门到精通的摄影宝典 学拍唯美风人像

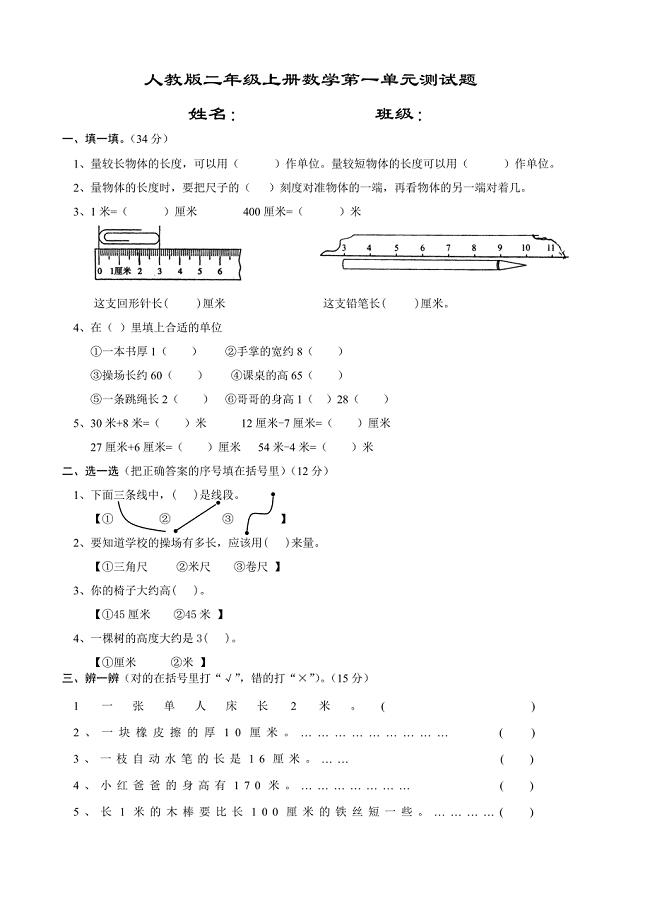

人教版二年级上册数学第一单元测试题

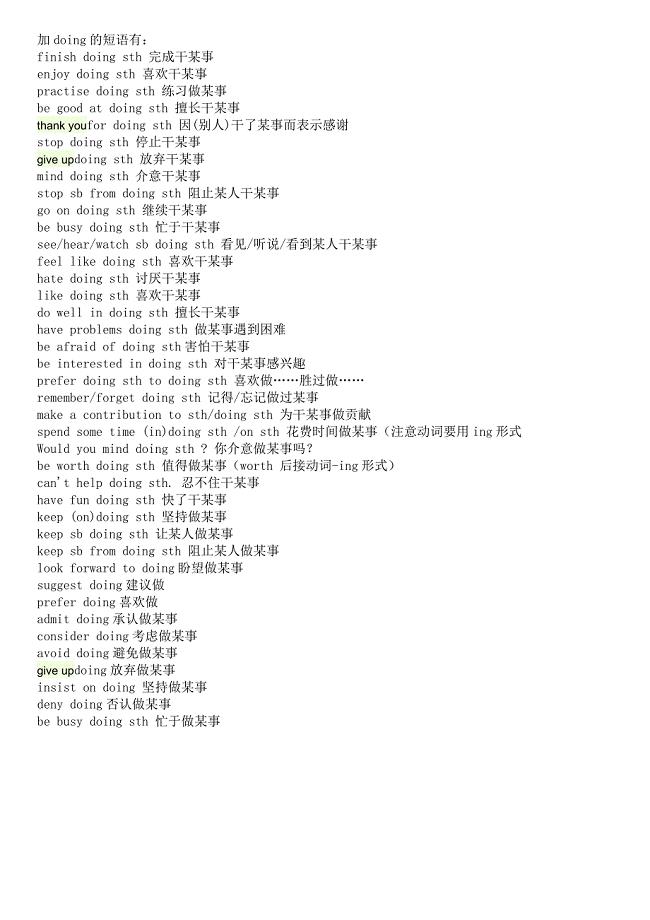

加doing的动词及短语

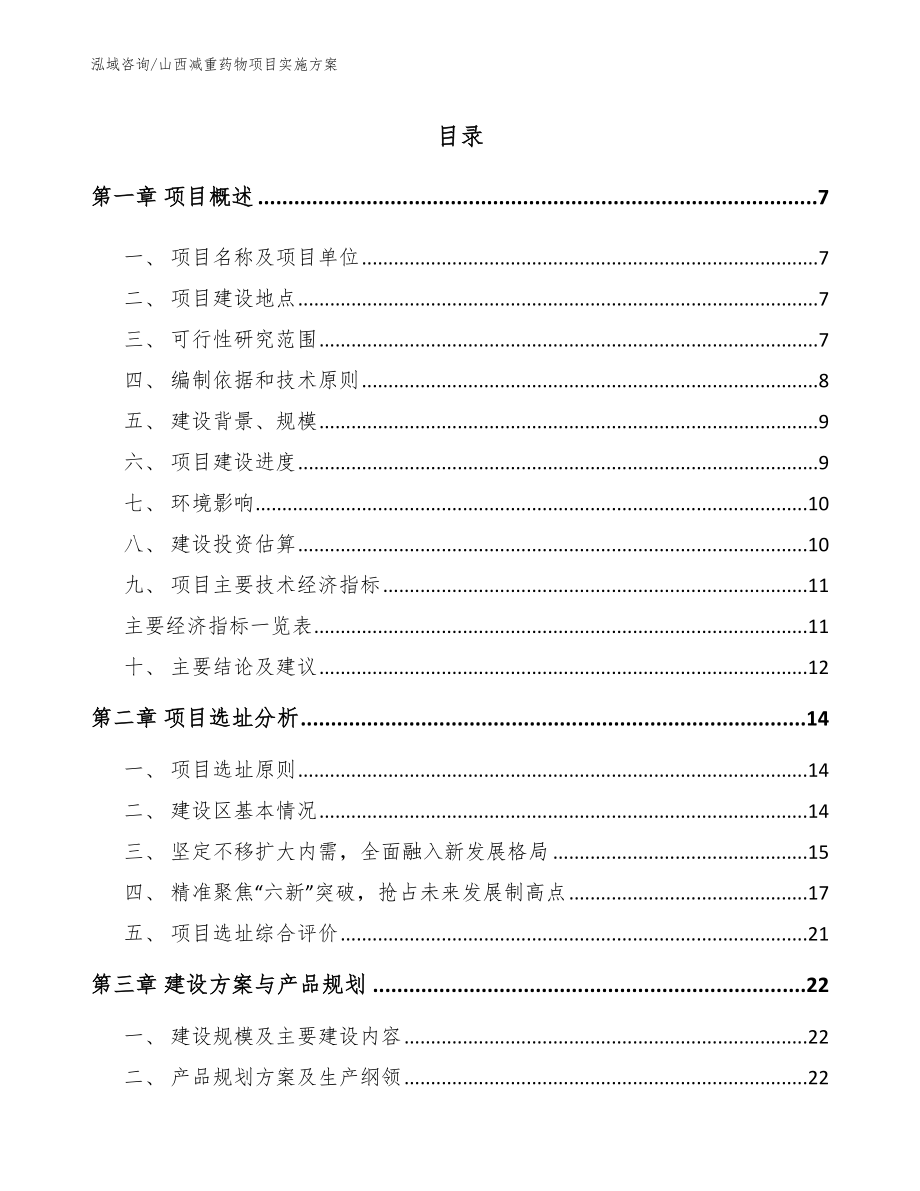

山西减重药物项目实施方案

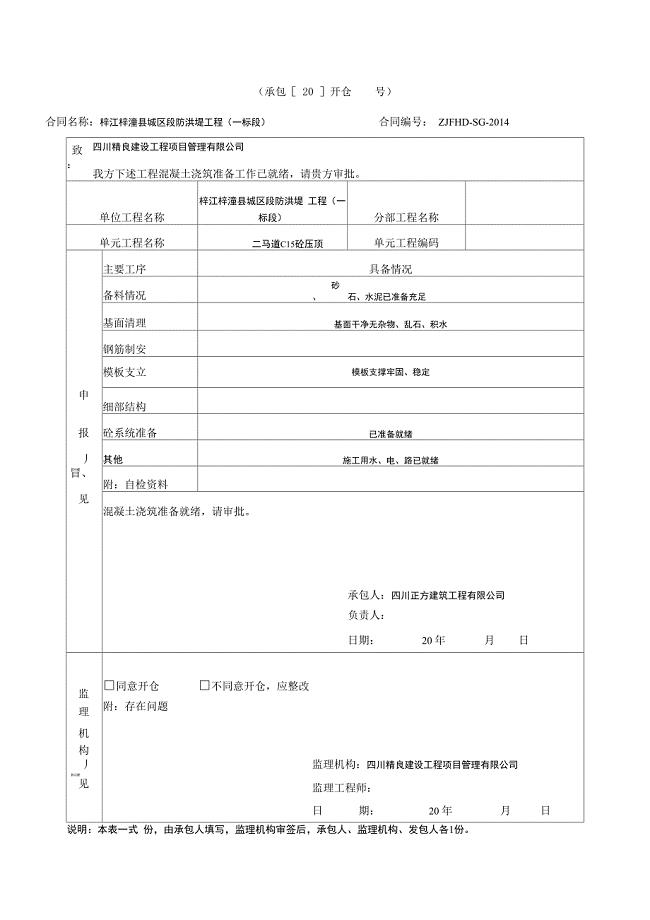

二马道C15砼压顶质检总表空表

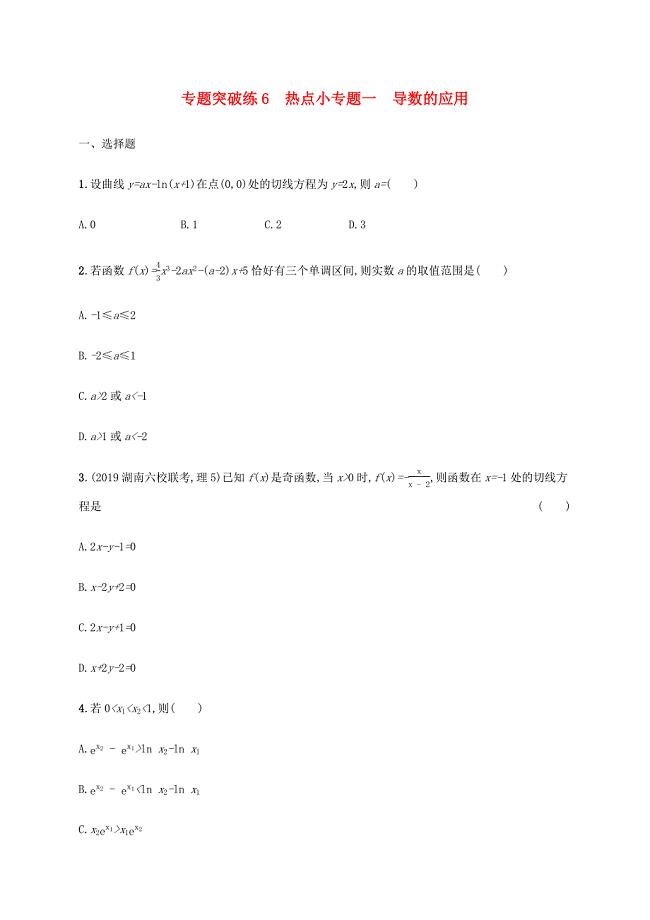

通用版2020版高考数学大二轮复习专题突破练6热点小专题一导数的应用理

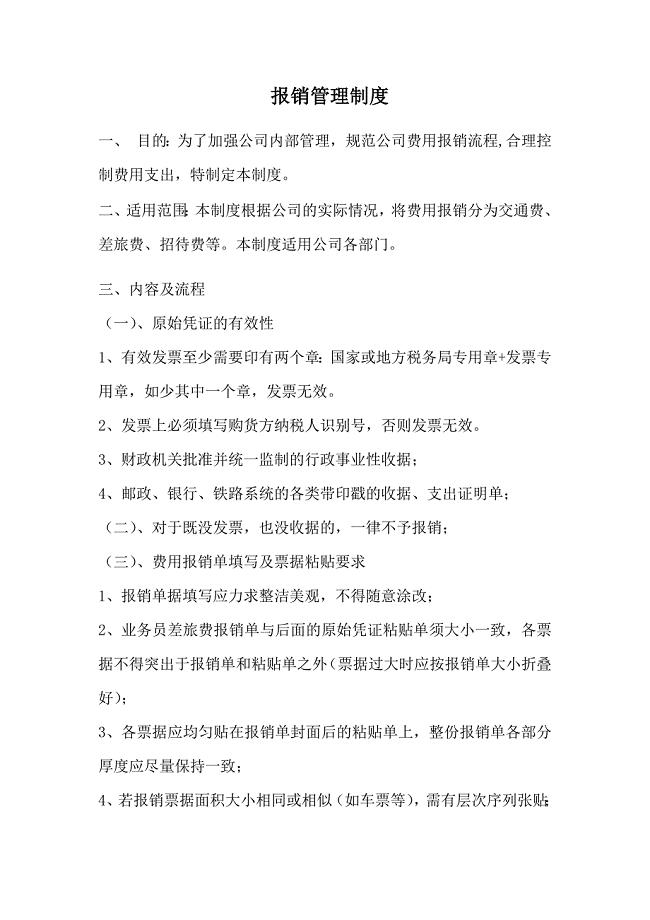

报销管理制度

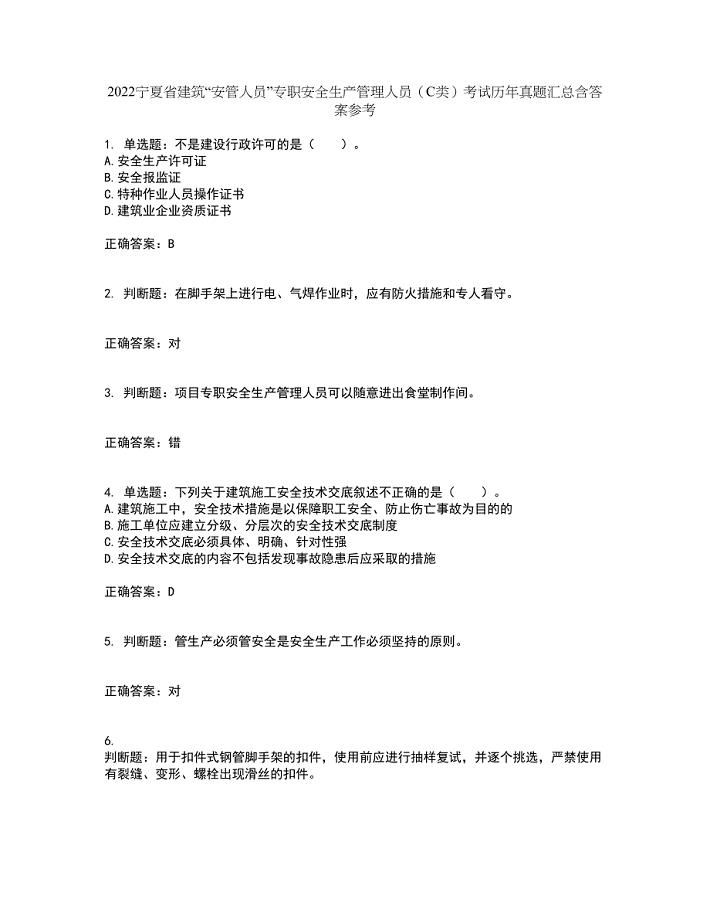

2022宁夏省建筑“安管人员”专职安全生产管理人员(C类)考试历年真题汇总含答案参考51

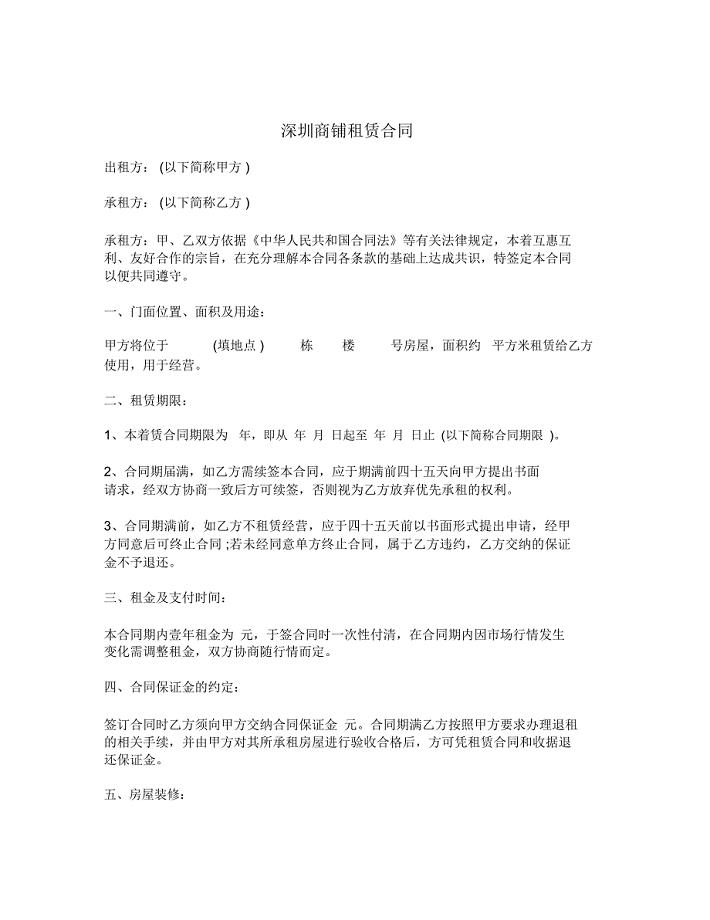

深圳商铺租赁合同

玉兰油精华露好用吗 大S教你如何挑选精华产品

引起靛颏“喘”的寄生虫

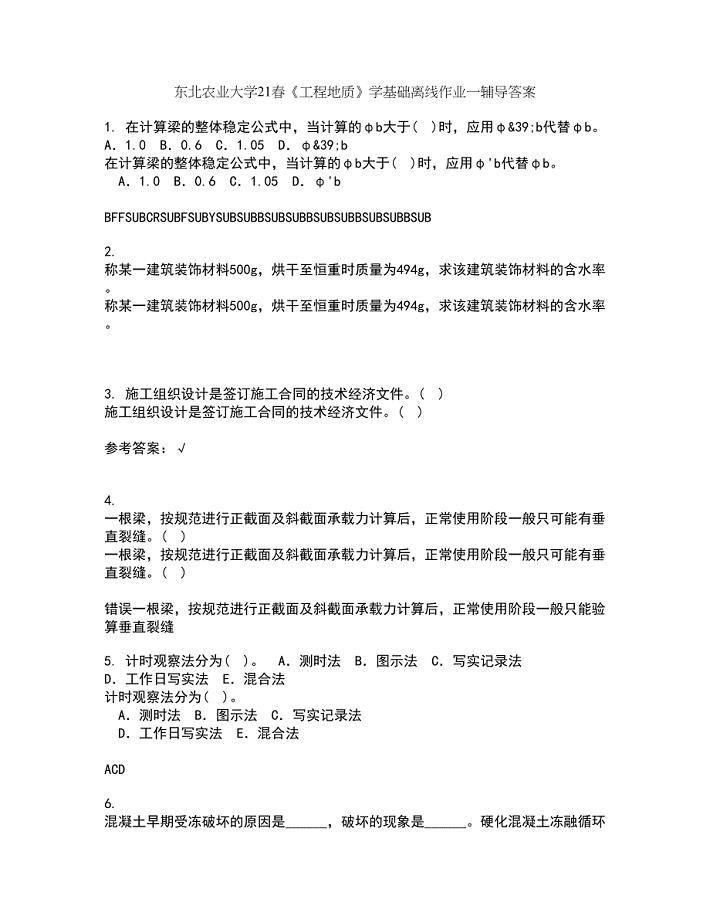

东北农业大学21春《工程地质》学基础离线作业一辅导答案62

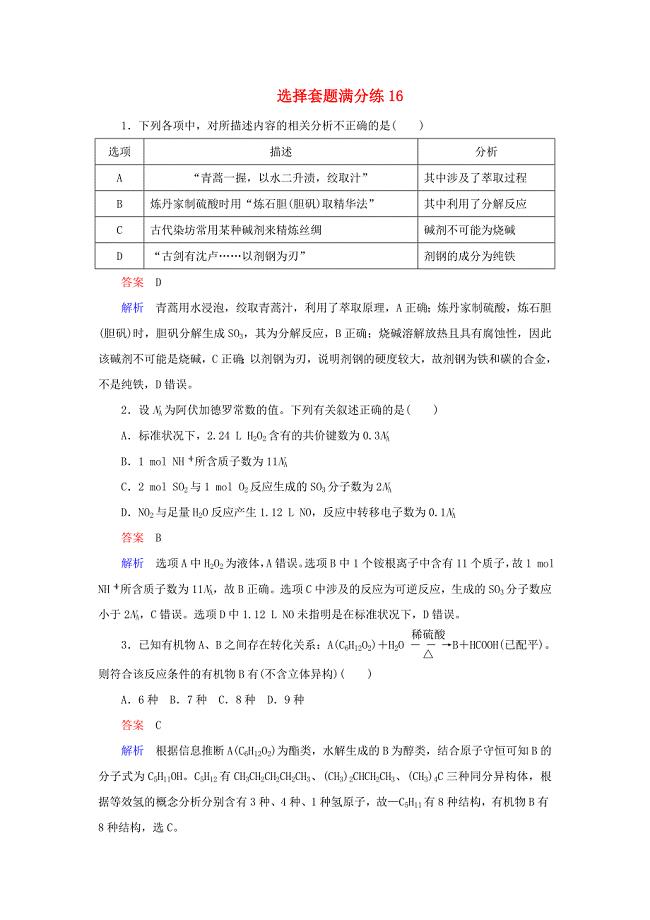

2019高考化学总复习选择套题满分练16

商业门面租赁合同(范本)

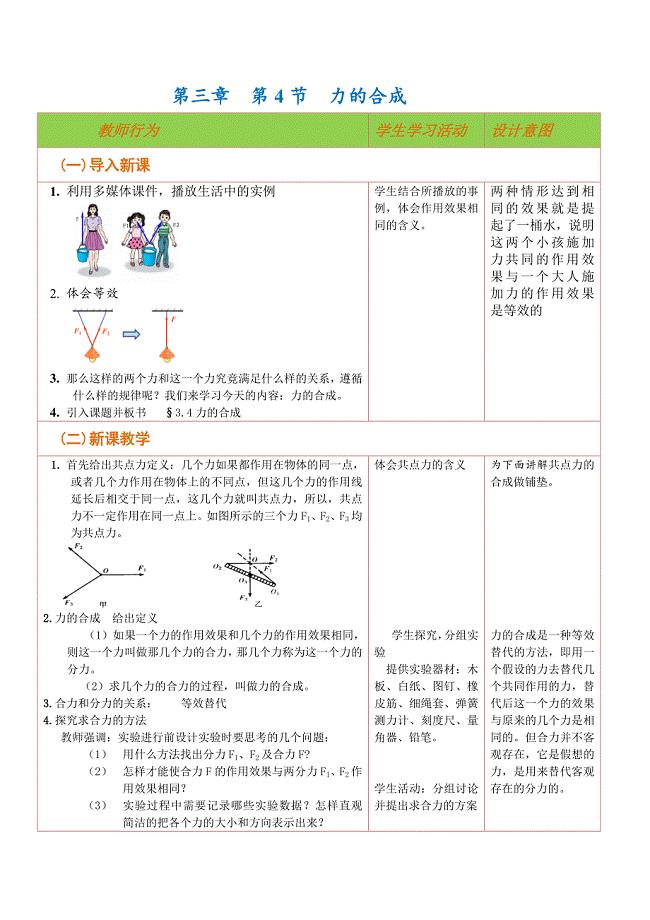

力的合成教学设计

投资现场尽职调查及可行性研究清单

绿色施工及节能减排措施

我国农村学前教育现状的调查同名

函数奇偶性的六类经典题型

初中英语网络研修总结

医院管理整形医院各部门岗位职责

医院管理整形医院各部门岗位职责

2022-10-15 28页

从入门到精通的摄影宝典 学拍唯美风人像

从入门到精通的摄影宝典 学拍唯美风人像

2022-12-20 4页

癫痫的治疗药物专利大全

癫痫的治疗药物专利大全

2023-09-26 20页

固定资产管理系统工作指引

固定资产管理系统工作指引

2022-09-07 11页

初一数学有理数乘除法练习题

初一数学有理数乘除法练习题

2022-09-24 13页

验收备案表(安徽标准格式)(DOC 19页)

验收备案表(安徽标准格式)(DOC 19页)

2023-02-14 19页

13年版测量放线工程专项施工方案1(DOC 16页)

13年版测量放线工程专项施工方案1(DOC 16页)

2023-05-08 17页

课堂观察记录表单(晋小艳)

课堂观察记录表单(晋小艳)

2023-02-16 5页

最新水产品商业计划书5

最新水产品商业计划书5

2023-06-17 8页

北师大小学二年级语文上册期中考试最新

北师大小学二年级语文上册期中考试最新

2022-07-31 5页