VHDL硬件课设.doc

4页1、用VHDL实现数字频率计首先介绍ispDesignExpert的初步使用打开ispDesignExpert,进入主界面,选择file | new project,打开Create New Project窗口,如图:图在保存在选择框选择工程所存的位置,在Project框中输入与VHDL源程序实体名相同的工程名,本例子中输入freq即可,在Project type选择框中选择Schematic/VHDL,完成以上步骤后,点击保存,完成工程的创建。若在以前已经建立了工程则可选择File | Open Project,打开已有工程。在完成工程创建之后,接下来是要为工程建立VHDL文件。这时只需打开Source | new即可打开如图所示对话框图选择VHDL Module,点击OK,出现New VHDL Source对话框,在其中的File Name框中输入与实体名相同的文件名,Entity框中输入实体名,Archetecture框中输入结构体名,在本程序中该三个框分别为:freq、freq、example,点击OK进入文本编辑器,在其中输入VHDL源代码后,保存即可。如果事先已在记事本等文本编

2、辑器中将源代码编辑好则只需选择Source | import,再出现的对话框中点击OK便可建立VHDL文件。之后关闭文本编辑器,进入图三界面,很有可能用户首次建立的工程的芯片默认不是我们实验中用到的ispLSI1016-80LJ44,这时用户可以双击Untitled下面的芯片选择项进行芯片选择。最终与我们实验台上所使用的芯片相符合。之后在Tools中选择Synplicity Synplify 对文件进行编译综合后返回图3窗口。 图3完成上述步骤后,用鼠标单击所指处,出现图4的界面,当然这是所有编译综合都通过后图4情况,对于同学们来说,当然是经过各步骤之后才能得到图示的效果,最后双击最后一项进入下载界面,如图5所示,点击工具栏中的SCAN,来检查电缆是否接好,电源是否接通等,尔后单击Browse加载*.jed文件,按Ctrl+R组合键把所生成的熔丝图文件下载到目标板上。在这里强调的是如果在综合编译综合之后,未及时的将引脚图文件加载进来,系统就会自动根据用户在实体内定义的输入输出引脚而随机的将之锁定在芯片引脚上,这时如果用户按照图5自己定义的引脚连线的话,很可能会出现难以预料的结果,这时用户可以双击图4右框中的Time Explore在出现的多重窗口中选择第一个主窗口,点击即可出现系统的引脚图如图6图6下面简单说明下载完成后的操作,因为在我们的实验台上不能为用户直接提供标准的8Hz频率,这就需要我们通过辅助芯片4020对100KHz的频率进行转换,尽量使之能够满足我们实验的需要,对于74LS4020共有16个引脚,其中8、16分别接GND和VCC(5V),对于11号引脚由于是低有效故也接GND,10号引脚接实验台上的100KHz频率信号,则7号引脚将会输出78KHz的频率,3号引脚输出的是7Hz左右的信号,这时的3号就可对应我们数字频率计所需的CLK了,而7号就相应的对应XCLK了。如果程序运行正常的话,大家检测到的频率也就是数码管上的显示应该是从一个很小的信号快速增达到8000左右的信号,然后重复上述显示,至此我们的数字频率计就完成了。

《VHDL硬件课设.doc》由会员小**分享,可在线阅读,更多相关《VHDL硬件课设.doc》请在金锄头文库上搜索。

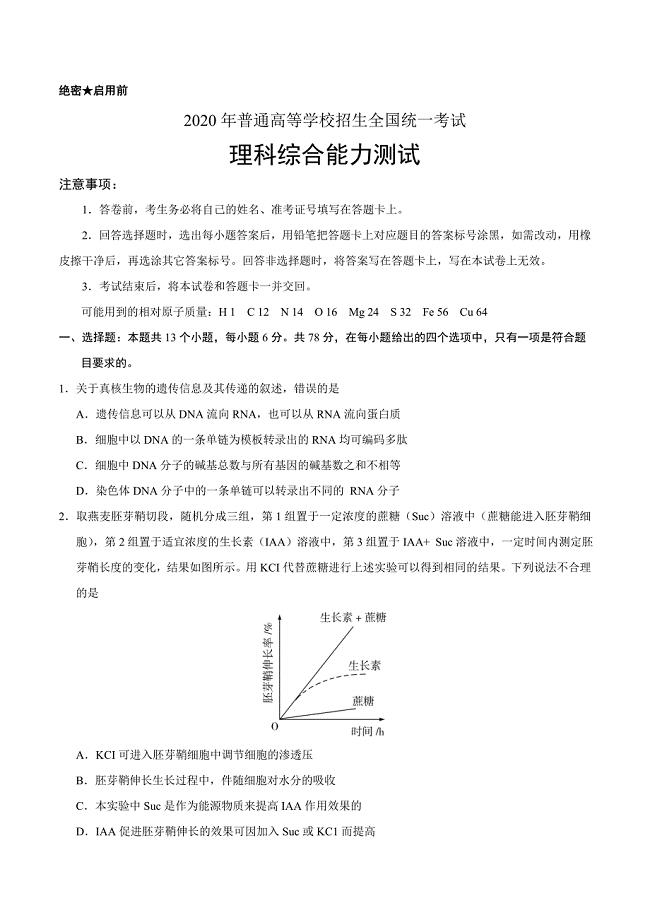

2020年高考真题——理科综合(全国卷Ⅲ)+Word版含答案

2021年绝味鸭脖策划书

2021年熟食店创业方案

2021年熟食店开店策划

2021年卤菜店创业计划书

2021年周黑鸭网络营销策划方案

东大21年1月考试《现代设计方法》考核作业

谈我国行政管理效率的现状及其改观对策(论文)

单证员考试-备考辅导-复习资料:无贸易背景信用证案分析.docx

土木工程毕业生答辩自述.docx

建筑学毕业后工作状态真实写照.doc

C#代码规范(湖南大学).doc

xx区食药监局2019年工作总结及2020年工作计划

2019年中医院药物维持治疗门诊工人先锋号先进事迹

2019年度xx乡镇林长制工作总结

2019年性艾科工作计划书

2019年人才服务局全国扶贫日活动开展情况总结

关于组工信息选题的几点思考

摘了穷帽子 有了新模样

2019年某集团公司基层党支部书记培训班心得体会

09.石油公司制度体系诊断及优化咨询项目

09.石油公司制度体系诊断及优化咨询项目

2024-04-08 33页

职工教育培训经费管理办法(规模生产制造业版)

职工教育培训经费管理办法(规模生产制造业版)

2024-04-08 10页

08.圆通银行战略咨询项目

08.圆通银行战略咨询项目

2024-04-08 25页

企业培训费管理实施暂行细则

企业培训费管理实施暂行细则

2024-04-08 12页

职工教育培训经费管理办法(适合中小企业)

职工教育培训经费管理办法(适合中小企业)

2024-04-08 10页

企业规章制度框架体系管理规定(2024修订版)

企业规章制度框架体系管理规定(2024修订版)

2024-04-08 21页

05.景宏集团全面管理提升咨询项目

05.景宏集团全面管理提升咨询项目

2024-04-08 40页

07.玉兔食品集团供应链咨询项目

07.玉兔食品集团供应链咨询项目

2024-04-08 34页

04.大华乳业业务战略咨询项目

04.大华乳业业务战略咨询项目

2024-04-08 28页

06.德邦公司精益生产管理咨询项目

06.德邦公司精益生产管理咨询项目

2024-04-08 28页