《电子实习2》基于FPGA多功能数字钟设计

32页1、江苏科技大学南徐学院 Jiangsu university of science and technology nanxu college电子实习2基于FPGA多功能数字钟设计姓 名:学 号:.班 级:.指导教师:提交日期:2012 年 3 月摘 要本文介绍了利用EDA技术自顶向下的设计方法,提出了一个多功能数字钟的设计方案,采用VerlogHDL语言设计了数字钟系统的各个模块,在QuartusII开发平台下进行了编译、仿真、下载,实现了基本计时显示和设置、调整时间、闹钟和秒表功能。VHDL是Very High Speed Integrated Circuit Hardware Description Language的缩写,意思是超高速集成电路硬件描述语言。对于复杂的数字系统的设计,它有独特的作用。它的硬件描述能力强,能轻易的描述出硬件的结构和功能。这种语言的应用至少意味着两种重大的改变:电路的设计竟然可以通过文字描述的方式完成;电子电路可以当作文件一样来存储。随着现代技术的发展,这种语言的效益与作用日益明显,每年均能够以超过30%的速度快速成长。本文介绍一种基于FPGA的数字时钟设

2、计方法,简要介绍了VHDL语言的一些基本语法和概念后,进一步应用VHDL,在MAX+plusII 的环境下设计一个电子钟,最后通过仿真出时序图实现预定功能。电子钟的时间显示用到了七段数码管(或称七段显示器)的电路设计,内部的时间控制输出则用到了各种设计,包括:时钟分频模块、计时模块、按键模块和显示模块四个部分。目 录1 引言12 总体方案设计 X2.1 项目设计要点2.2 方案论述2.3 软件介绍2.4 芯片介绍3 单元电路设计3.1 分频模块设计3.2 计时功能模块设计3.3 计数模块3.4 译码显示模块3.5 整点报时模块4 系统功能及功能仿真4.1 系统功能4.2功能仿真各个模块的仿真波形5 心得体会6 参考文献附录:完整实验程序引言VHDL语言是一种标准化的硬件描述语言。设计者可以通过它编写代码,然后用模拟器验证其功能,再将设计代码综合成门级电路,最后下载到可编程逻辑器件(CPLD,FPGA)中来实现一个设计。由于VHDL语言具有支持大规模设计和再利用已有设计等优点1,因此使用VHDL语言来设计数字钟。本设计采用的VHDL是一种全方位的硬件描述语言,具有极强的描述能力,能支持系

3、统行为级、寄存器传输级和逻辑门级这三个不同层次的设计;支持结构、数据流、行为三种描述形式的混合描述,覆盖面广,抽象能力强,因此在实际应用中越来越广泛。ASIC是专用的系统集成电路,是一种带有逻辑处理的加速处理器;而FPGA是特殊的ASIC芯片,与其它的ASIC芯片相比,它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检测等优点。在控制系统中,键盘是常用的输入设备,系统应当根据键盘的输入来完成相应的功能。因此,按键信息输入是与软件结构密切相关的过程。根据键盘结构的不同,采用不同的编码方法,但无论有无编码以及采用什么样的编码,最后都要转换成为相应的键值,以实现按键功能程序的转移。1钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。诸如定时自动报警、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些都是以钟表数字化为基础的。因此研究数字钟以及扩大其应用有着非常现实的意义。2.总体方案设计2.1项目设计要点 (1)以数字形式显示时、分、秒; (2)小时记数为24小时进制 (3)分秒进制为60

4、进制 (4)扩展功能:定时闹钟、整点报时2.2 方案论述 系统组成框图,如下图所示: 主体电路电路的两种工作状态如下图所示:1.为正常时钟模块2.设置时间模块控制按键用来选择是正常计数还是调整时间并决定调整时、分、秒; 置数按键按下时,表示相应的调整块要加一;基准时钟是1HZ;计数器是对1HZ的频率计数;动态显示模块是对计数器的计数进行译码,送到数码管进行显示 。2.3 软件介绍本设计采用Quartus II软件编写所需程序。Quartus II 是Altera公司的综合性PLD开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。 Quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl脚本完成设计流程外,提供了完善的用户图形界面设计方式。具有运行速度快,界面统一,功能集中,易学易用等特点。 Quartus II支持Altera的IP核,包含了LPM/MegaFunction宏功

《《电子实习2》基于FPGA多功能数字钟设计》由会员pu****.1分享,可在线阅读,更多相关《《电子实习2》基于FPGA多功能数字钟设计》请在金锄头文库上搜索。

2023年注册公用设备工程师《基础考试(给排水)》考试全真模拟易错、难点汇编第五期(含答案)试卷号:22

毕业实习报告内容及格式要求

鲁能康保屯垦风电场升压站增容工程环境影响报告资料

幼儿园大班优秀社会教案《感恩的心》教学设计

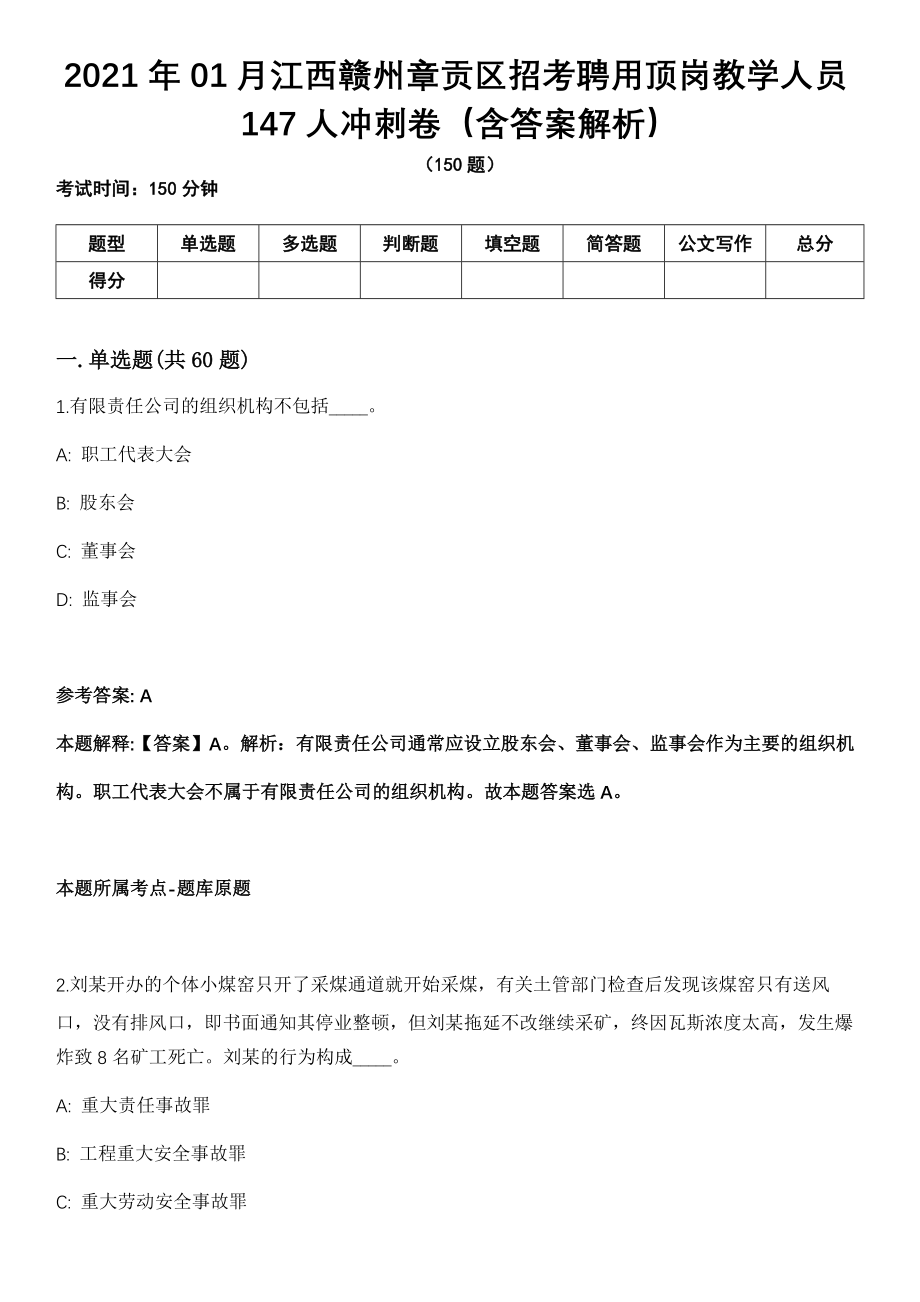

2021年01月江西赣州章贡区招考聘用顶岗教学人员147人冲刺卷(含答案解析)

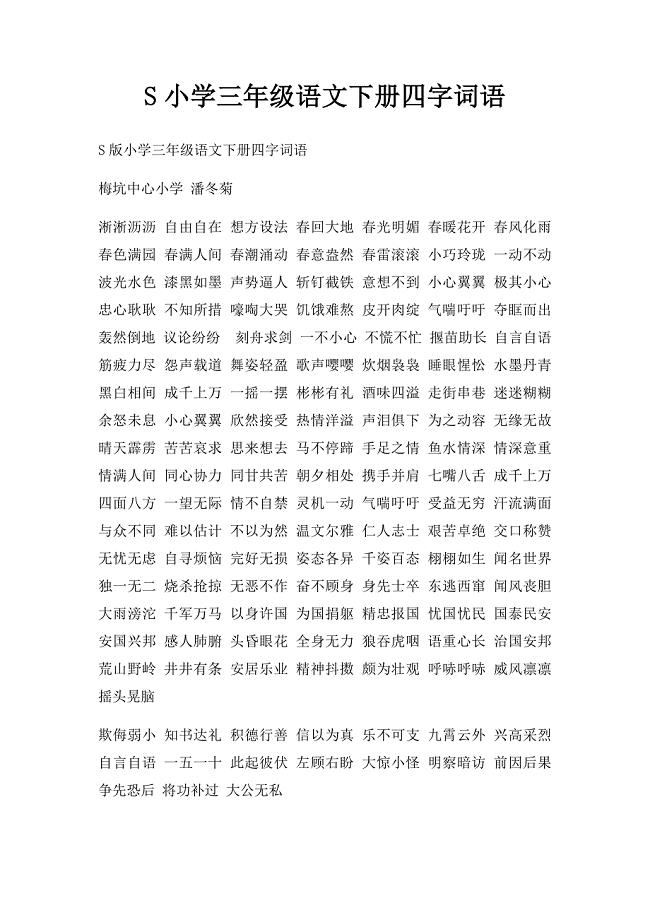

S小学三年级语文下册四字词语

发泡水泥门芯板项目可行性研究报告模板

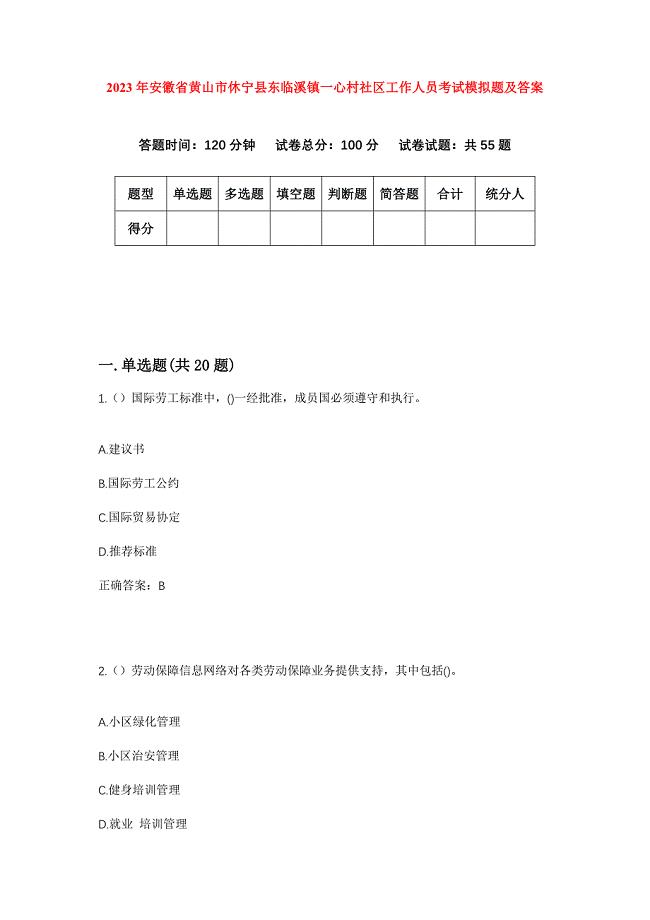

2023年安徽省黄山市休宁县东临溪镇一心村社区工作人员考试模拟题及答案

幼儿园教师师德工作计划范文5篇

牧草种植施工设计方案

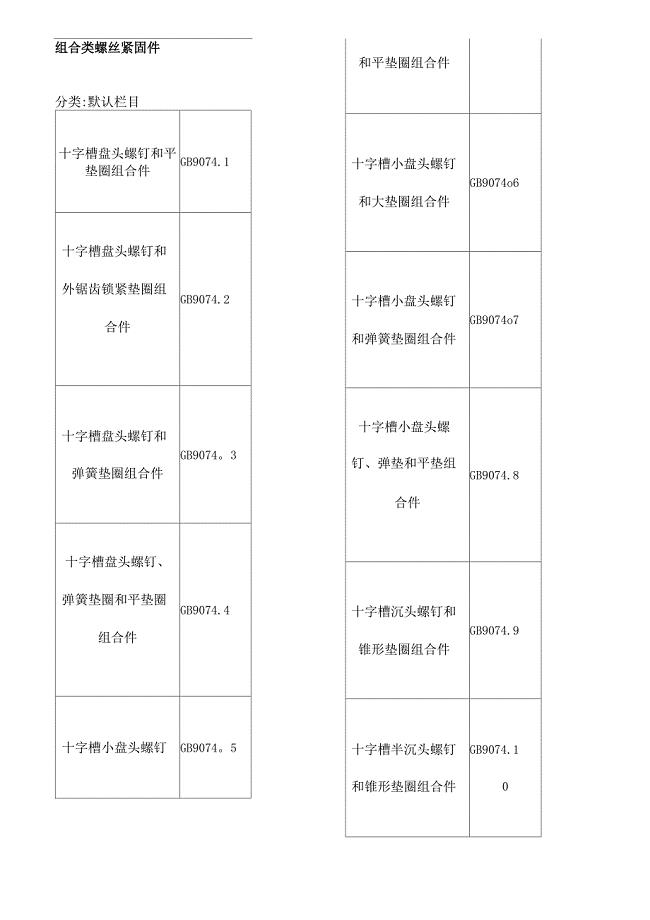

组合类螺丝紧固件

“高效课堂教学”展评暨教师基本功评比活动总结

初中英语重点单词

现在越来越多的煤改电工程使用了电磁锅炉优点有哪些

淘宝客服工作一周总结报告(4篇).doc

艾莫《做最有用的好员工》文稿

年产35万吨高速连续式棒材车间论文

隧道人行横通道施工技术交底

《劳动合同法》、《社会保险法》、《工伤保险条例》实操应对策略

超高层建筑施工测量方案

6S管理与持续改善

6S管理与持续改善

2023-07-30 4页

越努力越幸运作文

越努力越幸运作文

2023-08-29 8页

![[IT计算机]LSI MegaRAID SAS Software UGLSI SAS RAID卡配置中文版](/Images/s.gif) [IT计算机]LSI MegaRAID SAS Software UGLSI SAS RAID卡配置中文版

[IT计算机]LSI MegaRAID SAS Software UGLSI SAS RAID卡配置中文版

2023-03-13 104页

2022年关于难忘的小学作文300字八篇

2022年关于难忘的小学作文300字八篇

2023-02-27 9页

小学生防溺水主题班会教案设计暑假

小学生防溺水主题班会教案设计暑假

2023-05-30 23页

以等待花开为话题作文集锦

以等待花开为话题作文集锦

2023-05-19 10页

公司人力资源工作计划范文

公司人力资源工作计划范文

2023-09-07 6页

2022施工合同模板汇编9篇

2022施工合同模板汇编9篇

2024-01-10 56页

住宅租赁合同集锦8篇

住宅租赁合同集锦8篇

2023-02-23 32页

住家保姆合同汇编五篇

住家保姆合同汇编五篇

2023-09-13 22页