HLS-矩阵乘法单元设计与SDK测试

26页1、 HLS矩阵乘法单元设计与SDK测试 目录o 一、引言o 二、程序框架o 三、初步设计o 四、报告分析o 五、优化操作o 六、接口优化o 七、上板测试o 八、补充部分o 九、时间与参考一、引言矩阵乘法,涉及数组优化、循环优化和接口优化等。是一个学习HLS非常好的Lab。HLS新建工程这些就不记录了,在新建时有个需要注意,就是Clock Period的设置,如果设为10,会按照100MHz时钟来进行优化,如果一次运算15ms,就会分配到两个时钟来计算。但HLS工具预估是比较保守的,比如预估一次运算15ms,但实际上板卡后这个运算,就只要7ms。因此可以把周期稍微放大些/减轻约束压力,让HLS在做优化时,能放在一个周期内完成,但如果达不到约定的时钟频率,是可以进行更改的。在新建后的工程右键Project Settings,来进行更改。二、程序框架有Source、Include源代码和Test Beach目录。用于实现矩阵乘法功能的代码,放在Source目录下。用于测试矩阵乘法功能的代码,放在Test Beach目录下。新建文件:matrix_mul.cpp、matrix_mul.h和mai

2、n.cpp。在matrix_mul.h文件中,使用#ifdef 宏的方式,来避免重复声明某些内容。三、初步设计还未进行优化前的基本功能设计。1、matrix_mul.h文件任意精度定点数:在传统C中,char、int、short、long等的位宽都是固定的,8位、32位、16位和64位。如果电路中要求10位宽的数据,则常规变量无法实现,HLS为了能满足需求,搞了一种ap_int类型的数据变量,内放的是该类型变量的位宽,可以认为ap_int A与char B,是两种类型相同的变量。#ifndef _MATRIX_MUL_#define _MATRIX_MUL_/ HLS提供的任意精度定点数文件#include ap_fixed.h/ A元素对应行,与B元素对应列,进行相乘得到Cvoid matrix_mul(ap_int A44, ap_int B44, ap_int C44);#endif2、matrix_mul.cpp文件#include matrix_mul.hvoid matrix_mul(ap_int A44, ap_int B44, ap_int C44)for(int i=

3、0;i4;i+)for(int j=0;j4;j+)Cij=0;/ 循环乘四次,并进行相加for(int k=0;k4;k+)Cij=Cij+Aik*Bkj;3、main.cpp文件#include matrix_mul.h#include int main()ap_int A44;ap_int B44;ap_int C44;/ 初始化赋值0、1、2、3、4、5.for(int i=0;i4;i+)for(int j=0;j4;j+)Aij=i*4+j;Bij=Aij;matrix_mul(A, B, C);for(int i=0;i4;i+)for(int j=0;j4;j+)std:coutCi,j=Cijstd:endl;return 0;代码写完,第一步要跑C Simulation,用快捷键Ctrl + B,就可以进行编译了。生成exe文件,就证明没有语法错误。然后,在菜单栏里,有一个Run C Simulation,点后进行C仿真,来看结果是否正确。是纯C语言的仿真。第二步进行综合,点菜单栏的Run C Synthesis。可能会出现下面这个“The function mus

4、t be specified”错误,原因是可能有很多C函数,但哪个是顶层,需要确定下。在工程中右键Project Settings,选择Synthesis选项卡,将Top Function设置为matrix_mul,就可以跑综合了。四、报告分析综合完,会生成Synthesis的报告文件,下边对该文件的几个关键参数进行分析。1、Performance Estimates,性能估计。1Timing:包含clock,时钟约束。2Latency:在Summary中,包含了Latency与Interval,初步设计中,Latency为169,表示这个矩阵乘法的函数模块,需要耗时169个时钟周期。Interval是这次矩阵乘法与下一次,需要间隔多少周期,由于没有进行流水线的设计,这里需要间隔169个时钟周期,才能进行下一个的矩阵运算,因此Interval等于169。在Detail中,有循环内部的一些细节,可以看到每个循环需要的一些周期数,有些循环可能需要状态跳转,会消耗一部分的时钟周期。后续优化,主要也是照着Latency来进行优化。2、Utilization Estimates,资源利用率估计。

《HLS-矩阵乘法单元设计与SDK测试》由会员Baige****0346分享,可在线阅读,更多相关《HLS-矩阵乘法单元设计与SDK测试》请在金锄头文库上搜索。

员工积极主动行为的组态效应:基于过程的视角

汪晖齐物平等与跨体系社会的天下想象

函数性质中的数学抽象在问题解决与设计中的应用

日本东京大学入学考试理科数学试题解析

二次电池研究进展

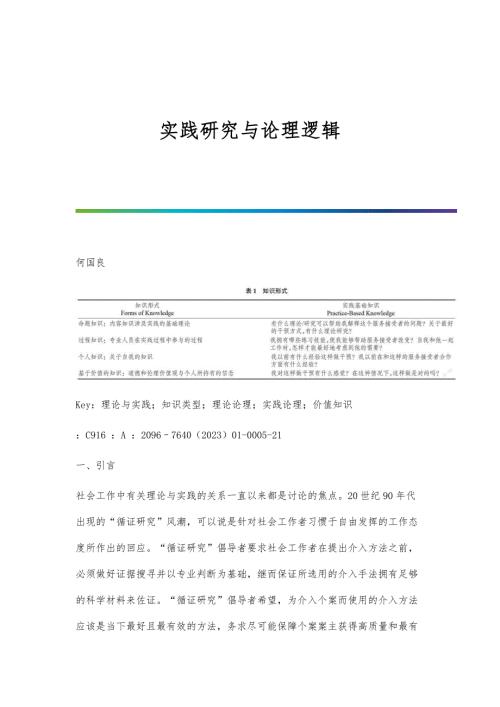

实践研究与论理逻辑

光学视觉传感器技术研究进展

龙泉青瓷的传承困境与发展

齐齐哈尔地区抗根肿病大白菜品种的抗性鉴定与评价

基于系统动力学模型的胶州湾海域承载力预测

基于弯液面电化学连接碳纤维实验初探

龟甲胶研究发展探析

鼻腔黏膜免疫佐剂鞭毛蛋白的研究进展

鼻内镜辅助上颌骨部分切除术治疗鼻腔鼻窦腺样囊性癌的临床分析

黑豆不同发芽期多酚、黄酮及抗氧化活性分析

齐鲁青未了:山东当代文学审美流变论

黄登水电站机电设备安装工程施工技术质量管理

黄河文化传承视角下音乐剧创作探究

黄亦琦从风论治咳嗽变异性哮喘经验※

鲸豚动物吸附式声学行为记录器综述

Kotlin设计模式实现之装饰者模式

Kotlin设计模式实现之装饰者模式

2022-03-24 12页

《信息安全系统设计基础》第三周学习总结

《信息安全系统设计基础》第三周学习总结

2022-03-24 11页

《信息安全系统设计基础》第四周学习总结

《信息安全系统设计基础》第四周学习总结

2022-03-24 10页

MVC思想及SpringMVC设计理念

MVC思想及SpringMVC设计理念

2022-03-24 25页

Jmeter接口测试数据库断言的实现与设计

Jmeter接口测试数据库断言的实现与设计

2022-03-24 13页

揭秘Spring类型转换-框架设计的基石

揭秘Spring类型转换-框架设计的基石

2022-03-24 18页

《信息安全系统设计基础》第1周学习总结

《信息安全系统设计基础》第1周学习总结

2022-03-24 10页

Kafka核心设计与实践原理总结-进阶篇

Kafka核心设计与实践原理总结-进阶篇

2022-03-24 32页

Activiti命令拦截器和设计模式

Activiti命令拦截器和设计模式

2022-03-24 8页

设计模式春招面试复习-命令模式

设计模式春招面试复习-命令模式

2022-03-24 9页