地址转换过程的模拟实现课程设计报告汇总

52页1、淮阴工学院操作系统课程设计报告选题名称:地址转换过程的模拟实现系(院):经济管理学院专业:信息管理与信息系统班级:姓名:学号:姓名:学号:姓名:学号:姓名:学号:指导教师:学年学期:学年第学期年月日设计任务书课题名称地址转换过程的模拟实现设计目的1 .理解地址转换相关理论。2 .熟悉地址转换的过程。3 .掌握常用地址转换算法的实现过程。实验环境1 .硬件:PC机,奔腾IV以上CPU,512MB以上内存,80G以上硬盘。2 .软件:Windows2000/XP、MicrosoftVisualC+6.0。任务要求1 .搜集地址转换过程的模拟实现可能涉及到的知识和相关资料。2 .应用MicrosoftVisualC+6.0集成开发环境,设计并实现一个地址转换模拟程序。3 .确保地址转换模拟程序能正确运行。4 .参加答辩,撰写课程设计报告。工作进度计划在舁厅P起止日期工作内容12013.12.14课题任务下达,查阅文献资料22013.12.52013.12.17课题总体设计、素材搜集与处理32013.12.182013.12.20课题详细设计、调试、完善设计42013.12.21答辩,撰写报告

2、指导教师(签章):年月日摘要:本课程设计主要针对地址转换相关理论进行设计,程序能模拟出操作系统常用的地址转换算法,包括可变分区存储管理的地址转换、分页存储管理的地址转换、分段存储管理的地址转换和段页式存储管理的地址转换。具体来说,把整个内存分成大小相等内存块,内存块从0开始依次编号。把用户程序分成若干段,每段有个段名。页面的大小和内存块相同,每段的各个页面都分别从0开始依次编号。虚拟空间的最小单位是页而不是段,内存就被分为若干个页,且每段所拥有的程序和数据在内存中可以分开存放,分段大小也不再受内存可用区的限制。程序模拟实现了四种地址转换方式,从中观察各种方法的优缺点及应用特点。段页式存储管理系统,用分段的方法来分配和管理虚拟存储器,而用分页的方法来分配和管理主存。既有段式系统便于实现段的共享,段的保护,动态链接和段的动态增长等一系列优点,又能像页式系统那样,很好地解决内存的外碎片问题。关键词:地址转换,虚拟地址,物理地址,偏移,越界1 需求分析11.1 可变分区存储管理的地址转换11.2 分页存储管理的地址转换41.3 分段存储管理的地址转换51.4 段页式存储管理的地址转换62 概要

3、设计152.1 可变分区存储管理的地址转换的概要设计152.2 分页存储管理的地址转换的概要设计192.3 分段存储管理的地址转换的概要设计202.4 段页式存储管理的地址转换的概要设计243 详细设计263.1 可变分区存储管理的地址转换的详细设计263.2 分页存储管理的地址转换的详细设计313.3 分段存储管理的地址转换的详细设计363.4 段页式存储管理的地址转换的详细设计384 调试与操作说明434.1 可变分区存储管理的地址转换的操作说明434.2 分页存储管理的地址转换的操作说明434.3 分段存储管理的地址转换的操作说明444.4 段页式存储管理的地址转换的操作说明45总结46致谢47参考文献48附录491需求分析本课程设计题目:地址转换过程的模拟实现。课程设计任务及要求:( 1)搜集地址转换过程的模拟实现可能涉及到的知识和相关资料。( 2)应用MicrosoftVisualC+6.0集成开发环境,设计并实现一个地址转换模拟程序。( 3)确保地址转换模拟程序能正确运行。( 4)参加答辩,撰写课程设计报告。运行环境:WindowsXP系统Pentium(R)Dual-co

4、reCPU3.20GHz1.96G内存200G硬盘。开发工具:本实验使用VC+6.0平台,使用基本的控制台应用程序,单文档结构,主要数据结构是结构体间的关系。打开VC+6.0建立一个新的C+源文件,根据数据结构编写代码。1.1 可变分区存储管理的地址转换一、任务要求该程序要对每一个虚地址计算其代表的有效地址所对应的物理地址,并进行越界判断,打印出每个虚地址的物理地址。能够输入进程名称和内存需求量,按页式存储管理方式把进程分成若干页,分配到内存中的若干个块中,同时生成并显示相应的页表。输入一个逻辑地址能够转换并输出相应的物理地址。二、基本思想可变分区的基本原理是:可变分区是指在作业装入是,依据它对内存空间实际的需求量来划分内存的分区,因此,每个分区的尺寸与进入他的作业大小相同。它能有效解决固定分区的内存碎片问题,是一种较为常用的存储管理方法。因为在系统运行过程中,内存中分区的数目和大小都是可变的,所以这种可变式分区也称为动态分区8。三、存储器的基本性能参数评价存储器性能的参数主要有三个方面:容量、速度与价格。存储器容量用S=WAl将表示,W为存储器字长,l为存储器字数,m则为存储器体数。

《地址转换过程的模拟实现课程设计报告汇总》由会员枫**分享,可在线阅读,更多相关《地址转换过程的模拟实现课程设计报告汇总》请在金锄头文库上搜索。

湛江电解铜箔技术应用项目商业计划书【范文】

办公室工作总结房管局办公室工作总结例文

内蒙古巴彦淖尔市磴口县九年级语文上学期期末考试试题无答案新人教版

玻璃工程质量通病和预防

电缆敷设规范超强研究材料

八年级语文上册第三单元15说“屏”同步练习无答案新版新人教版0722126

保密工作管理制度

城市实用版的房屋租赁合同.doc

简易商铺租赁合同书标准范文(八篇).doc

供应商管理该沪深要求

关于设立民办文山学院附属学校的可行性报告

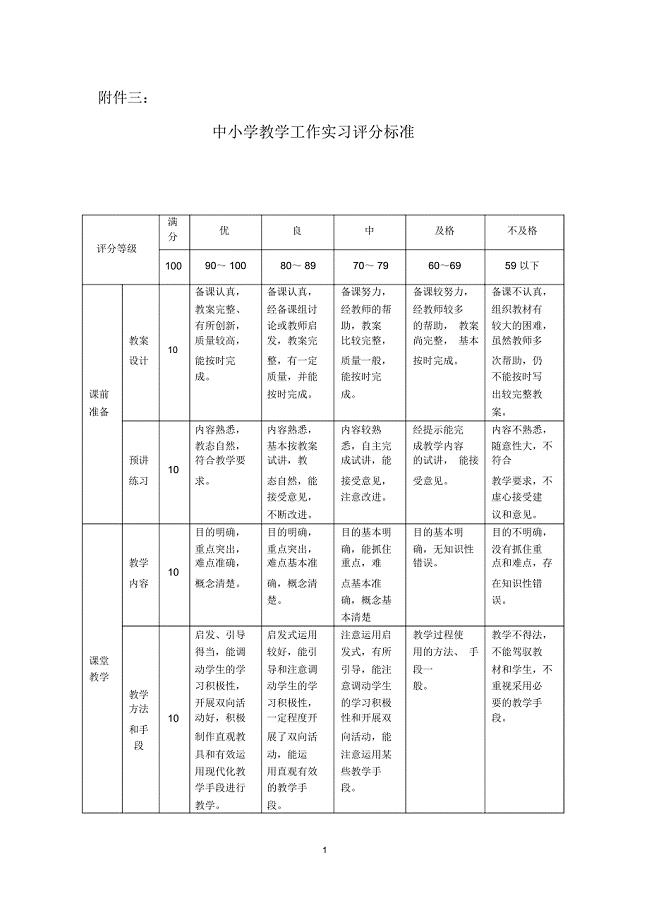

湛师基础教育学院教育实习工作条例-岭南师范学院基础教育学院

2023高三学生自我鉴定通用15篇

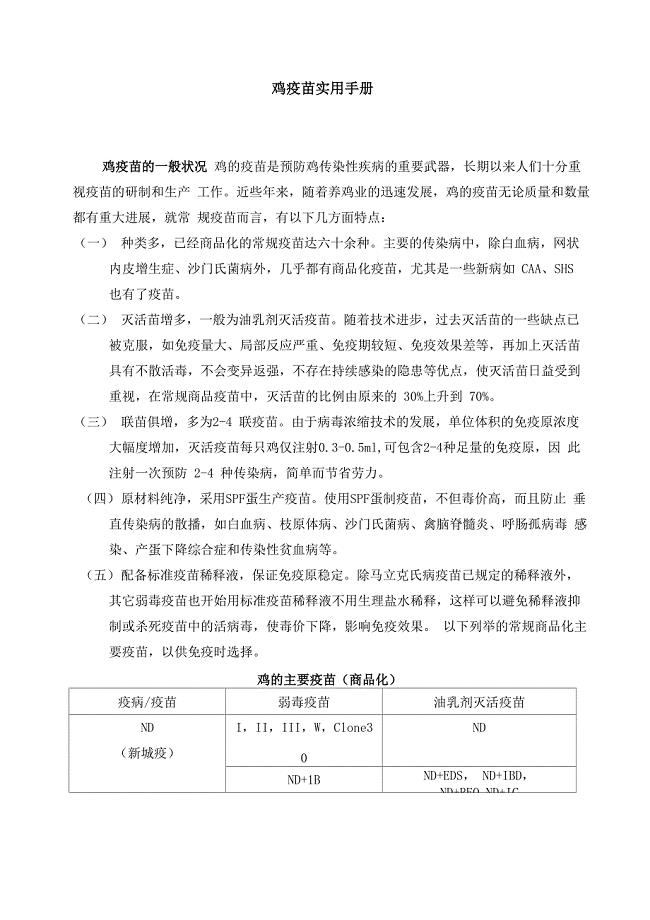

鸡疫苗实用手册

2023实习生保险公司实习报告总结(4篇).doc

大学生防骗心得体会

2023学年度第二学期三年级语文教学工作总结(2篇).doc

前台文员实习报告

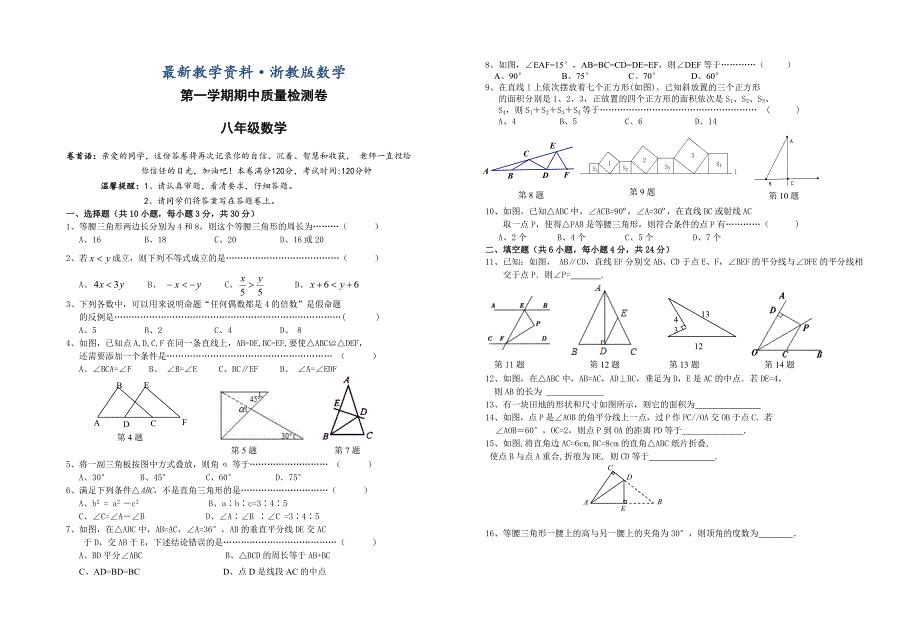

最新浙教版数学八年级第一学期期中质量检测试卷含答案

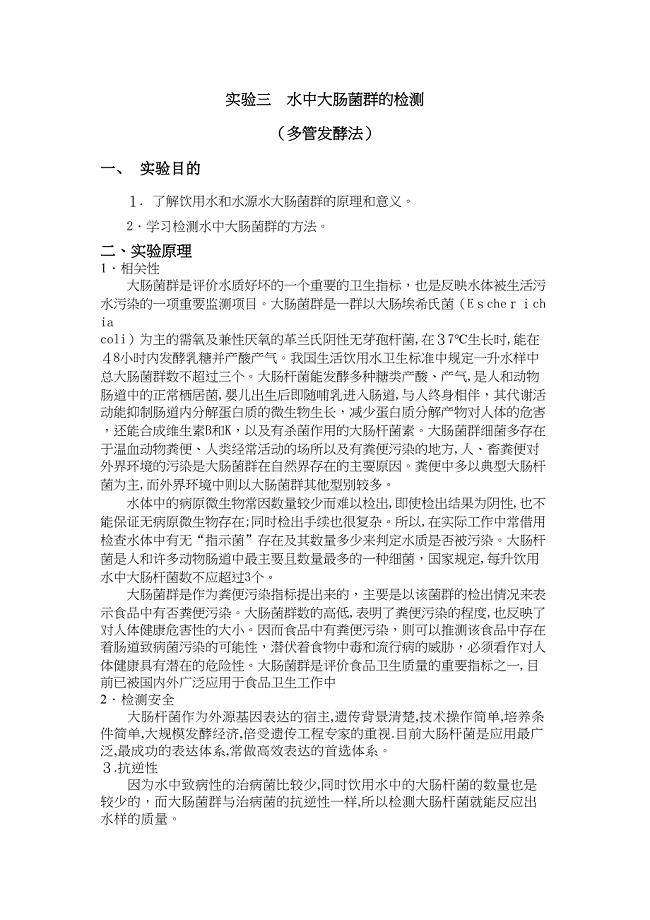

水中大肠菌群的培养

幼儿园校车运行方案

幼儿园校车运行方案

2022-09-26 2页

横一路WW68-72顶管专项施工方案-改

横一路WW68-72顶管专项施工方案-改

2023-08-07 47页

建筑工程项目安全生产承诺书(参考版本)

建筑工程项目安全生产承诺书(参考版本)

2024-01-15 5页

大学校园广播站招新计划

大学校园广播站招新计划

2023-07-09 5页

圆的周长和面积练习题

圆的周长和面积练习题

2022-11-01 3页

IBM营销策略纲要

IBM营销策略纲要

2023-02-24 23页

重大危险源监控及管理制度

重大危险源监控及管理制度

2022-09-19 34页

高速公路标深基坑专项施工方案

高速公路标深基坑专项施工方案

2023-04-08 39页

试谈提高个人执行力

试谈提高个人执行力

2022-09-22 11页

ago_外资企业考勤制度

ago_外资企业考勤制度

2022-12-14 8页