EDA实验 基于Libero的数字逻辑设计仿真及验证实验

40页1、计算机学院计算机科学与技术专业14级1班学号3114005811姓名梁智斌教师评定实验题目基于Libero的数字逻辑设计仿真及验证实验1、熟悉EDA工具的使用;仿真基本门电路。2、仿真组合逻辑电路。3、仿真时序逻辑电路。4、基本门电路、组合电路和时序电路的程序烧录及验证。5、数字逻辑综合设计仿真及验证。实验报告1、基本门电路一、实验目的1、了解基于Verilog的基本门电路的设计及其验证。2、熟悉利用EDA工具进行设计及仿真的流程。3、学习针对实际门电路芯片74HC00、74HC02、74HC04、74HC08、74HC32、74HC86进行VerilogHDL设计的方法。二、实验环境Libero仿真软件。三、实验内容1、掌握Libero软件的使用方法。2、进行针对74系列基本门电路的设计,并完成相应的仿真实验。3、参考教材中相应章节的设计代码、测试平台代码(可自行编程)完成74HC00、74HC02、74HC04、74HC08、74HC32、74HC86相应的设计、综合及仿真。4、提交针对74HC00、74HC02、74HC04、74HC08、74HC32、74HC86(任选一个)的

2、综合结果,以及相应的仿真结果。四、实验结果和数据处理1、所有模块及测试平台代码清单/74HC00代码-与非moduleHC00(A,B,Y);input4:1A,B;output4:1Y;assignY=(A&B);/与非endmodule/74HC00测试平台代码timescalelns/lnsmoduletestbench();reg4:la,b;lwire4:1y;HC00u1(a,b,y);initialbegina=4b0000;b=4b0001;#10b=b1;#10b=b1;#10b=b1;a=4b1111;b=4b0001;#10b=b1;#10b=b1;#10b=b1;endendmodule/74HC02代码-或非modulehc02(A,B,Y);inputA,B;outputY;assignY=(AIB);/Z或非endmodule/74HC02测试平台代码timescalelns/lnsmoduletest74hc02;rega,b;wirey;hc02u02(a,b,y);initialbegin#20a=0;b=0;#20a=l;#20b=l;#20b=0

3、;endendmodule/74HC04代码-非modulehc04(A,Y);inputA;outputY;assignY=A;endmodule/74HC04测试平台代码timescalelns/lnsmoduletest74hc04;rega;wirey;hc04u04(a,y);initialbegin#20a=0;#20a=l;endendmodule/74HC08代码-与moduleHC08(A,B,Y);inputA,B;outputY;assignY=A&B;endmodule/74HC08测试平台代码timescalelns/lnsmoduletest74HC08;rega,b;wirey;HC08u08(a,b,y);initialbegin#20a=0;b=0;#20b=l;#20a=l;#20b=0;endendmodule/74HC32代码-或moduleHC32(A,B,Y);inputA,B;outputY;assignY=A|B;endmodule/74HC32测试平台代码timescalelns/lnsmoduletest74HC32;rega,b;w

4、irey;HC32u32(a,b,y);initialbegin#20a=0;b=0;#20b=1;#20a=1;#20b=0;endendmodule/74HC86代码-异或moduleHC86(A,B,Y);inputA,B;outputY;assignY=(A&B)|(B&A);endmodule/74HC86测试平台代码timescalelns/lnsmoduletest74HC86;rega,b;wirey;HC86u86(a,b,y);initialbegin#20a=0;bEfCTrmHa.cjwwnnmMTi1.*hihiup*rircncwi$one-甲3暮中4中算鸟嗨AP乃笔4、第二次仿真结果(综合后)(截图)。回答输出信号是否有延迟,延迟时间约为多少?答:信号存在延时,延时约为0.3ns5、第三次仿真结果(布局布线后)(截图)。回答输出信号是否有延迟,延迟时间约为多少?分析是否有出现竞争冒险。i庁丄七盂直巳勺仝黑匚电左凸衣叵劭丰亡上上色,订_a独氏囊致乞itjr_rtInilL!IZwINph:Iu答:信号存在延时,延时约为4.2存在竞争冒险#2、组合逻辑电路一、

《EDA实验 基于Libero的数字逻辑设计仿真及验证实验》由会员博****1分享,可在线阅读,更多相关《EDA实验 基于Libero的数字逻辑设计仿真及验证实验》请在金锄头文库上搜索。

细胞培养的操作步骤修改3

(word版)房地产年终工作总结模板汇编5篇

是安全月生产活动总结

安全教育第一课

学校卫生保健工作计划

三亚重组抗体项目可行性研究报告模板范文

苏教版化学选修4《化学反应原理》全册教案(教育精品)

2023年辽宁省申报评审高、中级专业技术资格破格条件

arcgis考试上机终极版

优秀员工的发言稿范文

中国一次性输液器市场供需预测与未来发展趋势报告

不可压缩流体恒定流动量定律实验

排土场安全生产现场检查表

校园安全事故报告制度

运动会演讲稿

一年级看拼音写词语(田字格)

幼儿园中班主题活动教案《认识“五一”劳动节》含反思

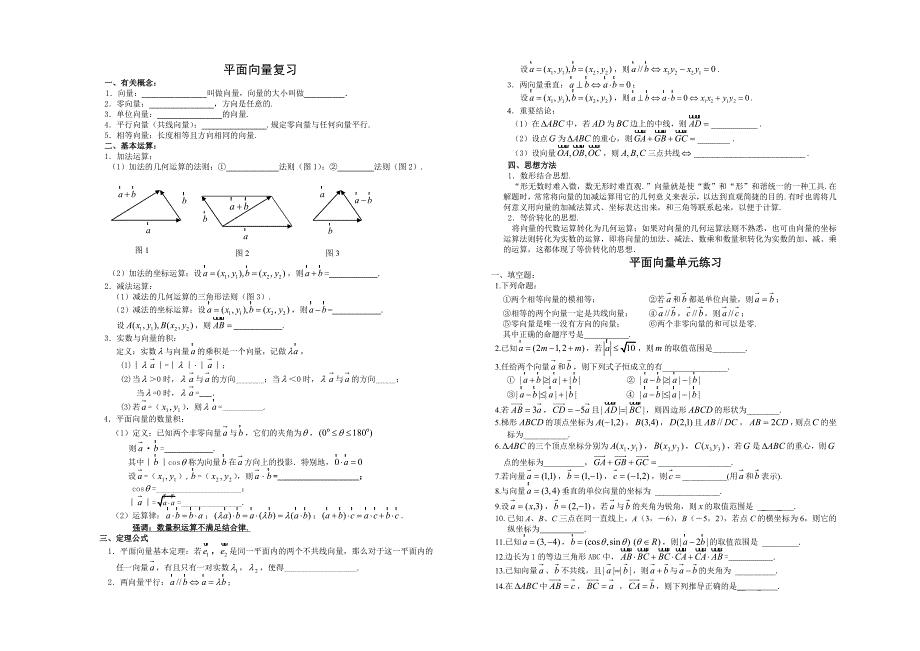

平面向量复习

泊头市产业用纺织品项目分析报告

2022年描写参观作文

工业集中区污水处理工程项目商业计划书写作模板

工业集中区污水处理工程项目商业计划书写作模板

2023-11-20 41页

2019高三英语一轮复习完形填空训练教育.doc

2019高三英语一轮复习完形填空训练教育.doc

2023-12-18 4页

三亚重组抗体项目可行性研究报告模板范文

三亚重组抗体项目可行性研究报告模板范文

2024-01-27 122页

年产30万千升啤酒智能化生产基地项目创业计划书写作模板

年产30万千升啤酒智能化生产基地项目创业计划书写作模板

2023-01-06 42页

关于虫子的作文6篇

关于虫子的作文6篇

2023-04-28 2页

大学生总结自我评价

大学生总结自我评价

2023-08-05 5页

九年级物理压强和浮力单元检测16

九年级物理压强和浮力单元检测16

2022-10-26 4页

银行危机公关与声誉风险管理培训

银行危机公关与声誉风险管理培训

2023-03-09 22页

厦门电触头项目商业计划书范文

厦门电触头项目商业计划书范文

2023-06-22 111页

虹口区电子信息项目可行性分析报告【参考范文】

虹口区电子信息项目可行性分析报告【参考范文】

2022-08-21 123页