四川大学数字逻辑实验报告6

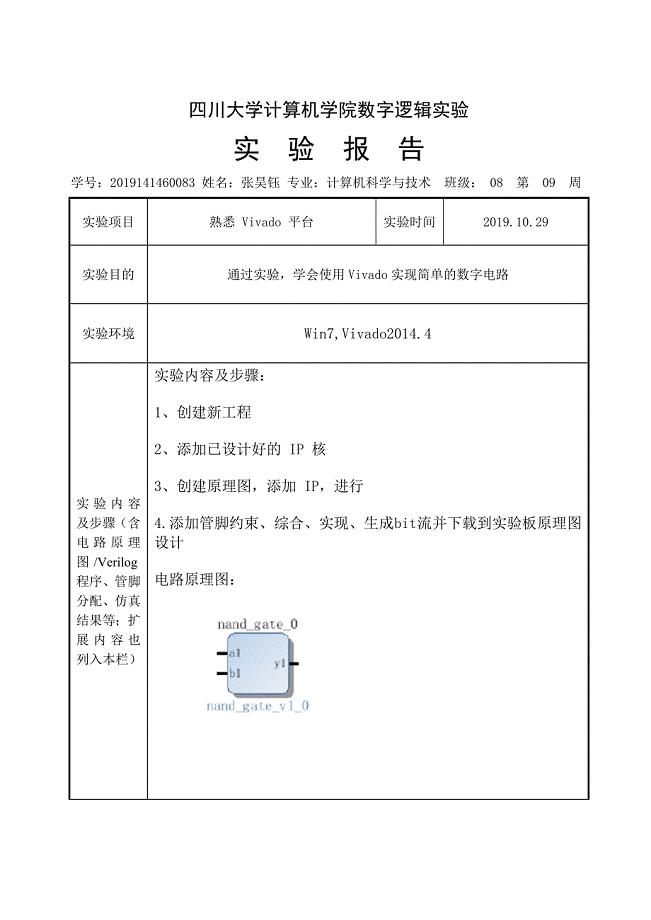

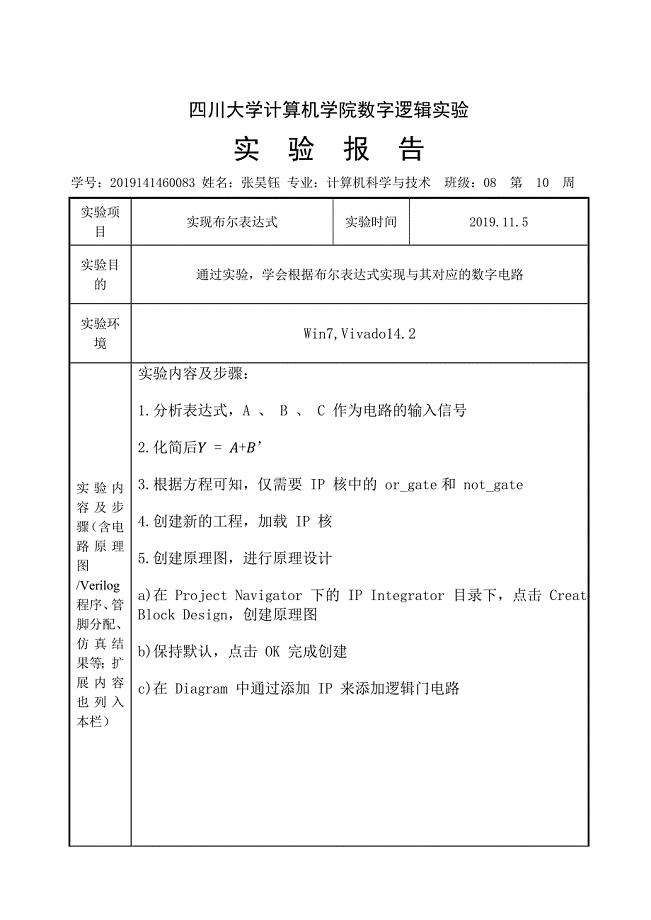

4页1、四川大学计算机学院数字逻辑实验实 验 报 告学号:2019141460083 姓名:张昊钰 专业:计算机科学与技术 班级:08 第 14 周 实验项目设计一个 4 位循环移位寄存器实验时间2019.12.03实验目的 通过实验,学会设计寄存器实验环境 Win7,Vivado14.2实验内容及步骤(含电路原理图/Verilog程序、管脚分配、仿真结果等;扩展内容也列入本栏) 实验步骤: (1)分析输入、输出;根据原理图和 IP 核库判断需要使用的门电路以及个数(2)按照模块化设计流程,新建工程,并且导入正确的 IP 核,准备新建BlockDesign 文件(3)参考原理图,在导入的 IP 核中选择 D 触发器进行 BlockDesign 设计,并且加入清零和置位功能接口,清零端和置位端都是低有效,将上一个寄存器的输出接到下一个寄存器的输出端,最后一个寄存器的输出接到第一个寄存器的输入,实现循环移位(4)BD 文件设计好之后,点击 Generate Output Products 和 Create HDL Wrapper,之后进入 RTL 分析,进行引脚分配 (5)把寄存器输入,清零端和置

2、位端接到开关引脚上面,把输出接到 LED 灯引脚上面,把 CLK 接到时钟 W5 引脚上 (6)引脚分配完成之后进行综合,分析,生成比特流,最后下载到实验板上面进行验证实验结果:当清零端为低电平时,四个 LED 灯都不亮代表寄存器输出为 0,当置位端为低电平时四个 LED 灯全部亮,代表寄存器输出为 1,当清零和置位端为高电平时,LED 会根据存储在寄存器中的内容进行循环位移。实际操作时应注意先使用CLR开关清零,然后使用PRE开关置位(如0100),然后将 5 个开关都同时置为高电平,这样才能观察到开始循环移(接上)实验内容及步骤(含电路原理图/Verilog程序、管脚分配、仿真结果等;扩展内容也列入本栏)注意事项: (1)实验板 W5 引脚的时钟频率为 100MHz (2)IP 核中 lab_clk 为分频器输入频率为 100MHz,输出频率为 2Hz(3)正沿触发 D 触发器的清零端 clr 和置位端 pre 低电平有效,不能留有空脚,否则无法实现清零和置位功能(4)本实验引脚分配较多,在引脚分配时要注意,最好按照开关,LED 灯对应分配,方便观察实验现象 (5)在设计 4 位并

《四川大学数字逻辑实验报告6》由会员Ide****t钰分享,可在线阅读,更多相关《四川大学数字逻辑实验报告6》请在金锄头文库上搜索。

中华文化课考卷

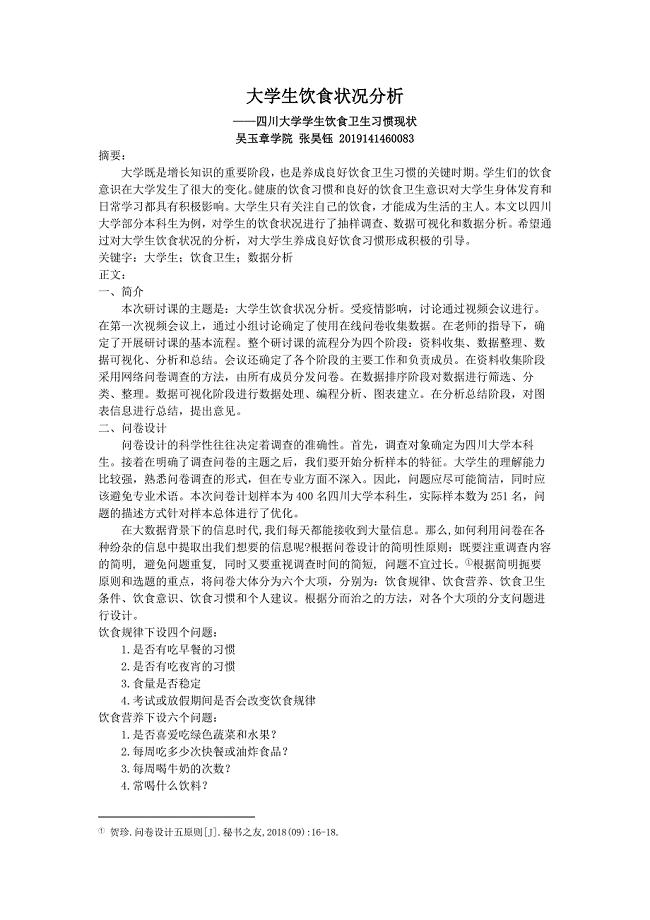

seminar大学生饮食习惯分析

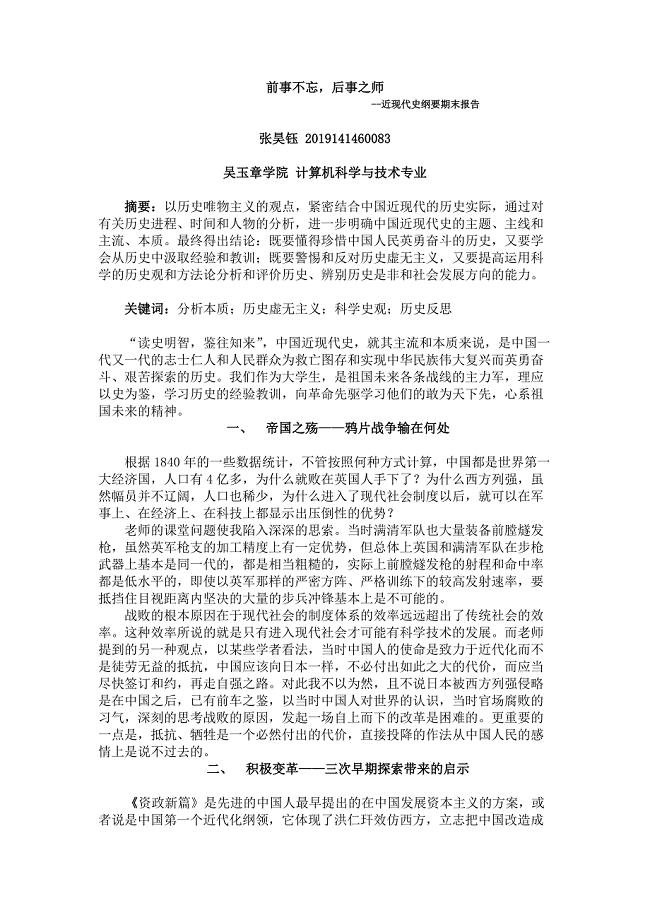

四川大学近现代史纲要期末论文

四川大学数字逻辑实验报告6

四川大学汇编程序设计第四次实验报告

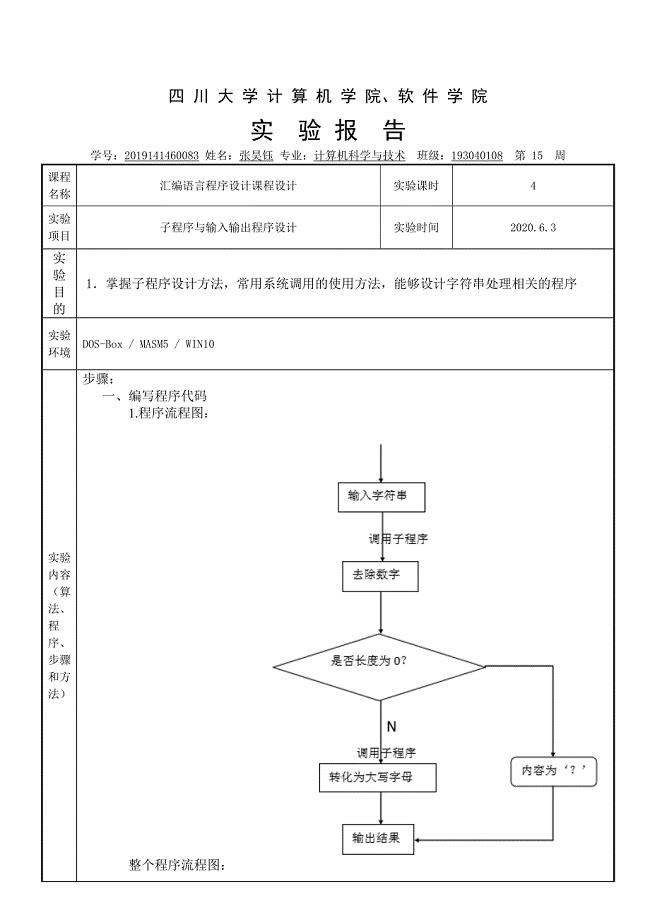

四川大学汇编程序设计第五次实验报告

四川大学汇编程序设计第一次实验报告

四川大学计算机导论实验报告

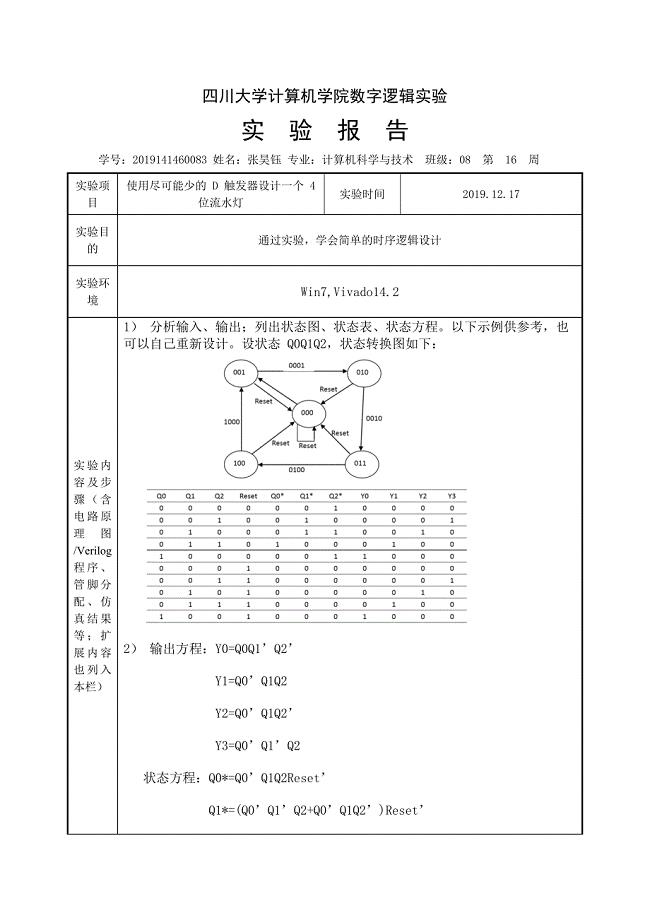

四川大学数字逻辑实验报告8

四川大学汇编程序设计第二次实验报告

四川大学汇编程序设计第三次实验报告

四川大学数字逻辑实验报告7

四川大学数字逻辑实验报告3

四川大学数字逻辑实验报告5

四川大学数字逻辑实验报告4

四川大学数字逻辑实验报告1

四川大学数字逻辑实验报告2

四川大学计算机学院新生研讨课报告增强现实技术(2)

四川大学计算机学院新生研讨课报告期末报告(4)

四川大学计算机学院新生研讨课报告自然语言处理(3)

5000 m3-d印染废水处理工艺设计

5000 m3-d印染废水处理工艺设计

2024-01-03 50页

矿井通风与安全课程设计--塔山矿1500万t-a新井通风设计

矿井通风与安全课程设计--塔山矿1500万t-a新井通风设计

2024-01-03 57页

《虚拟仪器设计》实验指导书

《虚拟仪器设计》实验指导书

2023-12-29 56页

住宅承接查验表格

住宅承接查验表格

2023-12-19 80页

(全)物业承接查验操作指南

(全)物业承接查验操作指南

2023-12-19 371页

机械设计基础课程设计任务书--机械厂装配车间输送带传动装置设计

机械设计基础课程设计任务书--机械厂装配车间输送带传动装置设计

2023-12-15 43页

一例猪圆环病毒病的诊断与治疗

一例猪圆环病毒病的诊断与治疗

2023-12-15 14页

网上资源操作系统实验报告

网上资源操作系统实验报告

2023-12-15 30页

机械专业综合课程设计说明书--落料拉伸复合模

机械专业综合课程设计说明书--落料拉伸复合模

2023-12-15 28页

承接查验评分表

承接查验评分表

2023-12-15 16页