四川大学数字逻辑实验报告2

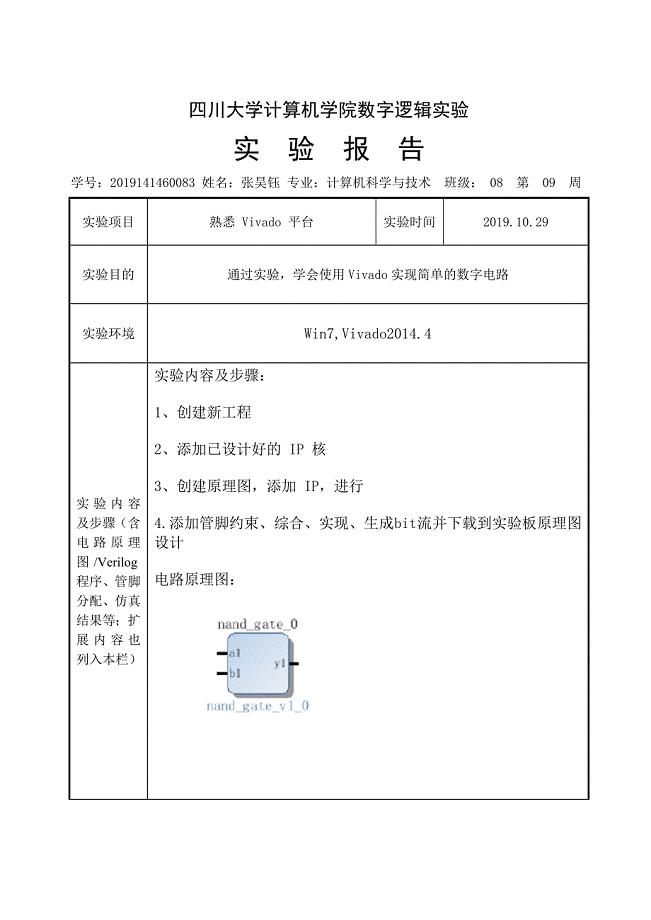

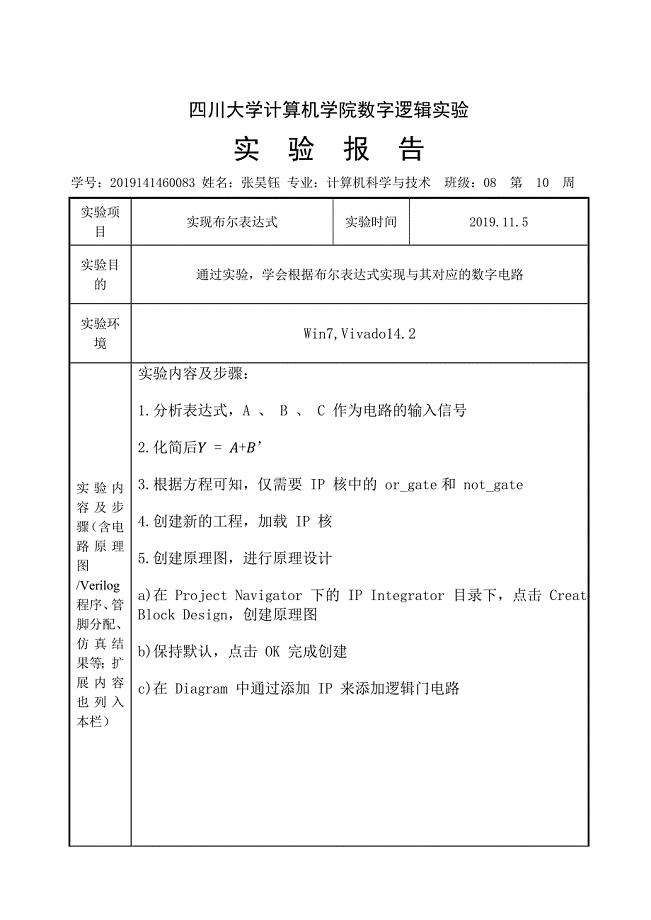

4页1、四川大学计算机学院数字逻辑实验实 验 报 告学号:2019141460083 姓名:张昊钰 专业:计算机科学与技术 班级:08 第 10 周 实验项目实现布尔表达式实验时间2019.11.5实验目的 通过实验,学会根据布尔表达式实现与其对应的数字电路实验环境 Win7,Vivado14.2实验内容及步骤(含电路原理图/Verilog程序、管脚分配、仿真结果等;扩展内容也列入本栏) 实验内容及步骤:1.分析表达式,A 、 B 、 C 作为电路的输入信号2.化简后 = +3.根据方程可知,仅需要 IP 核中的 or_gate和 not_gate4.创建新的工程,加载 IP 核 5.创建原理图,进行原理设计 a)在 Project Navigator 下的 IP Integrator 目录下,点击 Create Block Design,创建原理图 b)保持默认,点击 OK 完成创建 c)在 Diagram 中通过添加 IP 来添加逻辑门电路 (接上)实验内容及步骤(含电路原理图/Verilog程序、管脚分配、仿真结果等;扩展内容也列入本栏)电路原理图:6.右击 Block_Designs

2、中的 design_1,先点击“Generate Output Products”,然后点击 “Create HDL Wrapper” 7.打开 Elaborated Design,配置管脚约束(I/O PLANNING)8.综合、实现、生成 bitstream 9.完成板级验证仿真图:说明:A输入高电平(1),B输入低电平(2),LED灯亮起,符合布尔表达式,板级验证成功。实验结果分析拨动最右端的两个拨码开关 SW1 和 SW0,观察 LED 灯 LD0 的明亮情况。板级验证结果符合实验题目给出的布尔表达式,实验成功。实验方案的缺陷及改进意见 本实验为熟悉平台的基础实验,实验方案无明显缺陷,无改进意见心得体会、问题讨论心得体会:学会了采用模块化的设计流程,通过调用已经写好的模块设计数字 电路,初步熟悉了 Vivado 平台,掌握了创建与外界相连端口的两种方式,创建新工程时不能使用中文路径问题讨论:Vivado 要求模块的输入引脚(左侧)必须都有一个端口,而输出引脚则不必指导老师评 议 成绩评定: 指导教师签名:实验报告说明 数字逻辑课程组实验名称 列入实验指导书相应的实验题目。实验目的 目的要明确,要抓住重点,可以从理论和实践两个方面考虑。可参考实验指导书的内容。在理论上,验证所学章节相关的真值表、逻辑表达式或逻辑图的实际应用,以使实验者获得深刻和系统的理解,在实践上,掌握使用软件平台及设计的技能技巧。一般需说明是验证型实验还是设计型实验,是创新型实验还是综合型实验。实验环境 实验用的软硬件环境(配置)。实验内容(含电路原理图/Verilog程序、管脚分配、仿真结果等;扩展内容也列入本栏) 这是实验报告极其重要的内容。这部分要写明经过哪几个步骤。可画出流程图,再配以相应的文字说明,这样既可以节省许多文字说明,又能使实验报告简明扼要,清楚明白。实验结果分析 数字逻辑的设计与实验结果的显示是否吻合,如出现异常,如何修正并得到正确的结果。实验方案的缺陷及改进意见 在实验过程中发现的问题,个人对问题的改进意见。心得体会、问题讨论 对本次实验的体会、思考和建议。

《四川大学数字逻辑实验报告2》由会员Ide****t钰分享,可在线阅读,更多相关《四川大学数字逻辑实验报告2》请在金锄头文库上搜索。

中华文化课考卷

seminar大学生饮食习惯分析

四川大学近现代史纲要期末论文

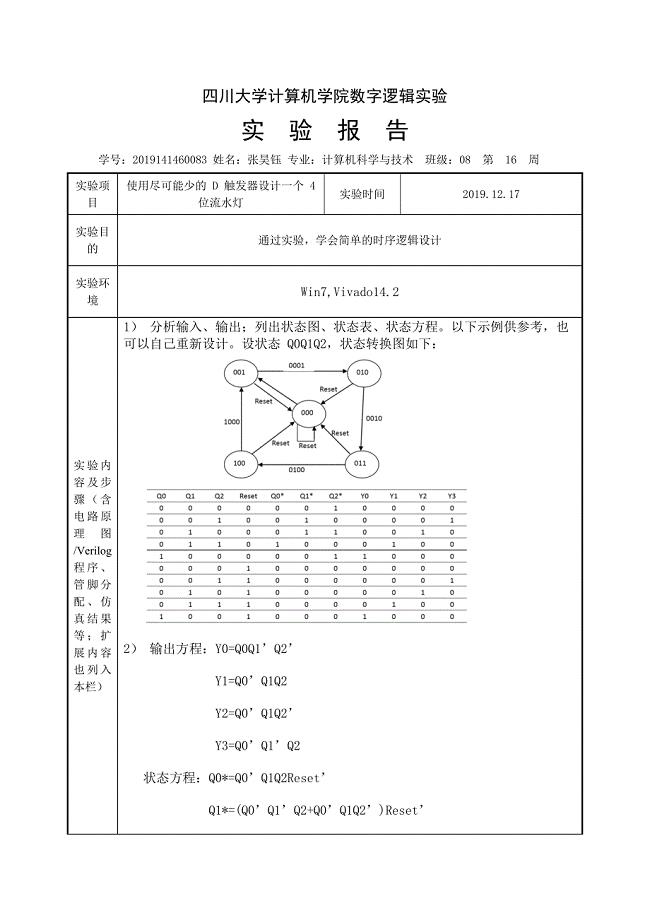

四川大学数字逻辑实验报告6

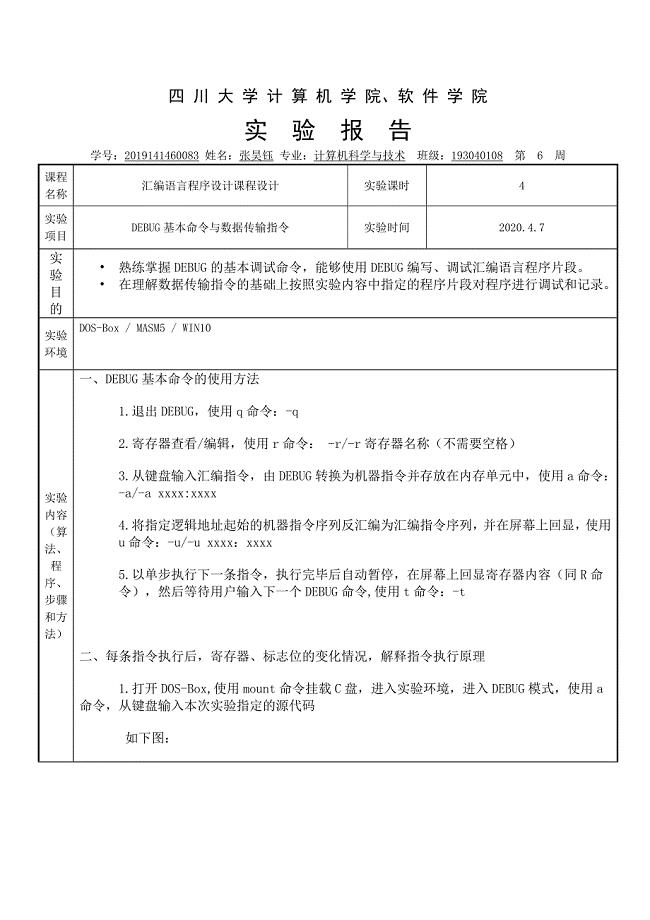

四川大学汇编程序设计第四次实验报告

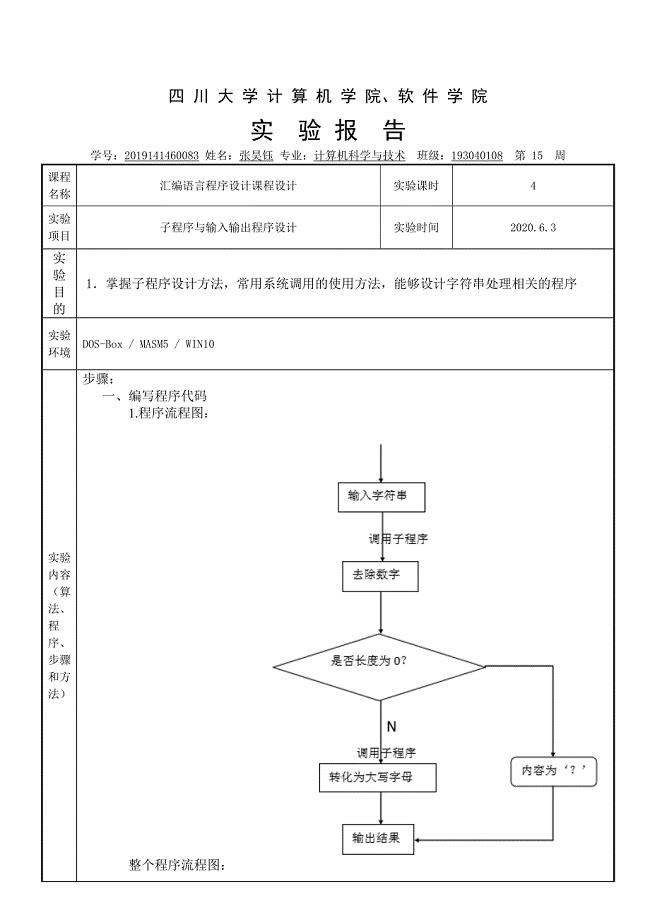

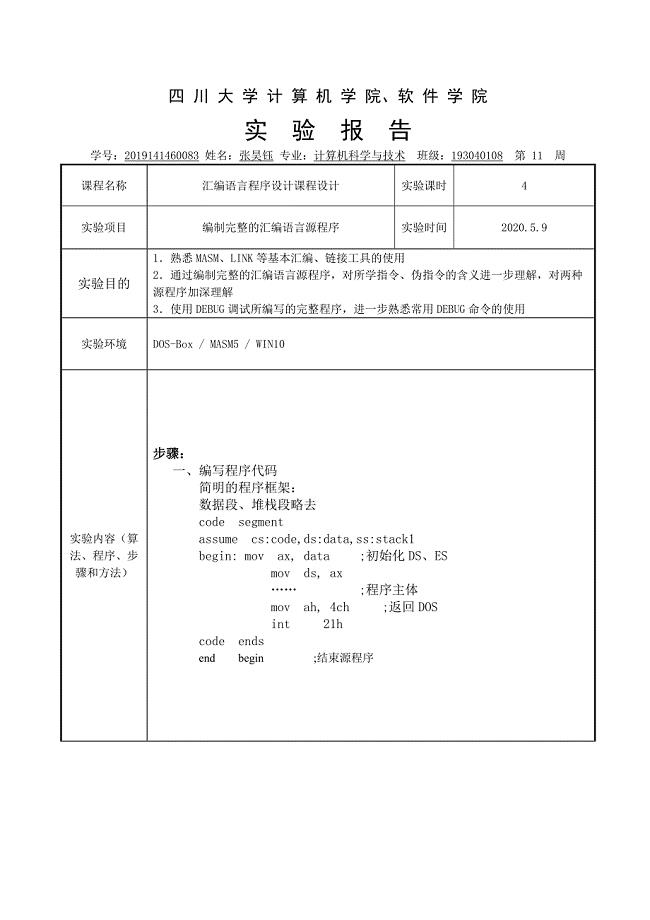

四川大学汇编程序设计第五次实验报告

四川大学汇编程序设计第一次实验报告

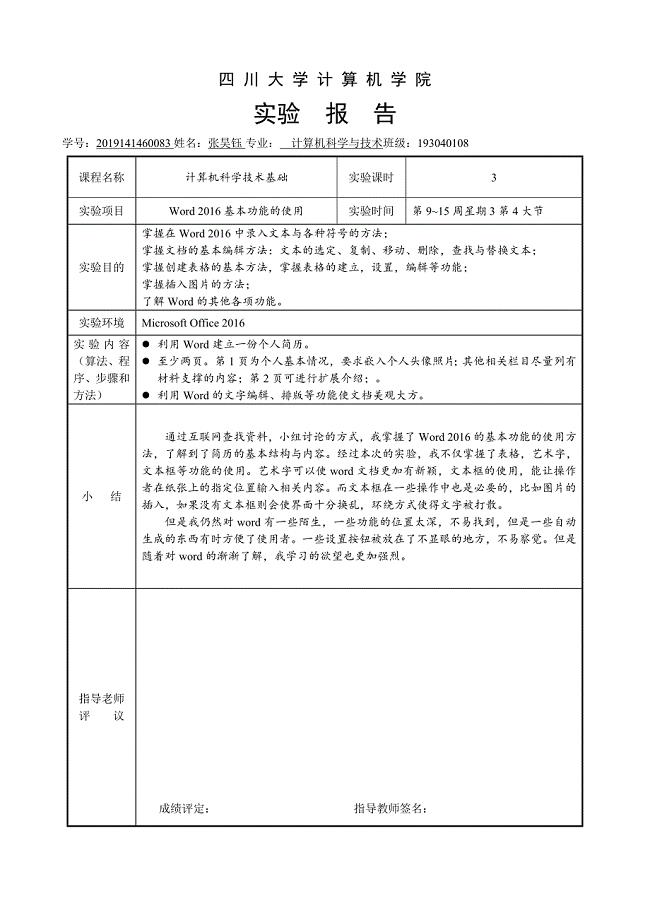

四川大学计算机导论实验报告

四川大学数字逻辑实验报告8

四川大学汇编程序设计第二次实验报告

四川大学汇编程序设计第三次实验报告

四川大学数字逻辑实验报告7

四川大学数字逻辑实验报告3

四川大学数字逻辑实验报告5

四川大学数字逻辑实验报告4

四川大学数字逻辑实验报告1

四川大学数字逻辑实验报告2

四川大学计算机学院新生研讨课报告增强现实技术(2)

四川大学计算机学院新生研讨课报告期末报告(4)

四川大学计算机学院新生研讨课报告自然语言处理(3)

《工程数据分析》-课程教学大纲

《工程数据分析》-课程教学大纲

2024-01-10 5页

郑州市某公司多层现浇钢筋混凝土框架结构办公楼设计

郑州市某公司多层现浇钢筋混凝土框架结构办公楼设计

2023-11-12 92页

人工智能未来发展和技术创新

人工智能未来发展和技术创新

2023-09-04 3页

AI人工智能时代:个人如何应对时代变化

AI人工智能时代:个人如何应对时代变化

2023-09-04 2页

AI大模型资源和设计模型

AI大模型资源和设计模型

2023-09-04 2页

e趣购app的设计与实现毕业设计

e趣购app的设计与实现毕业设计

2023-08-29 51页

乡机勃勃智慧农场互动云平台的设计与实现毕业设计

乡机勃勃智慧农场互动云平台的设计与实现毕业设计

2023-08-29 53页

大语言模型及代码

大语言模型及代码

2023-08-14 4页

常见的Vue面试题及答案

常见的Vue面试题及答案

2023-08-14 5页

程序员简历模板-精美面试模板(墙裂推荐)

程序员简历模板-精美面试模板(墙裂推荐)

2023-08-14 1页