基于Verilog的UART模块的设计课程设计

27页1、 电子课程设计实践报告题 目:基于Verilog的UART模块的设计 班 级: 信科07-4班 学 号: 08073653 姓 名: 姚万华 指导教师: 孙统风 中国矿业大学计算机学院2010-6-2摘 要UART(即 Universal Asynchronous Receiver Transmitter通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。通过应用 EDA技术,基于 CPLD/ FPGA器件设计与实现 UART的波特率产生器、UART发送器和接收器及其整合电路,目的是熟练运用 Verilog HD语言,掌握 CPLD芯片的使用。波特率发生器、接收器和发送器是UART的三个核心功能模块,利用Verilog HDL语言对这三个功能模块进行描述并加以整合,通过MaxPlusII10.01仿真,用串口调试助手进行验证,其结果完全符合UART协议的要求和预期的结果。关键词:UART;串行通讯;VerilogHDL;CPLD;仿真目 录第1章 课题概述31.1 课题背景21.2 课题目的与意义21.3 报告组织结构2第2章 相关理论与技术32.1

2、 UART相关内容简介32.1.1复杂可编程逻辑器件CPLD简介32.1.2 RS-232介绍32.1.3 VerilogHDL简介62.2 UART协议介绍62.3 硬件结构设计82.4软件设计9第3章 课题详细设计与实现93.1UART的整体设计93.2 波特率发生器113.2.波特率的分频因子的计算113.3 接收模块设计133.3.1接收模块原理133.3.2接收模块的源程序143.4 发送模块设计53.4.1发送模块设计原理53.4.2发送模块源程序63.5功能的测试11结 论11参考文献1210第1章 课题概述1.1 课题背景UART协议是数据通信及控制系统中广泛使用的一种全双工串行数据传输协议,在实际工业生产中有时并不使用UART的全部功能。只需将其核心功能集成即可。波特率发生器、接收器和发送器是UART的三个核心功能模块,利用Vefilog-HDL语言对这三个功能模块进行描述并加以整合UART(即Universal AsynchronousReceiver Transmitter 通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。串

3、行外设用到RS232-C异步串行接口,一般采用专用的集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL或Veriolog -HDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。1.2 课题目的与意义实际应用上,有时我们不需要使用完整的UART的功能和这些辅助功能。使用Verilog-HDL将所需要的UART的核心功能集成到FPGACPLD内部,就可以实现紧凑、稳定且可靠的UART数据传输。这样,既可以满足实际的应用,实现所要求的简单的通信和控制,又能够去除更多不需要的繁杂复杂的功能实现。1.3 报告组织结构第一章介绍课题的背景目的及意义,同时介绍了整个课题报告的组织形式。第二章介绍UART协议和硬件结构;以及RS232的简要介绍。简要介绍了课题所用

4、的语言Verilog HDL语言。第三章是课题的详细设计,分为波特率分频因子的计算,接收模块和发送模块。每一部分分为设计原理和源程序。最后是结论和参考文献。第2章 相关理论与技术2.1 UART相关内容简介2.1.1复杂可编程逻辑器件CPLD简介CPLD是 Complex PLD的简称, 顾名思义, 其是一种较PLD为复杂的逻辑元件。CPLD是一种整合性较高的逻辑元件。由于具有高整合性的特点, 故其有性能提升, 可靠度增加,PCB面积减少及成本下降等优点。CPLD元件,基本上是由许多个逻辑方块(Logic Blocks) 所组合而成的。而各个逻辑方块均相似于一个简单的PLD元件( 如 22V10) 。逻辑方块间的相互关系则由可变成的连线架构, 将整个逻辑电路合成而成。常见的CPLD元件有 Altera 公司的Max5000 及Max7000 系列。Cypress的 Max340 及Flash370 系列等, 一般来说, CPLD元件的逻辑门数约在10007000 门之间。【1】2.1.2 RS-232介绍RS232接口,就是普通电脑后面那个串口.一般为9针的,也有25针的.是1970年

《基于Verilog的UART模块的设计课程设计》由会员桔****分享,可在线阅读,更多相关《基于Verilog的UART模块的设计课程设计》请在金锄头文库上搜索。

电动力学复习题

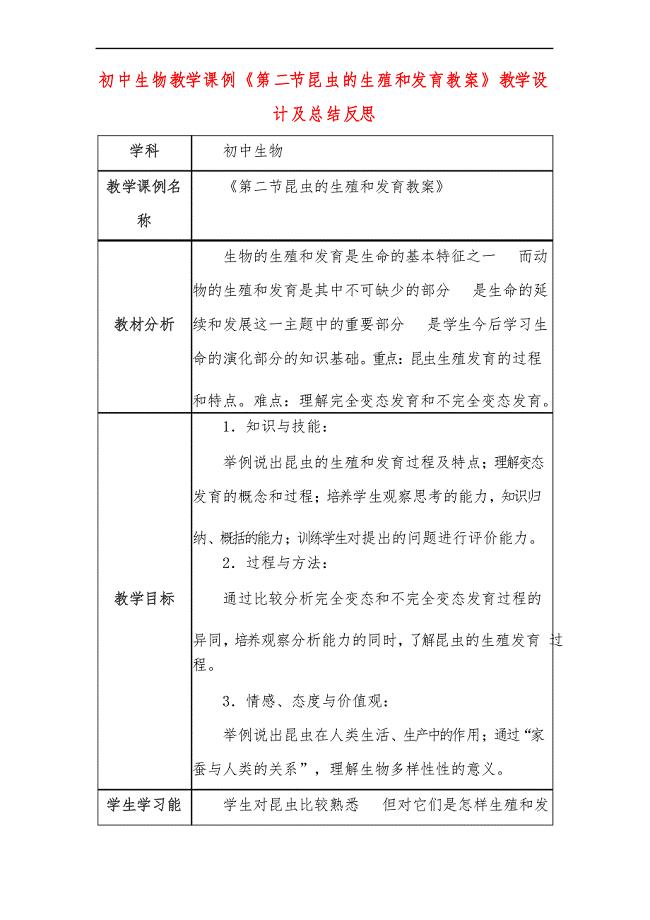

初中生物教学课例《第二节昆虫的生殖和发育教案》课程思政核心素养教学设计及总结反思

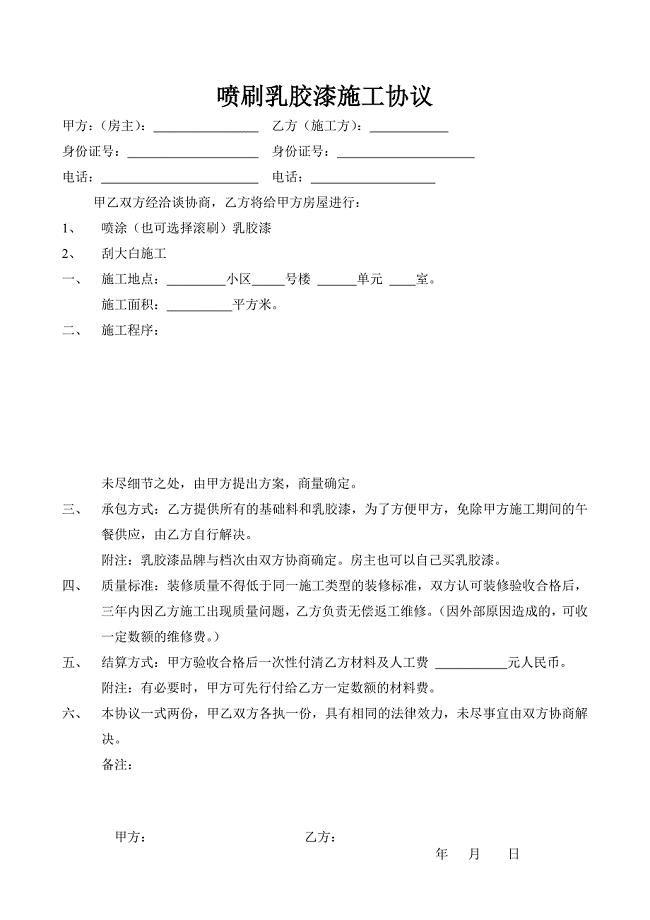

喷刷乳胶漆施工协议

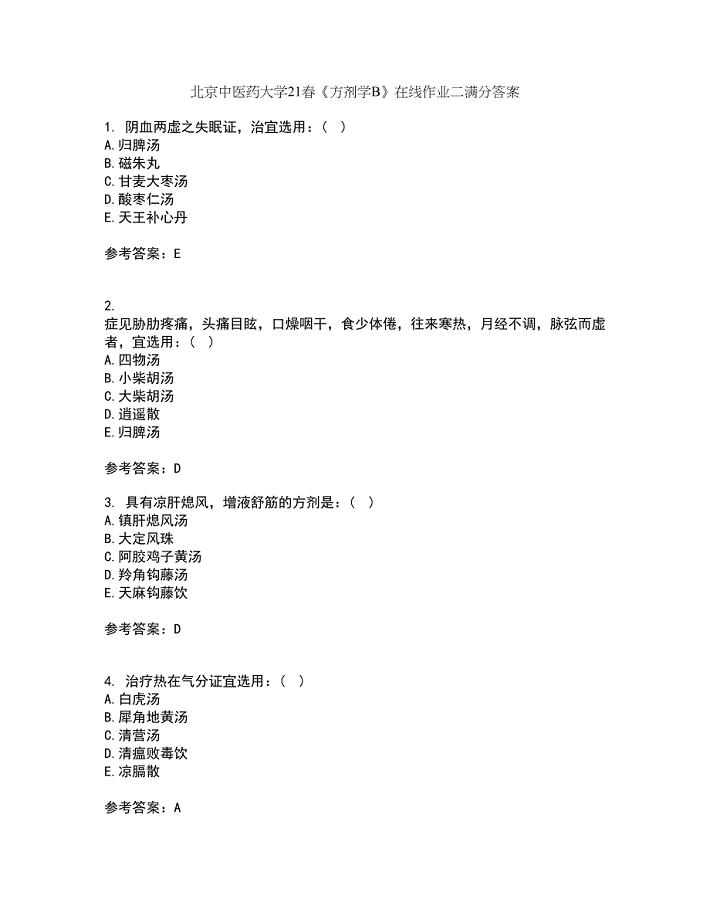

北京中医药大学21春《方剂学B》在线作业二满分答案_27

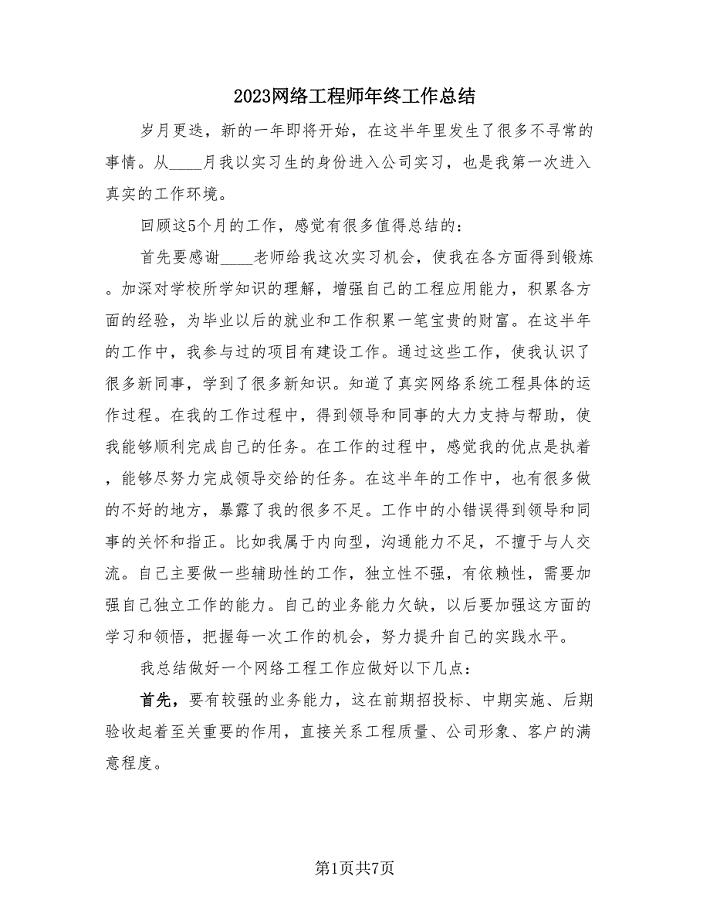

2023网络工程师年终工作总结(3篇).doc

寒假学习计划集合九篇.doc

初中2023-2024学年第一学期总务处工作计划范文(二篇).doc

2022年民办学校年检工作总结

个人房屋租赁热门协议格式范本(10篇)

利用环己酮副产X油制备邻苯基苯酚(OPP)立项报告.doc

班主任教育方法

2023年企业员工培训管理规章制度范本员工培训管理制度范本

宋朝服饰特点

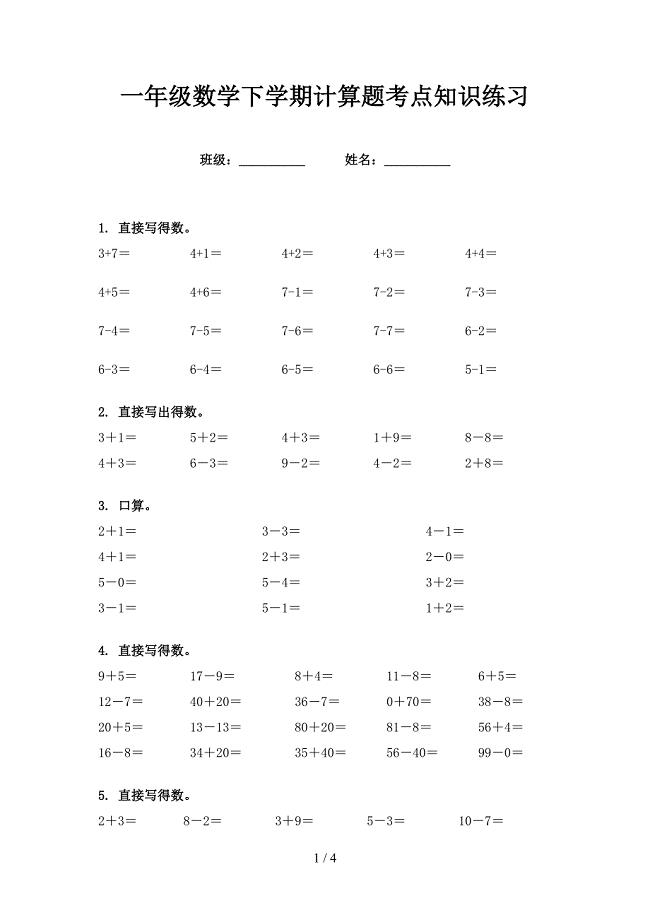

一年级数学下学期计算题考点知识练习

上半年工作总结及下半年计划标准范本(2篇).doc

地铁盾构法施工事故预防及处理措施

2022特岗教师考试(全能考点剖析)名师点拨卷含答案附答案72

![[最新]中考语文辽宁省复习考点跟踪突破32 人物与写作手法](https://union.152files.goldhoe.com/2023-10/20/378906c1-35b0-4c66-844c-aaedbf247ad9/pic1.jpg)

[最新]中考语文辽宁省复习考点跟踪突破32 人物与写作手法

举报奖励制度

2021年护士长工作述职报告范文3篇

儿童节主持词范文合集9篇【精选】

儿童节主持词范文合集9篇【精选】

2022-12-06 25页

监理平行检验方案

监理平行检验方案

2022-07-28 90页

甲乙双方签订的公路运输合同范本集锦.doc

甲乙双方签订的公路运输合同范本集锦.doc

2024-01-25 104页

以拥抱自然的作文高一

以拥抱自然的作文高一

2023-11-22 8页

心理健康教育的个人心得体会范文

心理健康教育的个人心得体会范文

2023-02-20 22页

2021伤感文案

2021伤感文案

2023-04-18 10页

寒假学习计划集合九篇.doc

寒假学习计划集合九篇.doc

2023-04-05 20页

出租土地合同.doc

出租土地合同.doc

2023-07-15 12页

2022客服述职报告合集10篇

2022客服述职报告合集10篇

2023-04-29 39页

给老师的介绍信范文汇编7篇

给老师的介绍信范文汇编7篇

2023-10-18 9页