PCB布线中的微带线和带状线设计

5页1、PCB布线中的微带线和带状线到底是哪个部分啊?1 特性阻抗 近年来,在数字信号速度日渐增快的情况下,在印制板的布线时,还应考虑电磁波和有关方波传播的问题。这样,原来简单的导线,逐渐转变成高频与高速类的复杂传输线了。 在高频情况下,印制板(PCB)上传输信号的铜导线可被视为由一连串等效电阻及一并联电感所组合而成的传导线路,如图1所示。只考虑杂散分布的串联电感和并联电容的效应,会得到以下公式: 式中Z0即特性阻抗,单位为。 PCB的特性阻抗Z0与PCB设计中布局和走线方式密切相关。影响PCB走线特性阻抗的因素主要有:铜线的宽度和厚度、介质的介电常数和厚度、焊盘的厚度、地线的路径、周边的走线等。 在PCB的特性阻抗设计中,微带线结构是最受欢迎的,因而得到最广泛的推广与应用。最常使用的微带线结构有4种:表面微带线(surface microstrip)、嵌入式微带线(embedded microstrip)、带状线(stripline)、双带线(dual-stripline)。下面只说明表面微带线结构,其它几种可参考相关资料。表面微带线模型结构如图2所示。 Z0的计算公式如下: 对于差分信号,

2、其特性阻抗Zdiff修正公式如下: 公式中: PCB基材的介电常数; bPCB传输导线线宽; d1PCB传输导线线厚; d2PCB介质层厚度; D差分线对线边沿之间的线距。 从公式中可以看出,特性阻抗主要由、b、d1、d2决定。通过控制以上4个参数,可以得到相应的特性阻抗。 2 信号完整性(SI) SI是指信号在电路中以正确的时序和电压作出响应的能力。如果电路中的信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。反之,当信号不能正常响应时,就出现了信号完整性问题。从广义上讲,信号完整性问题主要表现为5个方面:延迟、反射、串扰、同步切换噪声和电磁兼容性。 延迟是指信号在PCB板的导线上以有限的速度传输,信号从发送端发出到达接收端,其间存在一个传输延迟。信号的延迟会对系统的时序产生影响。在高速数字系统中,传输延迟主要取决于导线的长度和导线周围介质的介电常数。 当PCB板上导线(高速数字系统中称为传输线)的特征阻抗与负载阻抗不匹配时,信号到达接收端后有一部分能量将沿着传输线反射回去,使信号波形发生畸变,甚至出现信号的过冲和下冲。如果信号在传输线上来回反射,就会产

3、生振铃和环绕振荡。 由于PCB板上的任何两个器件或导线之间都存在互容和互感,因此,当一个器件或一根导线上的信号发生变化时,其变化会通过互容和互感影响其它器件或导线,即串扰。串扰的强度取决于器件及导线的几何尺寸和相互距离。 信号质量表现为几个方面。对于大家熟知的频率、周期、占空比、过冲、振铃、上升时间、下降时间等,在此就不作详细介绍了。下面主要介绍几个重要概念。 高电平时间(high time),指在一个正脉冲中高于Vih_min部分的时间。 低电平时间(low time),指在一个负脉冲中低于Vil_max部分的时间,如图3所示。 建立时间(setup time),指一个输入信号(input signal)在参考信号(reference signal)到达指定的转换前必须保持稳定的最短时间。 保持时间(hold time),是数据在参考引脚经过指定的转换后,必须稳定的最短时间,如图4所示。 建立时间裕量(setup argin),指所设计系统的建立时间与接收端芯片所要求的最小建立时间的差值。 保持时间裕量(hold argin),指所设计系统的保持时间与接收端芯片所要求的最小保持时间之

4、间的差值。 时钟偏移(clock skew),指不同的接收设备接收到同一时钟驱动输出之间的时间差。 Tco(time clock to output,时钟延迟),是一个定义包括一切设备延迟的参数,即Tco=内部逻辑延迟 (internal logic delay) + 缓冲器延迟(buffer delay)。 最大经历时间(Tflightmax),即final switch delay,指在上升沿,到达高阈值电压的时间,并保持高电平之上,减去驱动所需的缓冲延迟。 最小经历时间(Tflightmin),即first settle delay,指在上升沿,到达低阈值电压的时间,减去驱动所需的缓冲延迟。 时钟抖动(clock jitter),是由每个时钟周期之间不稳定性抖动而引起的。一般由于PLL在时钟驱动时的不稳定性引起,同时,时钟抖动引起了有效时钟周期的减小。 串扰(crosstalk)。邻近的两根信号线,当其中的一根信号线上的电流变化时(称为aggressor,攻击者),由于感应电流的影响,另外一根信号线上的电流也将引起变化(称为victim,受害者)。 SI是个系统问题,必须用系统观

《PCB布线中的微带线和带状线设计》由会员壹****1分享,可在线阅读,更多相关《PCB布线中的微带线和带状线设计》请在金锄头文库上搜索。

巩固发展创建文明城市工作情况汇报

留守儿童帮扶计划书

药品补充申请办事指南优秀范文五篇

初级银行从业《风险管理》考前(难点+易错点剖析)押密卷答案参考90

新教材八年级数学上册 1.1.1 探索勾股定理教学案北师大版

2023年农村房屋转让合同(份范本)

驾驶员年终工作总结范本(5篇).doc

2022年11月广东外语外贸大学门诊部公开招聘1名非事业编制工作人员笔试参考题库(答案解析)

购买土地合同样本(九篇).doc

小学一年级下学期少先队工作总结

小学六年级数学列方程解稍复杂的分数应用题教案

县领导城市管理会议讲话模板(2篇)

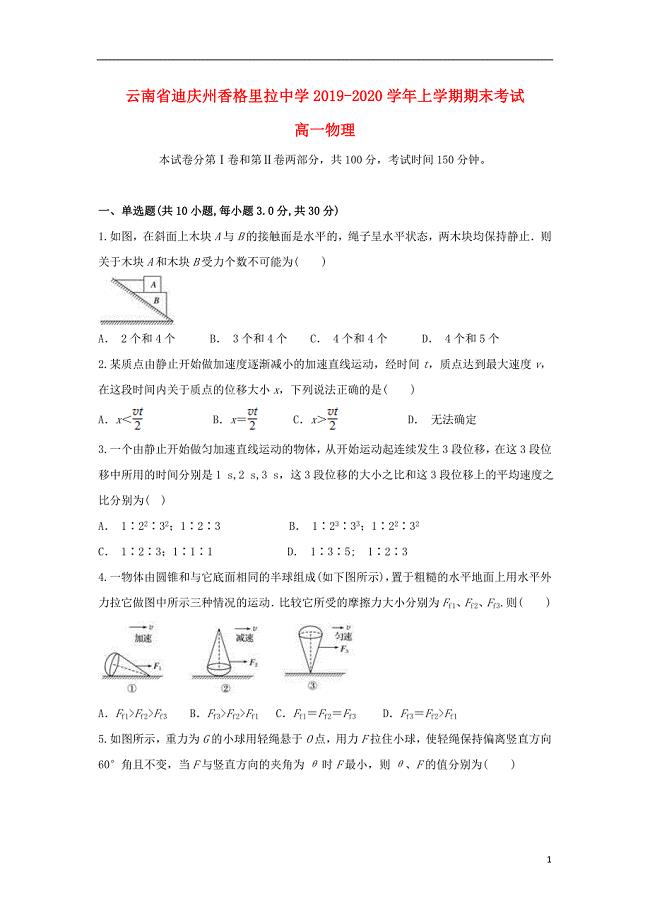

云南省迪庆州香格里拉中学2019-2020学年高一物理上学期期末考试试题

环保的工作总结范文5篇

黑龙江医保服务项目可研报告【参考模板】

临水临电专项施工方案

二手车买卖合同协议书范文(六篇)

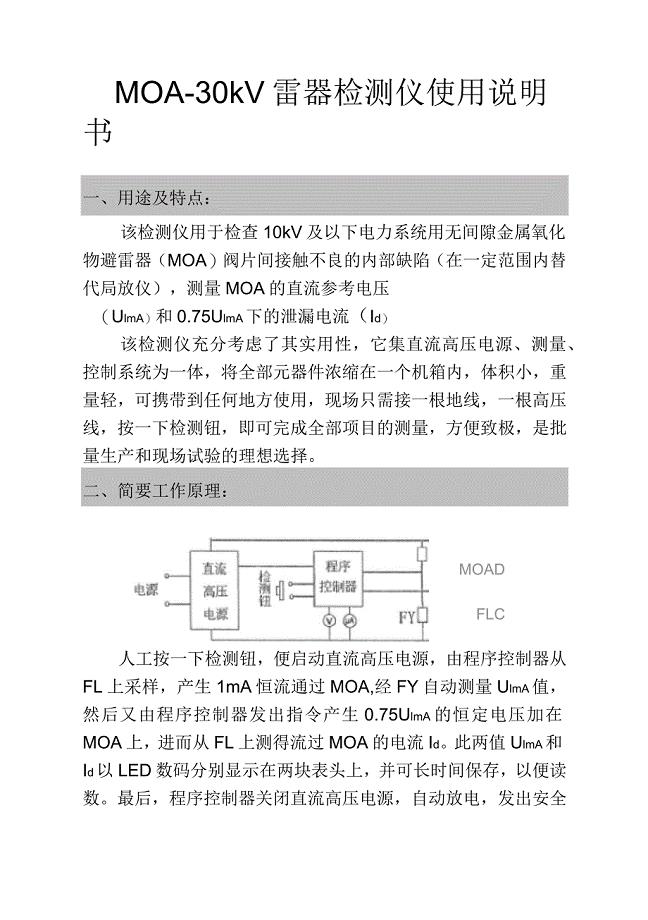

MOA-30KV避雷器检测仪使用说明书

开幕式表演解说词

×××农电局供电所制度

简洁完整的企业入离职流程图

简洁完整的企业入离职流程图

2023-12-06 3页

药物过敏抢救流程

药物过敏抢救流程

2023-08-14 2页

玻璃工程质量通病和预防

玻璃工程质量通病和预防

2022-09-14 2页

常用的工程单位换算表

常用的工程单位换算表

2023-06-29 9页

物理学在工程技术上的运用

物理学在工程技术上的运用

2023-02-10 7页

酒店PA管理资料

酒店PA管理资料

2023-03-01 16页

工程数学(本)电子导学教案

工程数学(本)电子导学教案

2023-08-07 15页

适航和人为因素题

适航和人为因素题

2023-10-18 33页

安居客网络工程项目实施文档

安居客网络工程项目实施文档

2023-11-17 11页

某城市花园环境景观工程施工组织设计

某城市花园环境景观工程施工组织设计

2022-12-01 24页