数字逻辑第6章习题参考解答

9页1、第6章习题参考解答6-3 画出74x27三输入或非门的德摩根等效符号。解:图形如下6-10 在图X6.9电路中采用74AHCT00替换74LS00,利用表6-2的信息,确定从输入端到输出端的最大时间延迟。解:该图中从输入到输出需要经过6个NAND2;每个NAND2(74AHCT00)的最大时间延迟为9 ns;所以从输入端到输出端的最大时间延迟为:54 ns。6-31 BUT门的可能定义是:“如果A1和B1为1,但A2或B2为0,则Y1为1;Y2的定义是对称的。”写出真值表并找出BUT门输出的最小“积之和”表达式。画出用反相门电路实现该表达式的逻辑图,假设只有未取反的输入可用。你可以从74x00、04、10、20、30组件中选用门电路。解:真值表如下A1B1A2B2Y1Y2A1B1A2B2Y1Y2000000100000000100100100001000101000001101101101010000110010010100110110011000111010011101111100利用卡诺图进行化简,可以得到最小积之和表达式为Y1=A1B1A2+A1B1B2Y2=A1A2B2+B1A

2、2B2Y2采用74x04得到各反相器采用74x10得到3输入与非采用74x00得到2输入与非实现的逻辑图如下:6-32 做出练习题6-31定义的BUT门的CMOS门级设计,可以采用各种反相门逻辑的组合(不一定是二级“积之和”),要求使用的晶体管数目最少,写出输出表达式并画出逻辑图。解:CMOS反相门的晶体管用量为基本单元输入端数量的2倍;对6-31的函数式进行变换:利用圈-圈逻辑设计,可以得到下列结构: 此结构晶体管用量为20只 (原设计中晶体管用量为40只)6-20 采用一片74x138或74x139二进制译码器和NAND门,实现下列单输出或多数出逻辑函数。解:a) b) c) d) e) f) 6-38 假设要求设计一种新的组件:优化的十进制译码器,它只有十进制输入组合。与取消6个输出的4-16译码器相比,怎样使这样的译码器价格降至最低?写出价格最低译码器的全部10个输出的逻辑等式。假设输入和输出高电平有效且没有使能输入。解:设输入为:A,B,C,D,将6个输入组合作为无关项以化简其余输出的乘积项,输出函数卡诺图如下:利用无关项进行最小成本设计,可以得到下列输出函数: 与4-16译

3、码器的前10个输出的实现相比,减少了10个与门输入端,减少了20只晶体管的用量。6-43 采用一片SSI器件(4 x Nand2)和一片74x138,实现下列4个逻辑函数。解: 6-21 图X6.21电路有什么可怕的错误?提出消除这个错误的方法。解:该电路中74x139两个2-4译码器同时使能,会导致2个3态门同时导通,导致输出逻辑电平冲突。为解决这一问题,可将使能端分开,进行反相连接,各自使能,即可消除该错误。6-63设计适合于24引脚IC封装的3输入,5位多路复用器,写出真值表并画出逻辑图和逻辑符号。解:设数据输入A(4.0),B(4.0),C(4.0),数据输出Y(4.0) 选择端S1,S0 则 Y=S1S0A+S1S0B+S1S0C真值表: S1S0Y00d01C10B11A其中Y,A,B,C均为5位总线,S1,S2为单线,加上电源和接地,可以采用24引脚IC封装。逻辑图和逻辑符号如下:6-68 对于图X6.68所示CMOS电路实现的逻辑功能,写出真值表并画出逻辑图(电路包含3.7.1节介绍的传输门)。解:SABZSABZ00001000001010110101110001111111Z=AS Z=SBZ=AS+BS为2选1多路器逻辑图为: 6-24 采用奇数块XNOR门,用图6-70(a)的形式构成某种校验电路,该电路实现什么功能?解:XNOR为XOR增加一个反相圈构成;对于偶数块的连接,利用圈到圈设计可以看到,功能与XOR的连接相同(如下图所示);所以,对于奇数块连接时,输出与对应XOR连接电路正好相反,即得到偶校验电路。6-96 采用3块74x682和必要的门电路设计一个24位比较器,将2个24位的无符号数P和Q进行比较,产生2位输出表达P=Q和PQ。 解:利用3块74x682(8位数值比较器)分别进行高中低3个8位段的比较;将各段的PEQQ_L进行NAND运算,可以得到PEQQ(P=Q);利用下式可以得到PGTQ(PQ):电路连接图如下所示:6-97 设计一个3位相等检测器,该器件具有6个输入端:SLOT2.0和GRANT2.0,一个低电平有效的输出端MATCH_L。利用表6-2,6-3提供的SSI和MSI器件,设计出最短时间延迟的器件。解:采用表6-3的74FCT682,延迟时间为11 ns。器件连接图如下:

《数字逻辑第6章习题参考解答》由会员新**分享,可在线阅读,更多相关《数字逻辑第6章习题参考解答》请在金锄头文库上搜索。

钢材买卖合同参考范本(8篇)

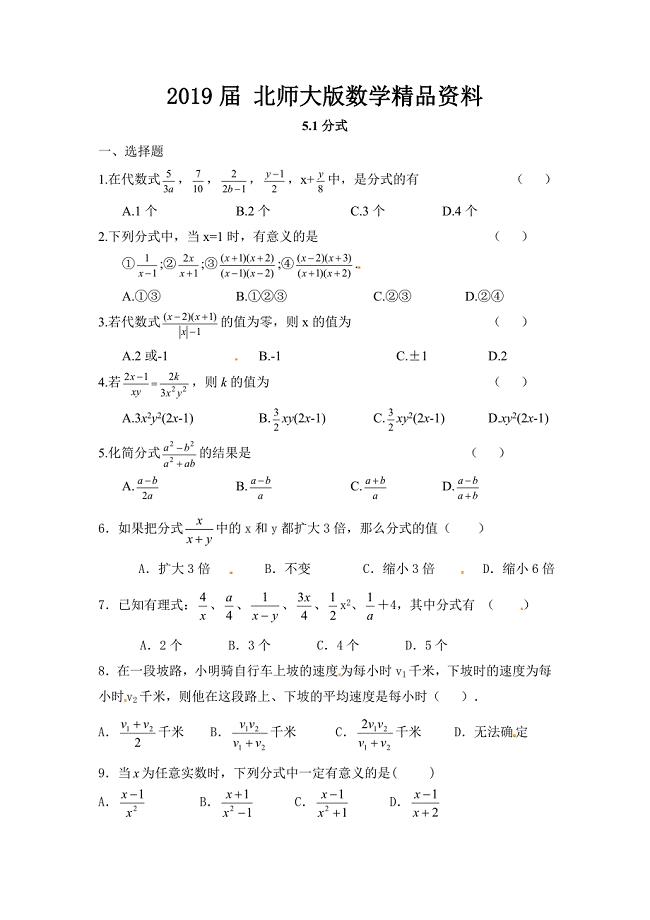

北师大版八年级数学下:5.1分式同步练习含答案

五型班组建设之巡检制度

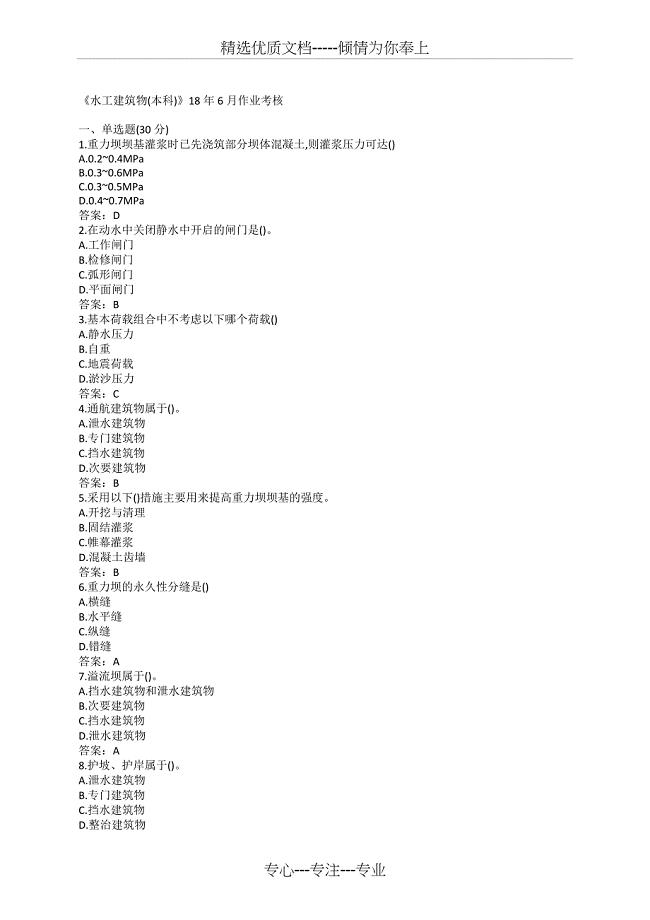

《水工建筑物(本科)》作业

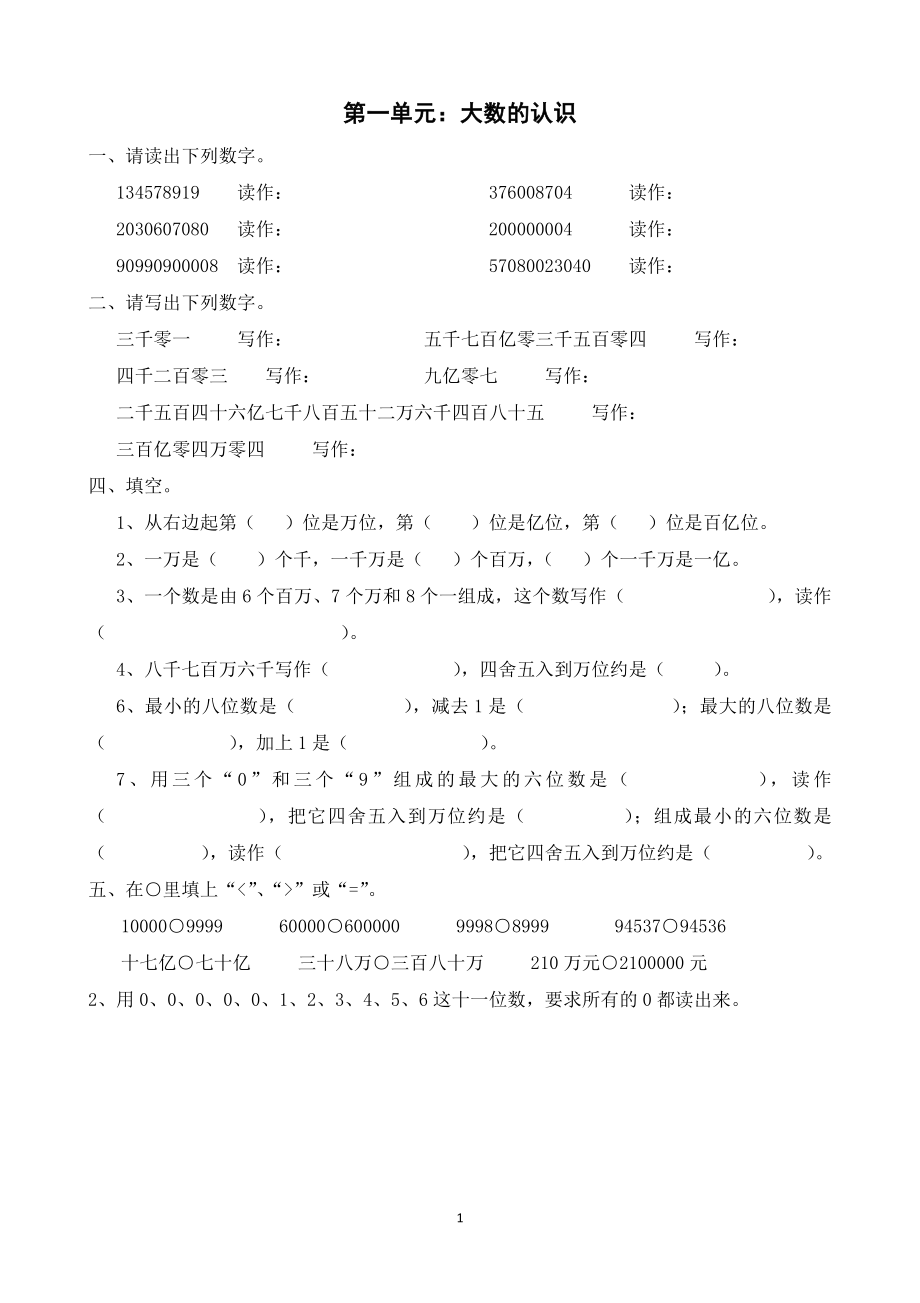

新人教版四年级数学上册全单元测试题及答案【必考题】

2023年家庭助廉倡议书(模板)

建设局实践科学发展观第一阶段学习总结

2023小学班主任下学期工作计划范文(5篇)

医院医疗服务和药品价格管理制度样本(3篇).doc

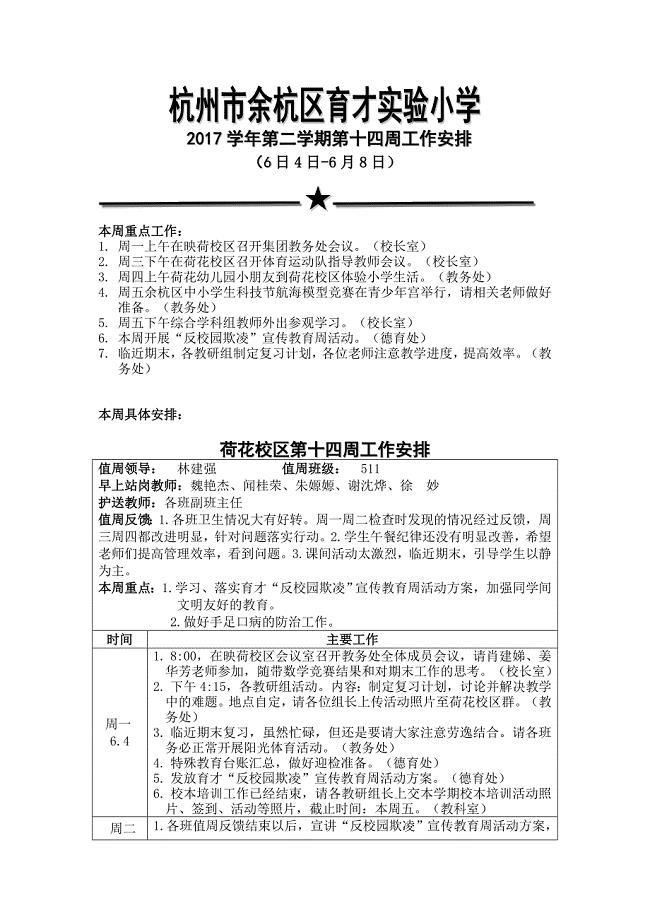

杭州余杭区育才试验小学

初一的老师作文合集十篇

梧州医疗美容产品项目商业计划书(模板范本)

梦想起航学生演讲稿

化工生产实习心得

在×房产开盘仪式仪式上的致辞

大学有机实验心得总结5篇

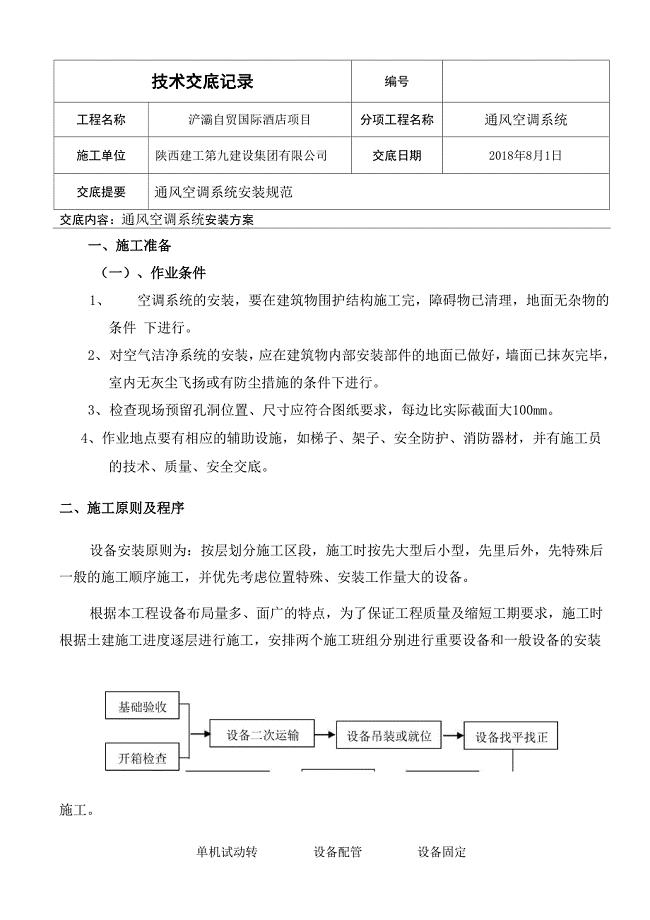

空调系统安装技术交底

2023年党委工作报告精华版本

物联网(IOT)简介

物业管理工作计划

2023年宣传委员工作总结和计划

2023年宣传委员工作总结和计划

2023-03-04 2页

华中师范大学22春《企业战略管理》补考试题库答案参考64

华中师范大学22春《企业战略管理》补考试题库答案参考64

2023-08-09 13页

2023年江西省九江市共青城市甘露镇林场生活区社区工作人员考试模拟题含答案

2023年江西省九江市共青城市甘露镇林场生活区社区工作人员考试模拟题含答案

2023-07-15 22页

质量管理全新体系

质量管理全新体系

2022-11-09 61页

2023年06月甘肃医学院招考聘用20人笔试题库含答案带解析

2023年06月甘肃医学院招考聘用20人笔试题库含答案带解析

2022-10-19 68页

2023年06月2023年浙江金华浦江县部分事业单位招考聘用37人笔试题库含答案解析

2023年06月2023年浙江金华浦江县部分事业单位招考聘用37人笔试题库含答案解析

2023-01-15 70页

2023年公选《专业科目》考试全真模拟易错、难点汇编第五期(含答案)试卷号:18

2023年公选《专业科目》考试全真模拟易错、难点汇编第五期(含答案)试卷号:18

2024-01-28 16页

未成年人思想道德建设测评模拟调查问卷答案

未成年人思想道德建设测评模拟调查问卷答案

2023-08-16 6页

东北财经大学21秋《国际财务管理》在线作业三答案参考74

东北财经大学21秋《国际财务管理》在线作业三答案参考74

2023-01-20 14页

福建师范大学21春《小学科学教育》离线作业2参考答案44

福建师范大学21春《小学科学教育》离线作业2参考答案44

2024-01-01 11页