第3章存储器及存储系统(详细版)

29页1、第三章主存储器及其组织3.1存储器概述3.2主存储器3.3半导体存储器芯片3.4主存储器组织3.5存储保护和校验技术3-1存储器概述计算机之所以能够脱离人的干预而高速、自动地工作,其中一个必要条件是在计算机中具有一个容量足够大的存储器,程序和程序所用的数据都事先存放在存储器中,由CPU自动地从存储器中取出指令并使之得到执行。存储器对计算机系统的技术、组织、性能和价格等方面都有很大的影响。由于目前计算机部件技术发展的速度不太均衡,处理器的发展速度太快,还没有很完善的满足系统需要的存储技术。一、存储器分类1、按存储介质分类(1)半导体存储器特点:集成度高、容量较大、体积小、速度快、功耗低、价格便宜、维护简单,但断电会丢失。又分两类:双极性存储器(TTL型和BCL型)和金属氧化物半导体存储器(MOS)(分为静态MOS存储器和动态MOS存储器)。(2)磁表面存储器特点:容量与体积大且不易丢失、速度慢,有磁盘存储器、磁带存储器等。(3)激光存储器特点:集上述两种优点。又分三种:只读型光盘(CD-ROM)、只写一次型光盘(WORM)和磁光盘(MOD)。2、按存取方式分类(1)随机存储器(RAM)在

2、存储器中,任何存储单元的内容都能随机存取,且存取时间与存储单元的物理位置无关。主要用于:高速缓冲存储器和主存储器。存放各种榆入/输出的程序、数据、中间结果以及与外界交换的信息。(2)串行访问存储器(SAS)在存储器中,按某种顺序来存取,也就是存取时间与存储单元的物理位置有关。又分为顺序存取存储器(SAM)和直接存取存储器(DAM)主要用于:外部存储器。(3)只读存储器(ROM)读写的状态条件不同,内容预先写入,存放固定不变的信息。又分为掩模ROM(MROM)、可编程ROM(PROM)、可擦除可编程ROM(EPROM和E2PROM)。主要用于:微程序控制器、BIOS等。3、按信息的可保存性分类(1)非永久记忆的存储器断电后信息即消失的存储器(主存中的RAM)。(2)永久记忆性存储器断电后仍能保存信息的存储器(辅存,ROM)o另外还有破坏性读出与非破坏性读出之分。4、按存储器在计算机系统中的作用分类(1)高速缓冲存储器用来存放正在执行的程序段和数据。它的存取速度可以与CPU相匹配,但容量较小、价格较高。(2)主存储器用来存放计算机运行期间所需要的程序和数据,CPU可直接随机地进行读/写访问

3、。(3)辅助存储器用来存放当前暂不参与运行的程序和数据以及一些需要永久性保存的信息。辅存设在主机外部,CPU不能直接访问它。辅存中的信息必须通过专门的程序调入主存后,CPU才能使用。存储器分类综述,内存储器存储器(4)控制存储器“RAM双极型rSRAM-CacheIMOS型jrMROMDRAM、ROMIPROMIEPROMIE2PROM磁盘懿磁带rCD-ROM一光盘1WORMEOD二、存储器的分级管理存储器有三个主要特征:速度、容量和价位,而对存储器的要求是速度快、容量大、位价低。一般说来是:速度越快、位价就越高,容量越大、位价就越低,容量越大、速度必越低;也就是说,对存储器的栗求与各类存储器各具的特点是不统一的。为解决这一矛盾,则采用层次结构的组织形式将各类存储器连接在一起,以发挥各自的特点。1、什么是存储系统两个或两个以上速度、容量和价格各不相同的存储器用硬件或轨件或硬件与软件相结合的方法有机地连接起来的一个集合,其对应用程序员是一个透明的存储器,并具有速度高、容量大、价格低的特性,该存储器集合就称为存储系统。存储器与存储系统是两个完全不同的概念。从外部看:存储周期T-MIN(Tl

4、.T2Tn);存储容量S-MAX(SI、S2、Sn);每位价格CMIN(Cl、C2Cn)。2、存储器层次结构实现的基础程序对存储空间访问有所谓程序访问局部性的特点,包括时间局部性和空间局部性两方面。一是时间局部性,它是指程序在最近的未来要用到信息很可能是现在正在使用的信息。二是空间局的部性,它是指程序在最近的未来要到的信息与现在正在使用的信息很可能在程序空间上是相邻或相近的。3、存储器的层次结构通常采用三级存储器结构:高速缓冲存储器、主存储器和辅助存储器,通常意义的存储器是指主存储器。CPU能直接访问存储器(高速缓冲存储器、主存储器)称为内存储器(内存),不能直接访问称为外存储器(外存)。形成了两个不同层次的存储管理系统:高速缓冲存储系统、虚拟存储系统。但在管理上有不少相同之处。三级存储结构关系图4.存储层次组织的基本操作存储层次间的数据信息的交换存储层次间的地址变换存储空间的替换存储层次间的数据信息一致性的维护三、高速缓冲存储器1 .高速缓冲存储器的功能高速缓冲存储器(Cache)简称快存,介于CPU与主存之间的小容量存储器,可以看作为主存的缓冲存储器,通常采用由高速的双极型半导体存

《第3章存储器及存储系统(详细版)》由会员工****分享,可在线阅读,更多相关《第3章存储器及存储系统(详细版)》请在金锄头文库上搜索。

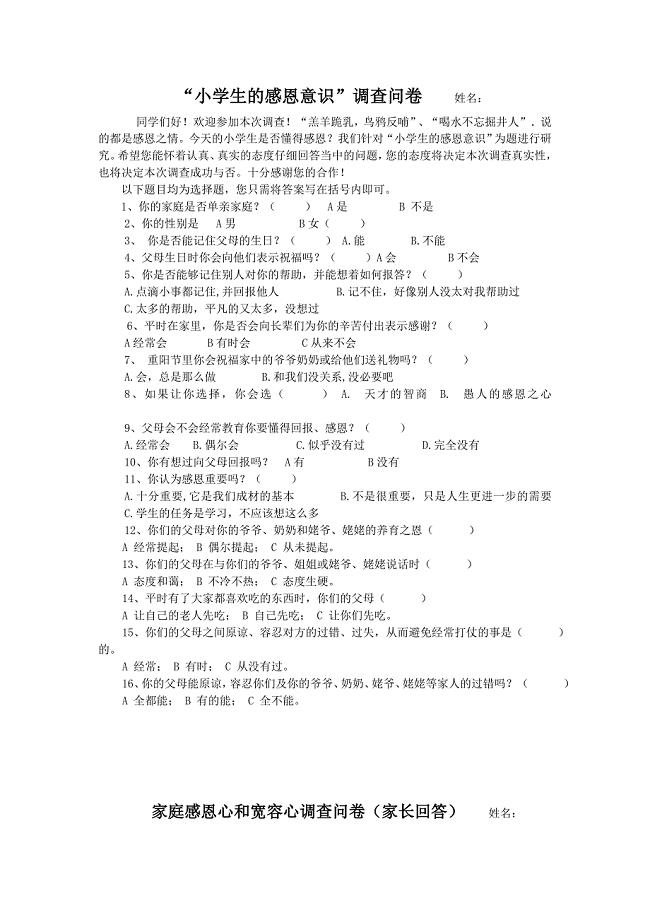

感恩调查问卷

葡萄季施肥的重要性

2023年运输管理制度

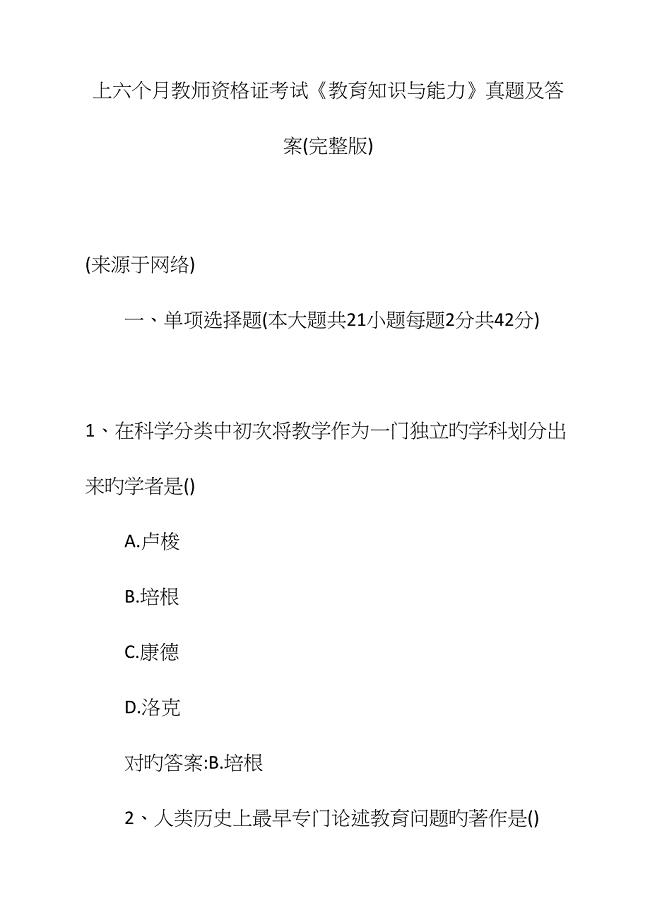

2023年上半年教师资格证考试教育知识与能力模拟真题及答案完整版

高中体育课堂教学

2022小学英语教学计划_15

体能训练教案

预算员考试专业管理实务模拟全考点题库附答案参考24

利用科技创新促进企业发展

南邮MATLAB数学实验答案(全)Word版

公共关系试题库范文

第一季度银保目标任务及全年思路

生产设备控制程序

土方开挖安全专项施工方案

“零缺陷”管理在电网调度中的应用(一)

2022年防灭尘工安全生产岗位责任制

操作工年终工作总结标准范本(二篇).doc

2018年水利水电工程常考题2155

505中医药养生旅游

六年级语文下册 第39课《天时不如地利》教案 上海版(五四制)

变配电工技术比武试题库完整

变配电工技术比武试题库完整

2023-11-18 50页

出售二手房合同

出售二手房合同

2023-03-22 6页

煤矿线路登杆检查及安全措施

煤矿线路登杆检查及安全措施

2023-12-16 10页

新课标高中物理公式大全(版)

新课标高中物理公式大全(版)

2023-03-29 12页

2021年项目委托合同

2021年项目委托合同

2023-06-17 5页

《机械工程控制基础》课后题答案

《机械工程控制基础》课后题答案

2023-10-31 102页

供应运输部门负责人工作责任制度

供应运输部门负责人工作责任制度

2023-06-23 2页

《红领巾真好》教案

《红领巾真好》教案

2023-08-09 6页

中药调剂学知识复习汇总

中药调剂学知识复习汇总

2023-10-29 13页

用友财务软件图文教程

用友财务软件图文教程

2022-09-20 38页