CMOS逻辑门的电压传输特性曲线与TTL逻辑门比较

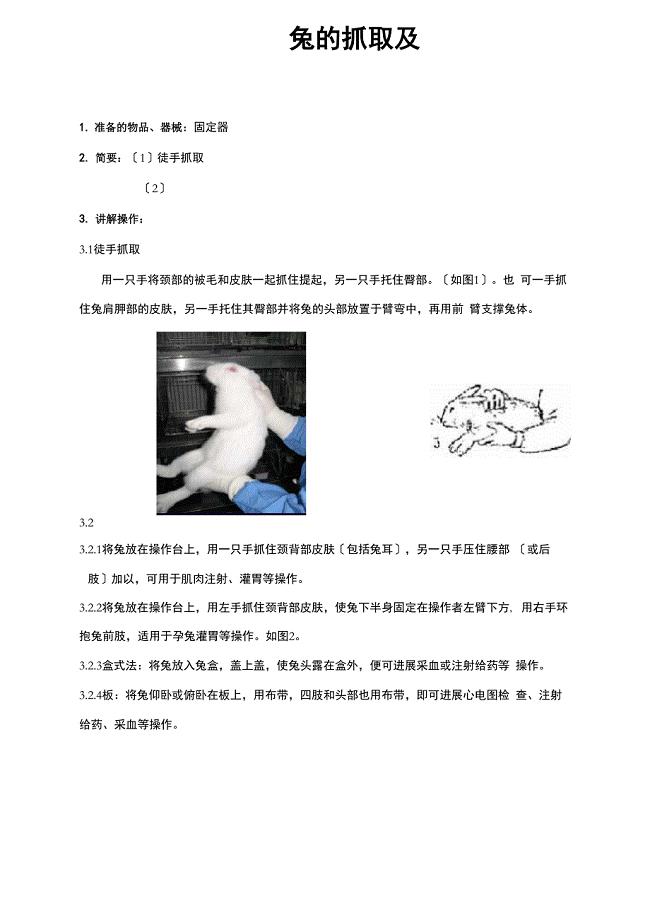

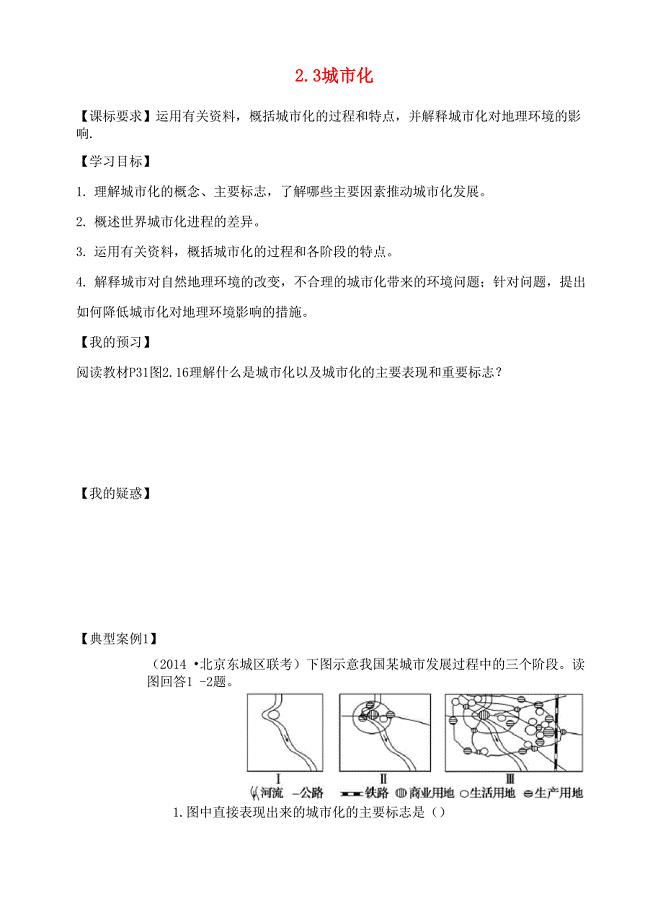

4页1、CMOS逻辑门的电压传输特性曲线与TTL逻辑门比較CMOS 逻辑门的电压传输特性曲线的外形与 TTL 逻辑门的外形相似,如图 18.36 所示,两者相比也有较大不同。CMOS 逻辑门的输出高电平的数值基本上等于电源供电电压值,也就是 说为了获得一个相同的高电平值,对于 CMOS 集成电路所需要的供电电压值要 更小一些,或称之为CMOS集成电路对电源电压的利用率高。在5V供电电压条 件下,CMOS逻辑门的高电平值要比TTL逻辑门高出大约一伏多。CMOS逻辑门的输出低电平的数值基本上等于零,一般小于0.1V, CMOS 逻辑门的低电平值要比TTL逻辑门更低,所以CMOS逻辑门的逻辑摆幅比TTL 逻辑门要大许多。一般条件下,CMOS的高电平比VDD小0.1V,低电平约为0.1V。 不同供电电压条件下,TTL和CMOS逻辑门的逻辑电平的范围如图18-4-4所示。TTL 集成电路的供电电压是 5V, CMOS 集成电路可以有更宽阔的供电 电压范围,可以从一点几伏到二十几伏。低的供电电压和微功耗,有利于便携式 电子仪器。CMOS 逻辑门的阈值电平大约等于电源电压的 50%,一般在电源电压的 45%

2、55%之间。在5V供电电压条件下,CMOS逻辑门的阈值要比TTL逻辑门 的阈值高出大约1V,因此CMOS逻辑门的抗干扰能力要比TTL逻辑门高,特 别是在低电平这一侧。图 18-4-3 CMOS 电压传输特性曲线CMOS逻辑门的缺点是比较容易受到静电的损伤,由于场效应管的栅极源极之间 几乎是绝缘的,电阻十分大,而栅源之间的电容又较小。所以一旦受到静电的影 响,栅源之间会有较高的电压产生,这个电压很可能击穿栅极,使场效应管损坏。 不过现在制造的 MOS 集成电路都有输入保护回路,用以防止静电损伤,但仍应 注意静电的危害。以下两个问题,虽不一定是缺点,需要注意。CMOS 电路的功耗很小是指它的静态功耗很小,动态功耗不一定小。由于静 态功耗极小,所以在 MOS 管的开关过程中,会有 NMOS 管从开到关, PMOS 管从关到开,或 NMOS 管从关到开, PMOS 管从开到关的暂短同时导通的时间, 这样就形成了动态功耗oCMOS电路的动态功耗基本上随工作频率的增加而线性 增加,在静态时,CMOS电路的静态功耗在微瓦数量级,在工作频率达到1MHz 时,可能达到毫瓦数量级。TTL逻辑门和CMOS逻

3、辑门的速度功耗曲线见图 18-4-5。103每门功耗.(mW)3 i i 1 102101.010-110-210-3ECL-510 Q TO-5.2V/TO-2YL、ECl】t5q3STTLlsTTL、CMpS(15V)-CMpS(10V) “CMQS (fV)|cl*5pFU= 0.2V 0.1VNL(HC) DD图 18-4-4 CMOS 和 TTL 逻辑门的逻辑电平10-4102 103 104 105 106 107 108输入频率(Hz)图 18-4-5 速度功耗曲线CMOS 电路既然没有输入电流,那么它的扇出系数是否很大?答案是否定 的。因为从电流的角度,CMOS门是可以带很多很多的门,但从动态的情况看, 带的门越多,输出端的分布电容也越大,相当CL很大,时间常数加大。这就使 输出电压从低电平向高电平变化时,上升沿变慢,限制了该逻辑门的工作速度。 所以 CMOS 电路的扇出也不是十分的大,扇出主要受制于逻辑门的工作速度。 低速时,可以带较多的门,高速工作时,就带不了那么多了。CMOS 逻辑电路CMOS是单词的首字母缩写,代表互补的金属氧化物半导体(Complementar

4、yMetal-Oxide-Semiconductor),它指的是一种特殊类型的电子集成电路(IC)。集成电路是一块微小的硅片, 它包含有几百万个电子元件。术语IC隐含的含义是将多个单独的集成电路集成到一个电路中,产生一个十 分紧凑的器件。在通常的术语中,集成电路通常称为芯片,而为计算机应用设计的IC称为计算机芯片。 虽然制造集成电路的方法有多种,但对于数字逻辑电路而言CMOS是主要的方法。桌面个人计算机、工作 站、视频游戏以及其它成千上万的其它产品都依赖于CMOS集成电路来完成所需的功能。当我们注意到所 有的个人计算机都使用专门的CMOS芯片,如众所周知的微处理器,来获得计算性能时,CMOS IC的重 要性就不言而喻了。CMOS之所以流行的一些原因为:逻辑函数很容易用 CMOS 电路来实现。CMOS 允许极高的逻辑集成密度。其含义就是逻辑电路可以做得非常小,可以制造在极小的面积上。用于制造硅片CMOS芯片的工艺已经是众所周知,并且CMOS芯片的制造和销售价格十分合理。 这些特征及其它特征都为CMOS成为制造IC的主要工艺提供了基础。CMOS可以作为学习在电子网络中如何实现逻辑功能的工具

《CMOS逻辑门的电压传输特性曲线与TTL逻辑门比较》由会员大米分享,可在线阅读,更多相关《CMOS逻辑门的电压传输特性曲线与TTL逻辑门比较》请在金锄头文库上搜索。

兔实验技术操作

森林监控方案

小学寒假实践创意作业

通风部调度员安全生产责任制(2篇)

保安主管年终总结

工作面周期来压分析

某县农委农业资源调研汇报

2023年二级建造师之二建建筑工程实务考前冲刺试卷B卷含答案

内蒙古2015年房地产估价师《理论与方法》:估价报告含义考试试题

学年度第二学期语文教研组工作计划

企业管理管理学整理

《阻断院感注射传播

安防系统改造合同

高中地理 第二章 城市与城市化 2.3 城市化导学案 新人

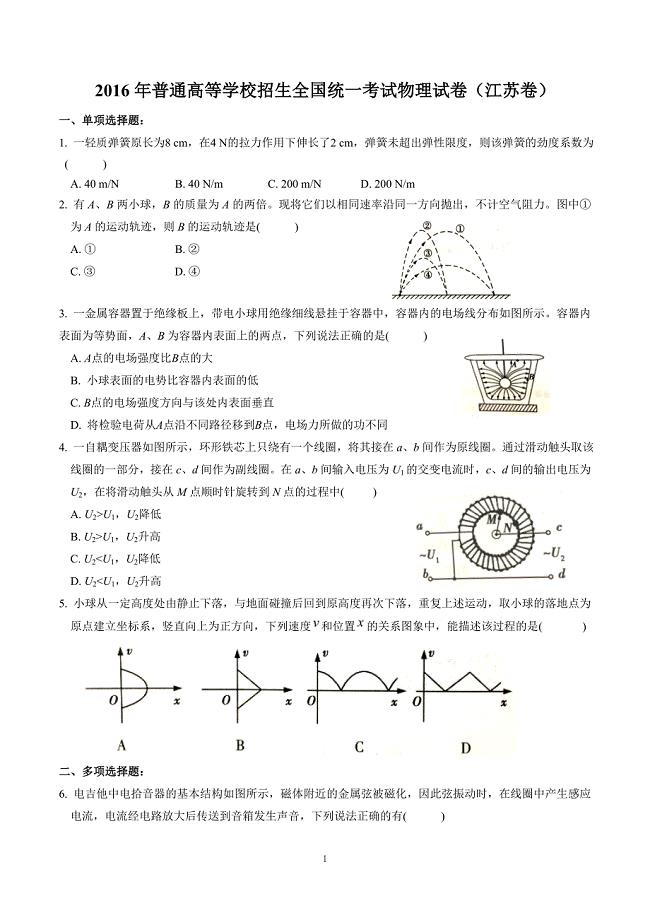

2016年高考物理试卷----江苏卷(高清版)

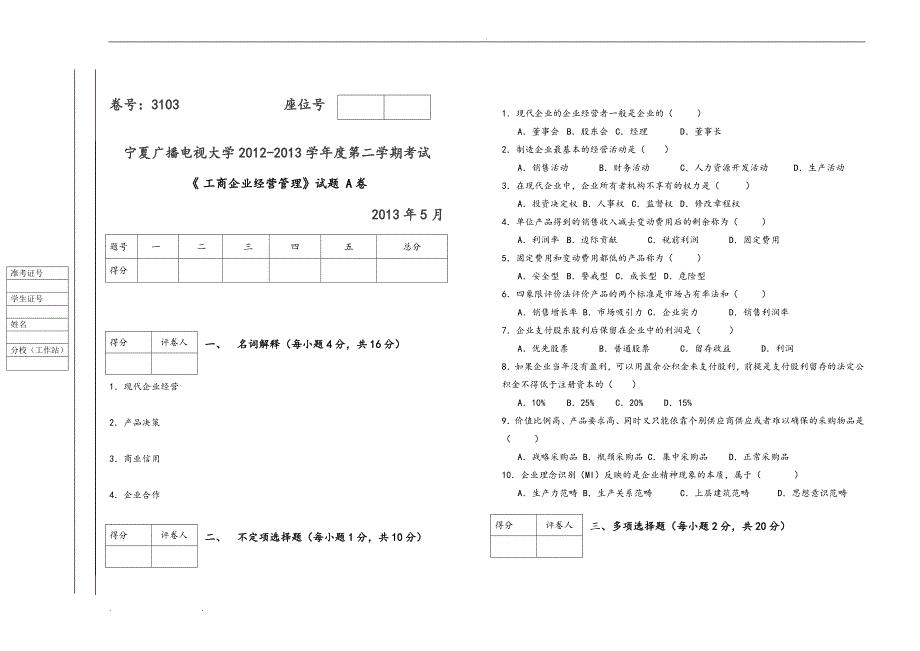

工商企业经营管理试题(A、B)试卷和答案

沟槽开挖、支护专项方案

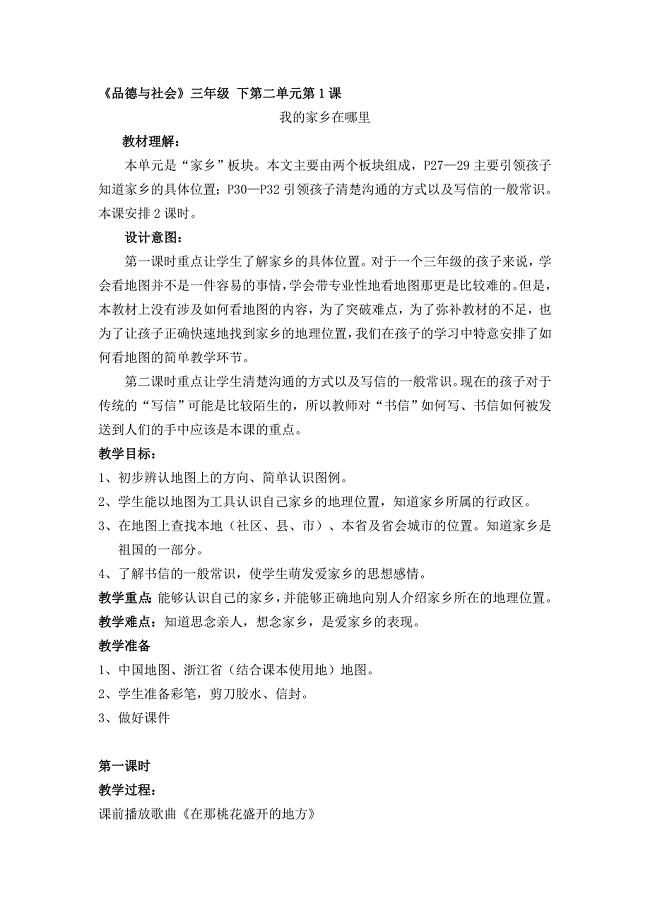

浙教版小学品德与社会三年级下册《我的家乡在哪里》教学设计

商务车租赁协议

中秋节庆贺词锦集100句

三米直尺法检测平整度

三米直尺法检测平整度

2024-02-10 2页

过渡句的用法归类

过渡句的用法归类

2023-10-16 4页

解除委托书范本集

解除委托书范本集

2023-12-04 8页

电子天平检定分度值与实际分度值的区别

电子天平检定分度值与实际分度值的区别

2023-01-12 4页

高校信息化问卷调查

高校信息化问卷调查

2022-11-13 18页

郑伯克段于鄢(翻译及注释)

郑伯克段于鄢(翻译及注释)

2023-12-26 4页

三坐标测量仪组成流程维护

三坐标测量仪组成流程维护

2022-11-29 14页

UHF RFID读写器的设计方案

UHF RFID读写器的设计方案

2024-01-18 8页

零售业态分类

零售业态分类

2023-09-22 2页

Graves病的诊断与鉴别诊断

Graves病的诊断与鉴别诊断

2023-07-26 1页