基于FPGA的数字信号发生器设计说明

33页1、 基于FPGA的数字信号发生器设计摘 要数字信号发生器是数字信号处理中不可缺少的调试设备,在生产生活中的应用非常广泛。本文所设计的容就是基于Altera公司的现场可编程门阵列(FPGA)实现数字信号发生器的设计,FPGA具有密度高,功耗低,体积小,可靠性高等特点,设计时可以不必过多考虑具体硬件连接;本设计中应用VHDL硬件描述语言进行描述,使该数字信号发生器可以产生正弦波、方波、三角波、锯齿波四个独立的波形,并能对所产生的四种波形的频率和幅度进行调节。关键词:直接数字频率合成;数字波形发生器;FPGA;DDS;VHDLDesign Of FPGA-based Digital Signal GeneratorYang Chunjian(Collegeof Physics Science and Information Engineering,JishouUniversity,JishouHunan416000)AbstractDigital signal transmitter as a test facility is an important part of information

2、processing system. In the production of a wide range of application of life. This content is designed by Altera, based on field programmable gate array (FPGA) design of digital signal generator, FPGA has a highdensity, low power consumption, small size, high reliability, can not have toomuchtoconsider wher designing specific hardware connection; the design of the application of VHDL hardware description language to describe, so that the digital signal generator can produce sine, square, triangle

3、, sawtooth waveforms of four independent,and is able to produce four waveforms by the frequency and amplitude adjustment.Key words:Direct Digital Frequency Synthesis;Digital Waveform Generator; FPGA;DDS;VHDL目 录第一章绪 论11.1 背景与意义11.2 国外发展现状1第二章 相关资料32.1 DDS技术32.2 FPGA简介42.3 VHDL简介52.4 Quartus简介7第三章 系统硬件电路设计93.1 数字信号发生器的系统组成93.2 设计原理与要求93.3 输入部分103.3.1频率、幅值和波形转换部分103.3.2系统时钟电路123.3.3 电源电路的设计123.4 FPGA部分123.5 D/A转换部分133.5.1 DAC0832转换器简介143.6滤波电路15第四章 系统软件设计164.1软件系统流程图164.2 数字信号发生器的软件设计164.2软件各模块174.

4、2.1 主控制模块174.2.2 波形数据产生模块18结束语22参考文献23附 录24 / 第一章 绪 论1.1 背景与意义在电子技术领域,常常需要波形、频率、幅度都可调的电信号,用于产生这种电信号的电子仪器称作信号发生器。信号发生器是一种常用的信号源,广泛运用于科学研究、生产实践和教学试验等领域。特别是在通信系统的科研实验中,常常需要用到不同频率和幅度的信号,如正弦波、三角波、方波和锯齿波等。作为一种为电子测量和计量提供电信号的设备,它和万用表、示波器、频率计等仪器一样,是最普通、最基本,也是运用最广泛的电子仪器之一,几乎所有电参量的测量都需要用到信号发生器。传统的波形发生器多采用模拟分立元件实现,产生的波形种类要受到电路硬件的限制,体积大、灵活性和稳定性也相对较差。近年来,以数字技术为基础的数字信号发生器得到了飞速的发展,性能指标都达到了一个新的水平。现场可编程门阵列器件具有容量大、运算速度快、现场可编程等优点,使得许多复杂的电路有了新的实现途径,越来越被广泛地应用到实际系统中。而且随着当今电子系统的越来越复杂,毫无疑问,数字信号发生器正在成为模拟复杂信号的事实标准。凡是能产生测试

《基于FPGA的数字信号发生器设计说明》由会员cn****1分享,可在线阅读,更多相关《基于FPGA的数字信号发生器设计说明》请在金锄头文库上搜索。

2021年七年级数学听课心得范文600字

(岗位职责)职责与权限

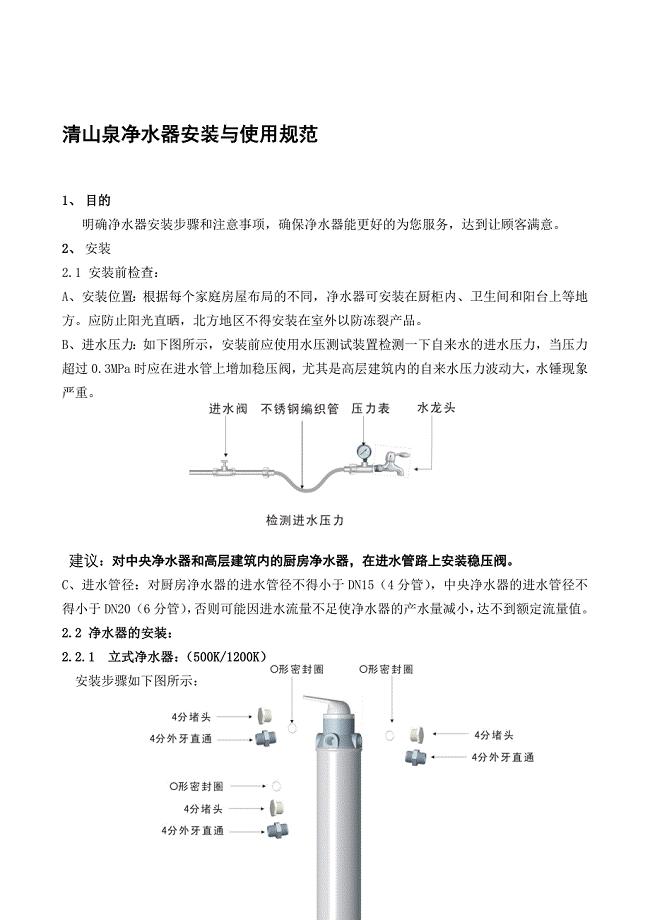

最新清山泉净水器安装与使用规范

商业中心的形成

大连理工大学21春《电气制图与CAD》在线作业二满分答案_95

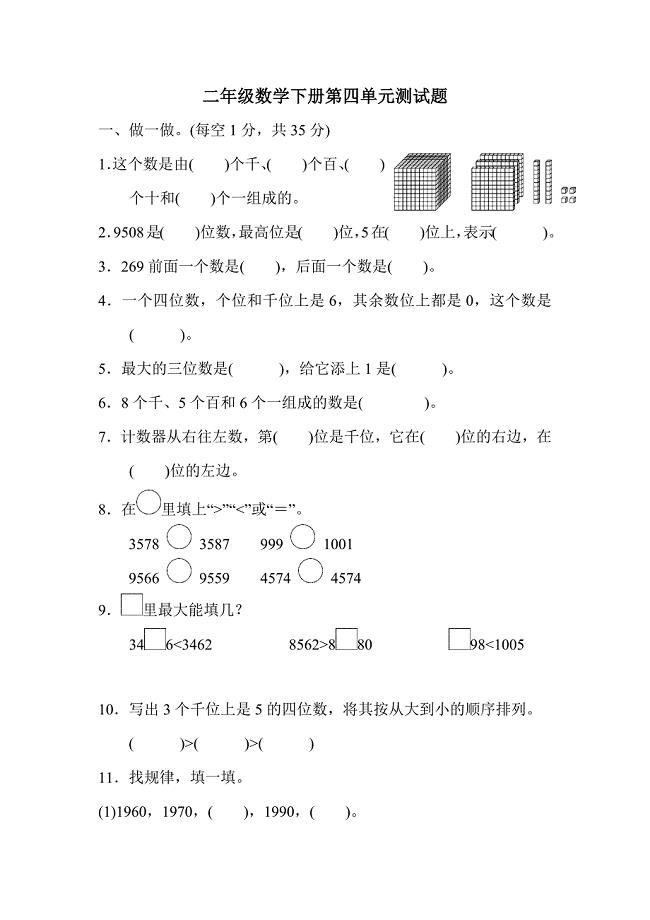

2020年苏教版二年级数学下册第四单元测试卷(含答案)

2022证券从业资格试题库及全真模拟试题含答案14

学前教育管理学和答案

有效促进师生沟通的基本条件

人教版一年级下册27课《两只小狮子》教学设计(宏庙小学_曾宪婷)

北京市农作物种子代销合同

第一学期初三班主任工作计划5篇第一学期班级工作计划

2022年初中优秀班主任个人总结.doc

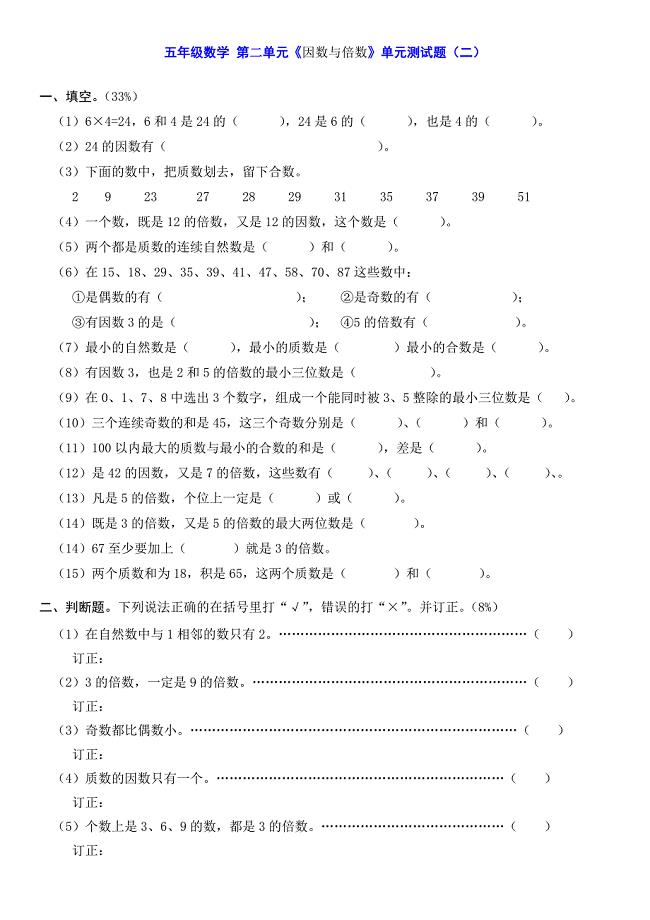

人教版五年级数学下册第二单元测试卷B

二次根式的乘除3

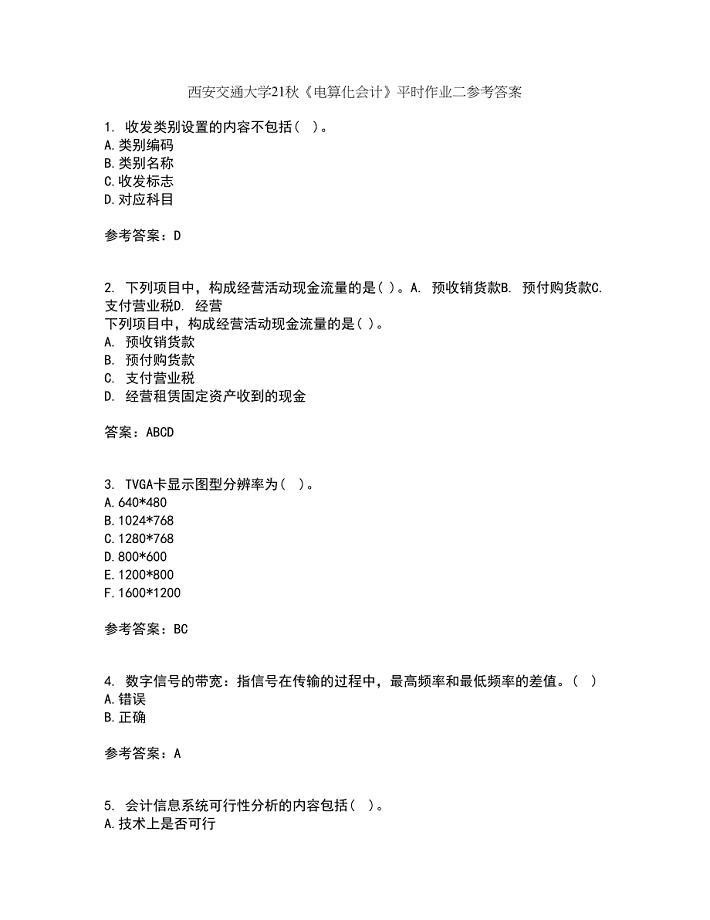

西安交通大学21秋《电算化会计》平时作业二参考答案18

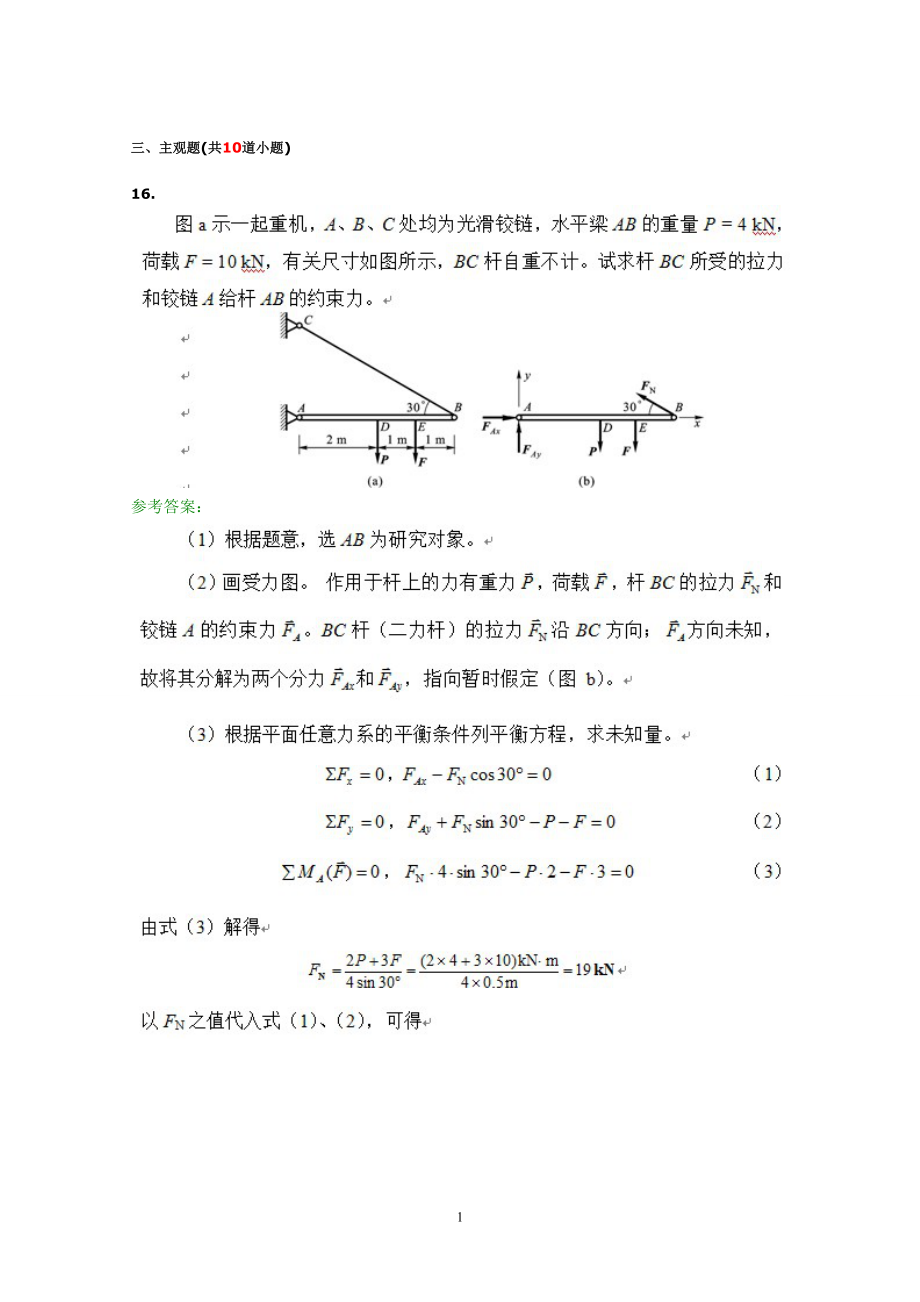

西南交大作业题及答案0615

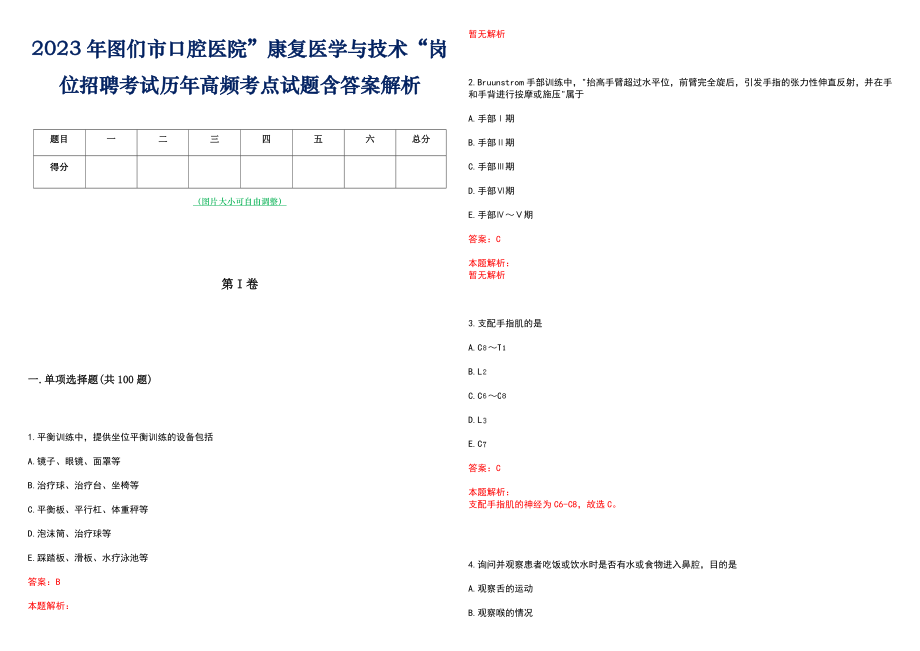

2023年图们市口腔医院”康复医学与技术“岗位招聘考试历年高频考点试题含答案解析

最新珠宝买卖协议范本

幼儿园亲子运动会活动总结(2篇).doc

中国大学MOOC形势与政策专题四(上)参考word

中国大学MOOC形势与政策专题四(上)参考word

2022-12-12 12页

工厂安全用电知识

工厂安全用电知识

2023-02-05 12页

温度采集与显示DSP控制器及其应用课程设计说明书

温度采集与显示DSP控制器及其应用课程设计说明书

2023-04-03 17页

落地式脚手架施工方案设计新颖

落地式脚手架施工方案设计新颖

2022-09-01 28页

2022证券从业资格试题库及全真模拟试题含答案14

2022证券从业资格试题库及全真模拟试题含答案14

2023-10-04 7页

综合布线设计方案1

综合布线设计方案1

2023-11-04 19页

学校应急演练计划3篇

学校应急演练计划3篇

2023-03-07 19页

有效促进师生沟通的基本条件

有效促进师生沟通的基本条件

2022-10-02 31页

地产项目营销推广方案3

地产项目营销推广方案3

2023-09-30 28页

工艺管理制度及其考核办法

工艺管理制度及其考核办法

2023-02-17 6页