计算机组成原理第五章5-7节

44页1、计算机学院体系结构中心计算机学院体系结构中心1、实现方法通过逻辑电路直接连线而产生的,又称为组合逻辑控制方式2、设计目标使用最少元件复杂的树形网络速度最高5.5 硬布线控制器硬布线控制器2024/5/8计算机学院体系结构中心计算机学院体系结构中心3、逻辑原理 1逻辑原理图C为微操作控制信号Im为译码器输出,Mi为节拍电位,Tk为节拍脉冲,Bj为状态条件C由组合电路实现,速度快,但难以修改。2指令的执行流程微程序控制器时序信号简单。只需要假设干节拍脉冲信号即可。组合逻辑控制器除了节拍脉冲信号外,还需要节拍电位信号。返回5.5 硬布线控制器硬布线控制器2024/5/8计算机学院体系结构中心计算机学院体系结构中心4 微操作控制信号产生n在微程序控制器中,微操作控制信号由微指令产生,并且可以重复使用。n在硬联线控制器中,某一微操作控制信号由布尔代数表达式描述的输出函数产生。n设计微操作控制信号的方法和过程是,根根据据所所有有机机器器指指令令流流程程图图,寻寻找找出出产产生生同同一一个个微微操操作作信信号号的的所所有有条条件件,并与适当的节拍电位和节拍脉冲组合,从而写出其布尔代数表达式并进行简化

2、,然后用门电路或可编程器件来实现。5.5 硬布线控制器硬布线控制器2024/5/8计算机学院体系结构中心计算机学院体系结构中心 例3 根据图5.29,写出以下操作控制信号RDI、RDD、WED、LDPC、LDIR、LDAR、LDDR、PC+1、LDR2的逻辑表达式。其中每个操作控制信号的含义是:RDI指存读命令RDD数存读命令WED数存写命令LDPC打入程序计数器LDIR打入指令存放器LDAR打入数存地址存放器LDDR打入数据缓冲存放器PC+1程序计数器加1LDR2打入R2存放器5.5 硬布线控制器硬布线控制器2024/5/8计算机学院体系结构中心计算机学院体系结构中心数据通路图数据通路图2024/5/8计算机学院体系结构中心计算机学院体系结构中心图5.29硬布线控制器的指令周期流程图M1M2M32024/5/8计算机学院体系结构中心计算机学院体系结构中心图5.29中五条指令的微操作控制信号举例。LDAR=M2(LAD+STO)T4 LDDR=M2T3(MOV+ADD)+M3LDAT3 LDIR=M1T4 其中M1、M2、M3是三个节拍电位信号;T3、T4为时钟周期信号;ADD、STO

3、、JMP是指令OP字段译码器的输出信号。5.5 硬布线控制器硬布线控制器2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.6.1 Intel 80885.6.2 IBM3705.6 传统传统CPU2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.6.1Intel 80882024/5/8计算机学院体系结构中心计算机学院体系结构中心5.6.2 IBM370IBM370 CPU1972年32位ALU的三个功能部件存放器结构CPU控制状态管态目态2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.1 并行处理技术5.7.2 流水CPU的结构5.7.3 流水线中的主要问题5.7.4 Pentium CPU5.7 并行并行CPU2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.1并行处理技术并行处理技术并行性Parrelism概念问题中具有可以同时进行运算或操作的特性例:在相同时延的条件下,用n位运算器进行n位并行运算速度几乎是一位运算器进行n位串行运算的n倍狭义广义含义只要在同一时刻同时性或在同一时间间隔内并发性完成两种或两种以上性

4、质相同或不同的工作,他们在时间上相互重叠,都表达了并行性2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.1并行处理技术并行处理技术三种形式时间并行重叠:让多个处理过程在时间上相互错开,轮流使用同一套硬件设备的各个部件,以加快硬件周转而赢得速度,实现方式就是采用流水处理部件空间并行资源重复:以数量取胜它能真正的表达同时性LSI和VLSI为其提供了技术保证时间+空间并行Pentium中采用了超标量流水线技术2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.2 流水流水CPU的结构的结构n1.流水计算机的系统组成n存储器体系:主存采用多体交叉存储器;Cachen流水方式CPU:指令部件、指令队列、执行部件n指令流水线n指令队列:FIFOn执行部件:可以有多个采用流水线方式构成的算术逻辑部件构成,可以将定点运算部件和浮点运算部件分开。2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.2流水流水CPU的结构的结构2.流水线CPU时空图IFInstruction Fetch取指 IDInstruction Decode指令译码EXExecut

5、ion执行 WBWrite Back写回2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.2流水流水CPU的结构的结构流水CPU非流水CPU2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.2流水流水CPU的结构的结构具有两条以上的指令流水线上图中流水线满载时,每一个时钟周期可以执行2条指令采用时间和空间并行技术2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.2流水流水CPU的结构的结构3.流水线Pipelining的分类按级别分为:指令流水线:取指,译码,取数,执行。算术流水线:加法流水线,乘法流水线,除法流水线等。处理机流水线宏流水线2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.3流水线中的主要问题流水线中的主要问题n瓶颈问题流水线中有速度慢的段n资源相关:多条指令进入流水线后在同一时钟周期内争用同一功能部件。n解决方法:后边指令拖一拍再推进;增设一个功能部件2024/5/8计算机学院体系结构中心计算机学院体系结构中心5.7.3流水线中的主要问题流水线中的主要问题 数据相关数据相关例:两条指令发生数据相关

《计算机组成原理第五章5-7节》由会员资****亨分享,可在线阅读,更多相关《计算机组成原理第五章5-7节》请在金锄头文库上搜索。

输油设备计算机辅助仿真系统

数显式顶板离层仪B

树立科学发展观(1)

数电组合逻辑电路应用举例、竞争冒险

数电实验0GOS6051型二踪示波器实验一常用电子仪器的使用练习

数电84第五版—康华光

数码裂隙灯图像系统操作

数理统计12主成分分析

数控系统的备份与还原训练

数控技术及应用清华版7数控机床进给伺服系统的控制原理

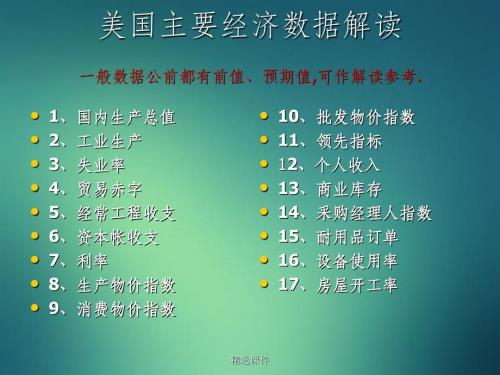

数据解读PPT(BNU金融协会)

数控技术及应用清华版8数控机床的精度

数控机床故障诊断 (2)

数据质量评估与控制体系-刘思琦组

数控技术及应用清华版17数控机床进给伺服系统的控制原理

数控技术2011-2-数控系统

数控加工工艺与设备》电子教案

数控加工的程序编制车床

数据通信与计算机网络第二版》电子教案西南

数据资料的收集方法

企业管理培训课件:领导力与执行力

企业管理培训课件:领导力与执行力

2024-05-22 48页

医疗品管圈培训课件:降低消毒供应中心内差件数

医疗品管圈培训课件:降低消毒供应中心内差件数

2024-05-22 28页

医疗医院新员工入职培训课件

医疗医院新员工入职培训课件

2024-05-22 22页

医疗健康培训课件:定期检验

医疗健康培训课件:定期检验

2024-05-22 32页

医疗培训课件:老年人误吸的预防与处理

医疗培训课件:老年人误吸的预防与处理

2024-05-22 22页

医疗健康培训课件:合理膳食 均衡营养

医疗健康培训课件:合理膳食 均衡营养

2024-05-22 31页

输油设备计算机辅助仿真系统

输油设备计算机辅助仿真系统

2024-05-14 5页

数显式顶板离层仪B

数显式顶板离层仪B

2024-05-14 6页

树立科学发展观(1)

树立科学发展观(1)

2024-05-14 40页

数电组合逻辑电路应用举例、竞争冒险

数电组合逻辑电路应用举例、竞争冒险

2024-05-14 38页