计算机组成原理复习

8页1、1.计算机中有两股信息:一股是(控制流),即操作命令,其发源地是(控制器),它分散流向各个部件;另一股是(数据流),它受控制信息的控制,从一个 部件流向另一个部件,边流动边加工处理。2. 从器件角度看计算机经历了五代变化。但从系统结构看,至今绝大多数计算机仍属于冯(诺依曼位表示符号位)计算机。3. 利用大规模集成电路技术把计算机的运算部件和控制部件做在一块集成电路芯片上,这样的一块芯片叫做单片机。? 错 这样的芯片叫 CPU4. 在计算机中,客观存在的事物或属性从某个角度看得到,就称为“透明”。?在计算机中,客观存在的事物或属性从某个角度看不到,就称为透明。5. 存储器系统的层次结构可以解决什么问题?实现存储器层次结构的先决条件是什么?用什么度量?存储器层次结构可以提高计算机存储系统的性能价格比,即在速度方面接近最高级的存储器,在容量和价格方面接近最低级的存储器。 实现存储器层次结构的先决条件是程序局部性,即存储器访问的局部性是实现存储器层次结构的基础。 其度量方法主要是存储系统的命中率,由高级存储器向低级存储器访问数据时,能够得到数据的概率。6. 对计算机的软、硬件资源进行管理,是?

2、的功能。(操作系统)7. 在计算机的层次结构中,为什么说硬件、软件的功能划分与逻辑上是等价的? 硬件的功能可以用软件完成,软件的功能 可以用硬件完成8. PCI总线的基本传输机制是猝发式传送。利用(桥)可以实现总线间的猝发式传送,使所有的存取都按CPU的需要出现在总线上。 PCI 允许多条总线(并行)工作。9. 在下列各种情况中,应采用异步传输方式的是?。CPU与I/O交换信息 CPU与PCI总线交换信息 CPU与存储器交换信息vJ/O接口与打印机交换信息10. 动态RAM和静态RAM都是易失性半导体存储器? ?丁11. 什么是总线标准?为什么要设置总线标准?目前流行的总线标准有哪些?总线标准可视为系统与各模块、模块与模块之间的一个互连的标准界面。 解决系统、模块、设备与总线之间的不适应、不通用、不匹配的问题。ISA、EISA、PCI、AGP、RS-232C、USB总线中地址线的作用( )。只用于选择存储单元V用于选择指定存储器单元和I/O设备接口电路的地址 由设备向主机提供地址 起到多路复用的作用12. 什么叫刷新?为什么要刷新?说明刷新有几种方法? 刷新的过程实质上是先将原存信息读

3、出,再由刷新放大器形成原信息并重新写入的再生过程。 刷新原因由于某些存储单元长期得不到访问,不进行存储器的读或写操作,其存储单元的原信息将会慢慢消失,为此必须采用定时刷新的方法。 常用的刷新方法有三种集中式、分散式、异步式。集中式:在规定的一个刷新周期内,集中安排一段时间进行刷新,此刻必须停止读或写操作;分散式:每行存储单元的刷新分散到每个存取周期内完成,无CPU访存死时间,不需停止读或写操作的死时间; 异步式:是集中式和分散式的折衷。13. 什么是程序访问的局部性原理?局部性原理可分为哪几类,各有何特点? 在一小段时间内,最近被访问过的程序和数据很可能再次被访问;在空间上,这些被访问的程序和数据往往集中在一小片存储区;在访问顺序上,指令顺序执行比转移 可能性大, 在一段小的时间间隔内,被访问过的某指令或数据,很快会被再次访问(时间局部性);进程访问的地址空间往往集中在某个区域(空间局部性)。13 同步通信之所以比异步通信具有较高的传输速率,是因为( )。同步通信不需要应答信号且总线长度较短同步通信用一个公共的时钟信号进行同步同步通信中,各部件存取时间较接近V以上各项因素的综合结果14

4、. 在链式查询方式下,若有 n 个设备,则有(n)条总线请求信号有n-1条总线请求信号共用一条总线请求信号无法确定15. 简述同步通信与异步通信的区别?16. 动态 RAM 的刷新是以 ? 为单位进行的。宏观而论DRAM刷新是以行为单位进行的。从微观看DRAM的刷新却又是以存储单元为基本单位。17. 计算机使用总线结构的主要优点是便于实现积木化,同时?。减少了信息传输量 加重了系统的工作量 提高了信息传输的速度 减少了信息传输线的条数18. 决定总线由哪个设备进行控制称为(总线仲裁 );实现总线数据的定时规则称为(总线协议 )。19. 根据连线的数量,总线可分为(串行)总线和并行总线,其中(串行)总线一般用于长距离的数据传送20. 下列有关存储器的描述中,不正确的是?多体交叉存储器主要解决扩充容量问题 cache 与主存统一编址,即主存空间的某一部分属于 cache丁访问存储器的请求是由CPU发出的cache的功能全由硬件实现21. 某计算机字长为32位,其存储容量为8MB,若按双字编址,它的寻址范围是?22. 若磁盘的转速提高一倍,则?。丁平均定位时间不变 平均存取时间减半存储密度可

《计算机组成原理复习》由会员人***分享,可在线阅读,更多相关《计算机组成原理复习》请在金锄头文库上搜索。

管理规约示范文本

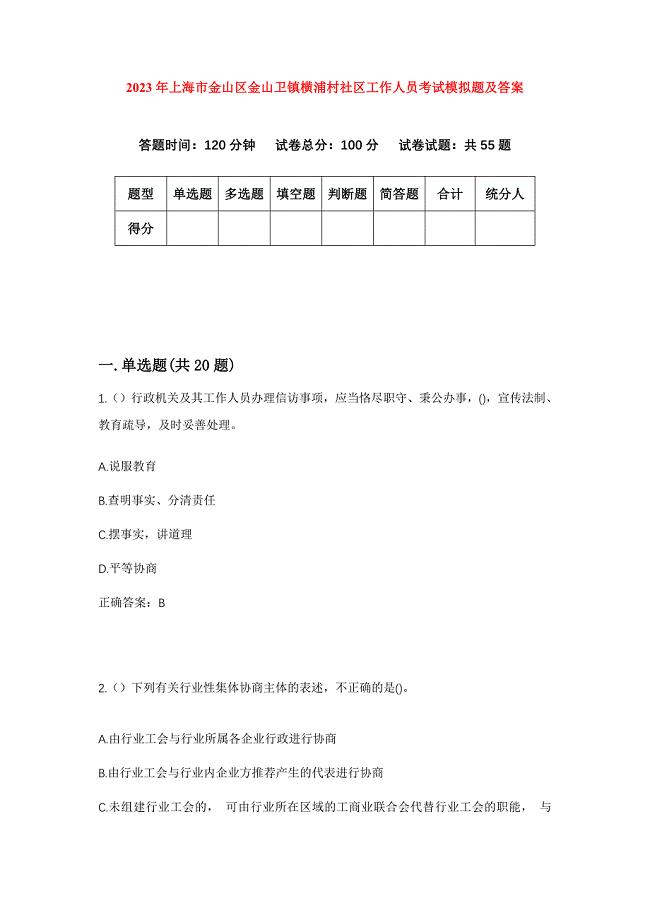

2023年上海市金山区金山卫镇横浦村社区工作人员考试模拟题及答案

2023年小学家长双减心得

2023手术室年度思想工作总结(5篇).doc

铝箔项目规划设计方案(模板)

法务实习生的职责范本(三篇).doc

初中学生会竞选演讲稿汇总5篇

部门经理个人年度工作总结范文(二篇).doc

门面转让合同范本(八篇).doc

碧天家园售楼部管理制度文件

贫困户入股分红协议

贵州省安顺市2023年高三下学期第二次诊断性检测试题数学试题

中国的行政区教学设计

客运站卫生管理制度

《优秀的绵羊》读后感1000字

救援基地水泥搅拌桩试桩施工方案

会计月工作计划(3篇).doc

离职协议书的样板

试用期三个月转正工作总结范文

中小企业局领导班子全年工作总结

网络文学作品评价体系分析

网络文学作品评价体系分析

2023-08-15 5页

骨折术后功能锻炼

骨折术后功能锻炼

2023-07-23 14页

冬季施工方案及施工保证措施36442

冬季施工方案及施工保证措施36442

2023-09-17 15页

电磁感应中的动力学问题

电磁感应中的动力学问题

2022-08-13 4页

无机材料科学基础课后答案

无机材料科学基础课后答案

2023-08-25 101页

计算组成原理与汇编语言

计算组成原理与汇编语言

2024-01-26 4页

附录F常用生态护岸技术详解

附录F常用生态护岸技术详解

2022-07-30 10页

材料力学作业

材料力学作业

2022-08-03 58页

高强螺栓断裂原因

高强螺栓断裂原因

2023-01-19 1页

预防校园盗窃

预防校园盗窃

2022-09-20 2页