计算机体系结构第五章练习题参考解答

8页1、。第五章5.34在一个采用组相联映象方式的Cache存储系统中,主存由 B0 B7 共 8 块组成,Cache有 2 组,每组 2 块,每块大小为 16B。在一个程序执行过程中,访存的主存块地址流为:B6,B2,B4,B1, B4,B6,B3, B0, B4 ,B5,B7, B3。(1)写出主存地址的格式,并标出各字段的长度。(2)写出 Cache 地址的格式,并标出各字段的长度。(3)指出主存与 Cache 之间各个块的映象关系。(4)0123Cache 块地址流。若 Cache的 4 个块号为 C、C、C和 C ,列出程序执行过程中的(5) 若采用 FIFO 替换算法,计算 Cache 的块命中率。(6) 若采用 LRU替换算法,计算 Cache 的块命中率。(7) 若改为全相联映象方式,再做 (5) 和 (6) 。(8) 若在程序执行过程中,每从主存装入一块到 Cache,平均要对这个块访问 16 次,计算在这种情况下的 Cache命中率。解:( 1)(2)采用组相联映象时,主存和Cache 地址的格式分别为:区号 E区内组号 G 主存组内块号 B块内地址 W组号 g组内块号 b

2、块内地址 w主存按 Cache 的大小分区,现主存有8 个块, Cache 有 2 2=4 个块,则主存分为 8/4=2个区,区号 E 的长度为 1 位。又每区有 2 个组,则组号 G、g 的长度都为 1 位。而每组有 2 个块,则块号 B、b 的长度又都为 1 位。每块大小为 16 个存储字,故块内地址 W、w的长度都为4 位。( 3)根据组相联映象的规则,主存块 07 与 Cache块 0 3 之间的映象关系为:主存块0、 1、 4、 5 与 Cache块 0、1 之间全相联,主存块2、3、6、7 与 Cache 块 2、3 之间全相联。( 4)根据组相联映象的规则, 该主存块地址流相应的一种 Cache块地址流如下表所示(组内替换算法为 FIFO)。时间: 123456789101112主存块地址流: B 6B 2B4B 1B4B 6B3B 0B4B5BCache块地址流: C 2C 3C0C 1C0C 2C2C 0C0C0C( 5)组内替换算法采用FIFO 时, Cache块 03 的使用过程如下表所示。时间:12345678910 1112主存块地址流:B 6B 2B4B1B

《计算机体系结构第五章练习题参考解答》由会员cl****1分享,可在线阅读,更多相关《计算机体系结构第五章练习题参考解答》请在金锄头文库上搜索。

2023年浙江省宁波市象山县丹西街道社区工作人员考试模拟试题及答案

温度采集与显示DSP控制器及其应用课程设计说明书

勿忘国耻圆梦中华

氦氖实验讲义

通信工程电源系统防雷技术规定

xx年秘书个人总结(二)

六盘水减震器项目招商引资方案【范文参考】

2022年实用的寒假周记3篇【最新】

![[工作范文]考研全程学习规划简案](https://union.152files.goldhoe.com/2023-12/2/42727eee-7943-4eba-8aa8-e202ff422457/pic1.jpg)

[工作范文]考研全程学习规划简案

2022企业技术中心年终工作总结

物业客户服务礼仪

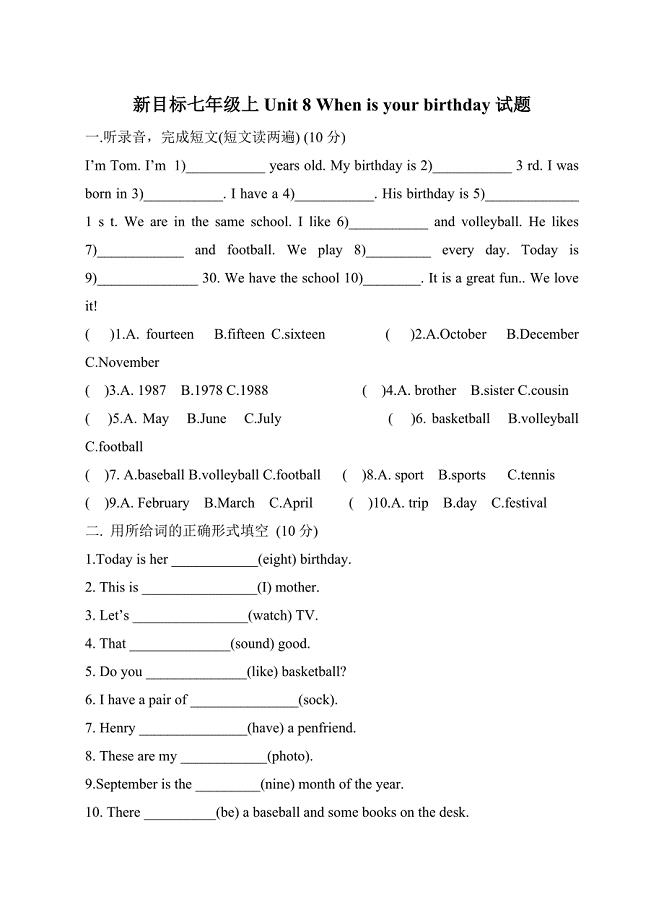

新目标七年级上Unit 8 When is your birthday试题

变电站监理总结

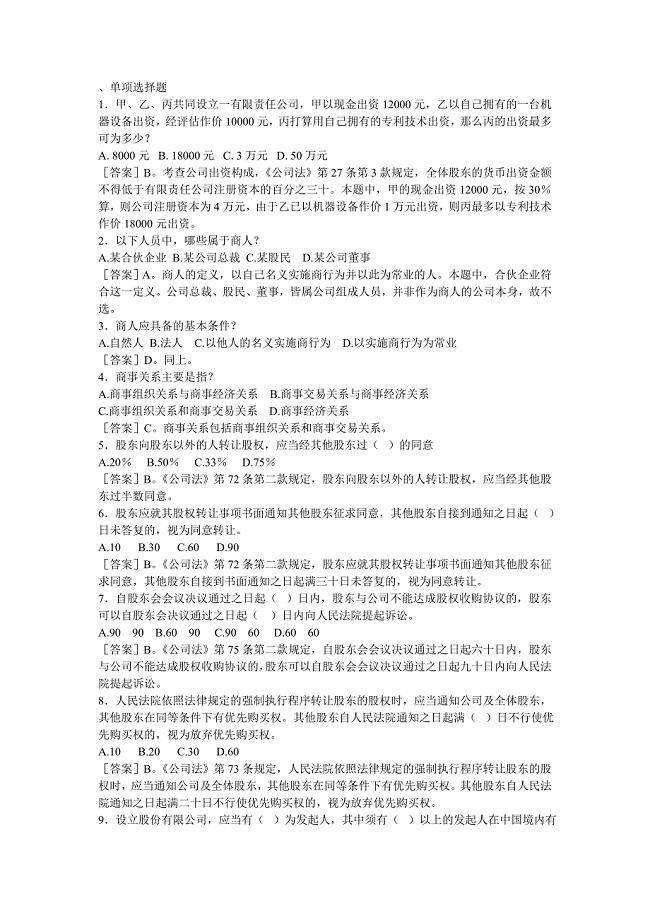

商法期末考试复习指南试题答案

生产计划主管工作总结

城市管理局四风问题情况工作总结

留守儿童心理健康教育讲稿(二)

《健康生活每一天》教学反思

砖砌检查井方案

新冠肺炎疫情防控学生健康档案

VC与Matlab混合编程

VC与Matlab混合编程

2024-02-06 19页

EtherPeek-NX-2.1软件的基本使用方法

EtherPeek-NX-2.1软件的基本使用方法

2022-09-28 9页

2011年12月考试可视化程序设计(VB)第一次作业doc

2011年12月考试可视化程序设计(VB)第一次作业doc

2023-04-14 6页

2013版电梯门禁梯控管理系统硬件手册

2013版电梯门禁梯控管理系统硬件手册

2023-08-03 8页

汽车空调多媒体课件

汽车空调多媒体课件

2023-01-03 171页

jsp中的数据库编程

jsp中的数据库编程

2024-01-16 8页

04界面编程2-控制条

04界面编程2-控制条

2022-11-17 21页

linu命令行下安装racleG

linu命令行下安装racleG

2022-08-17 13页

电力系统继电保护简介1

电力系统继电保护简介1

2024-03-02 5页

实验4Linux C语言编程和调试

实验4Linux C语言编程和调试

2023-09-01 7页