基于FPGA的通用可控分频器的设计

18页1、泉州师范学院毕业论文(设计)题目 墓于FPGA的通A可控分频器的设计物理与信息工程学院电子信息科学与技术专业2007级学生姓名 李文才 学号 070303018指导教师 曾永西 职称 讲师完成日期 2011 年4月1日教务处制基于FPGA的通用可控分频器的设计泉州师范学院电子信息科学与技术专业 070303018李文才指导教师曾永西讲师【摘要】介绍了基于FPGA的通用可控分频器的工作原理和设计过程。根据分频技术原理,使用 Altera 公司的EP2C8Q208C8芯片为核心器件,在 Quartus II平台上,用 VHDL语言编程完成了分频器的软 件设计、编译、调试、仿真和下载,然后与外围硬件电路相结合调试,最终设计出能进行2到9999分频和占空比1%J 99列调的分频器,该分频器的输入信号为1MHZ【关键词】FPGA ; VHDL ;通用分频器;分频系数;占空比#目录第1章引言21.1课题分析31.2 VHDL 语言和 QUARTUS II 简介31.2.1 VHDL 简介31.2.2 Quartus II 简介 4第2章方案选择及原理分析 42.1通用可控分频器硬件方案选择 42.

2、2通用可控分频器原理分析 42.2.1偶数分频器42.2.2奇数分频器 5第3章硬件设计 63.1系统设计的主要组成分 .63.2 FPGA 简介73.3显示电路介绍7第4章软件设计74.1系统分析74.2系统的结构和模块划分 74.2.1固定数值分频模块 84.2.2按键和显示模块 错误!未定义书签。4.2.3占空比和分频系数可控分频模块 84.3可控分频的实现10第5章 软硬件的系统测试 10结论10参考文献11致谢11附录I测量的数据表 12附录n程序12第1章引言分频器是数字系统设计中的一种基本电路,我们往往需要通过分频器得到我们所需要的时钟频率。在实际设计中我们经常用到的为整数分频,有时要求等占空比, 有时又要求非等占空比。在同一个设计中有时要求多种形式的分频,通常由计数器或计数器的级联结构构成各种形式的任意占空比偶数分频及非等占空比的奇数分频,实现起来比较简单,对于等占空比的奇数分频以及可控的分频实现起来会较为困难。本文利用VHDL硬件描述语言,通过Quartus n 7.2开发平台,使用 Altera公司的FPGA芯片,设计了一种能够满足上述要求,而 且较为通用的可控分频

3、器。只需在分频器的输入端用按键输入相应的分频系数,就可以得到所需的频率。1.1课题分析随着电子技术的高速发展,FPGA/CPLD以其高速、高可靠性、串并行工作方式等突出 优点在电子设计中受到广泛的应用,而且代表着未来EDA设计的方向。FPGA/CPLD的设计采用了高级语言,如 VHDL语言AHDL语言等,进一步打破了软件与硬件之间的界限, 缩短了产品的开发周期。所以采用先进的FPGA/CPLD取代传统的标准集成电路、接口电路 已成为电子技术发展的必然趋势。EDA技术代表了当今电子设计技术的最新发展方向,采用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程在汁算机上自动处理完成。 由于现代电子产品的复杂度和集成度的日益提高,一般分离的中小规模集成电路组合已不能满足要求,电路设计逐步地从中小规模芯片转为大规模、超大规模芯片,具有高速度、高集成度、低功耗的可编程朋IC器件已蓬勃发展起来。1分频器是一种在 FPGA的设计中使用效率非常高的设计,使用硬件描述语言进行设计 消耗不多

4、的逻辑单元就可以实现对时钟的操作,具有成本低、可编程等优点。1.2 VHDL 语言和 QUARTUS II 简介1.2.1 VHDL语言简介VHDL (VHSIC (Very High Speed Integrated Circuit ) Hardware Description Language )是 超高速集成电路硬件描述语言,是一种用于电路设计的高级语言。它出现于80年代后期,刚开始时它是由美国国防部开发出来的,是为了供美军用来提高设计的可靠性和缩减开发周期的一种使用范围比较小的设计语言。VHDL语言主要应用于数字电路系统的设计。目前,国内对它的应用多数集中在FPGA/CPLD/EPLD的设计当中,除此之外,一些较为有实力的单位,也将它用来设计 ASIC。VHDL语言具有多层次描述系统硬件功能的能力,既可以描述系统级电路,又可以 描述门级电路。而描述既可以采用行为描述、寄存器传输描述或结构描述,也可以采 用三者混合的混合级描述。另外,VHDL还支持惯性延迟和传输延迟,还可以准确地建立硬件电路模型。VHDL支持预定义的和自定义的数据类型,给硬件描述带来较大的自由度,使设计人员能够方

《基于FPGA的通用可控分频器的设计》由会员枫**分享,可在线阅读,更多相关《基于FPGA的通用可控分频器的设计》请在金锄头文库上搜索。

(完整)人教版二年级下册语文全册教案,推荐文档

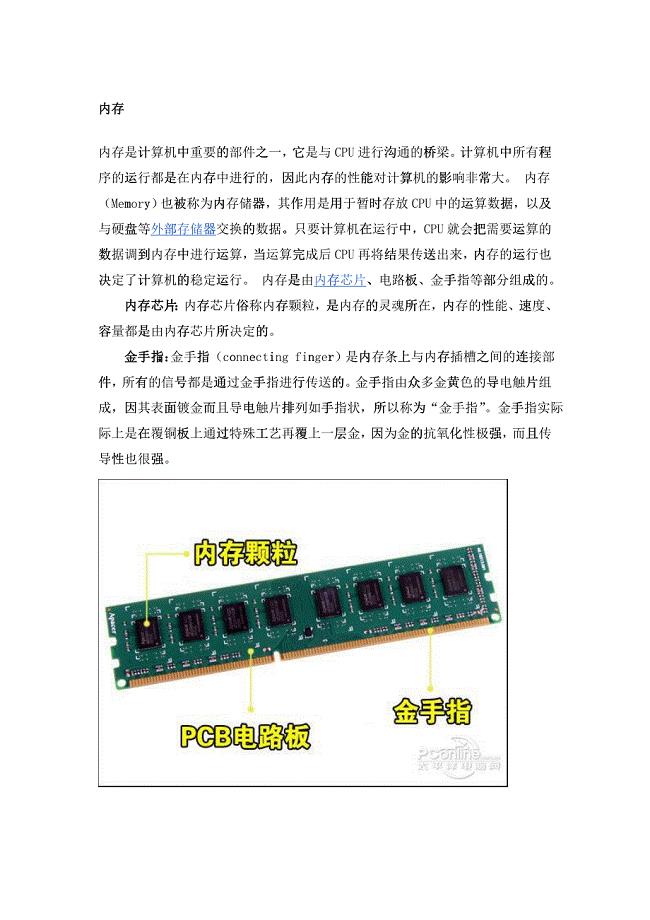

硬件培训范本

装卸工管理制度(9篇).doc

临床护理实践指南考试题06

热门劳动合同模板汇编10篇

2023办公室人员年终工作总结标准模板(3篇).doc

接待员年度考核个人总结2023年(四篇).doc

六年级复习资料

2022年口腔科医生年终总结

施工工地安全员工作总结与施工工地安全员工作总结范文汇编

广告的实习报告

中心幼儿园年度工作计划(四篇).doc

保安班长工作计划标准范本(2篇).doc

人教版语文九年级上册古诗文默写题大全

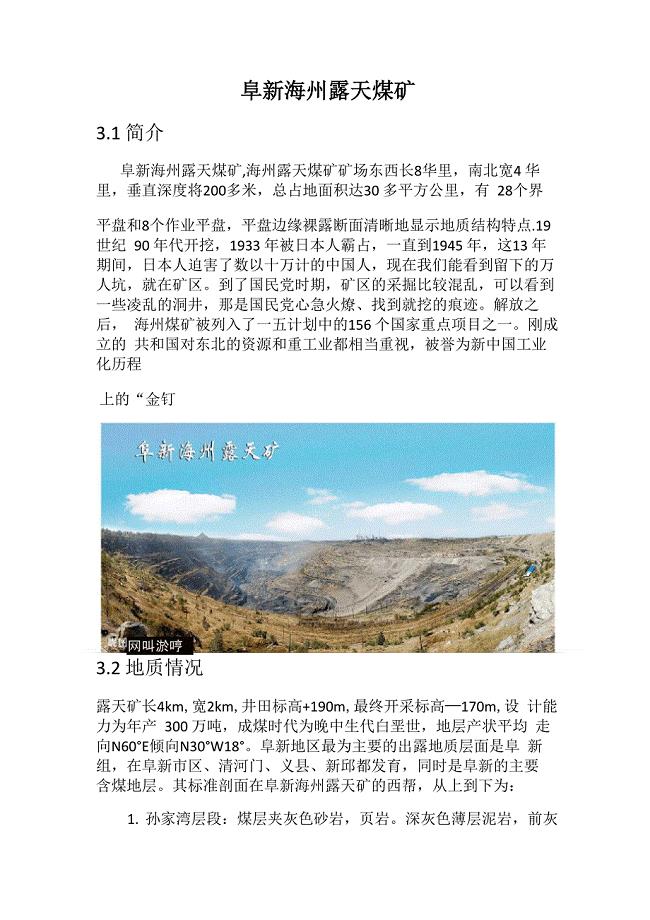

阜新海州露天煤矿

大创心得体会

2023物业管理助理年度工作计划例文(三篇).doc

劳务派遣公司章程

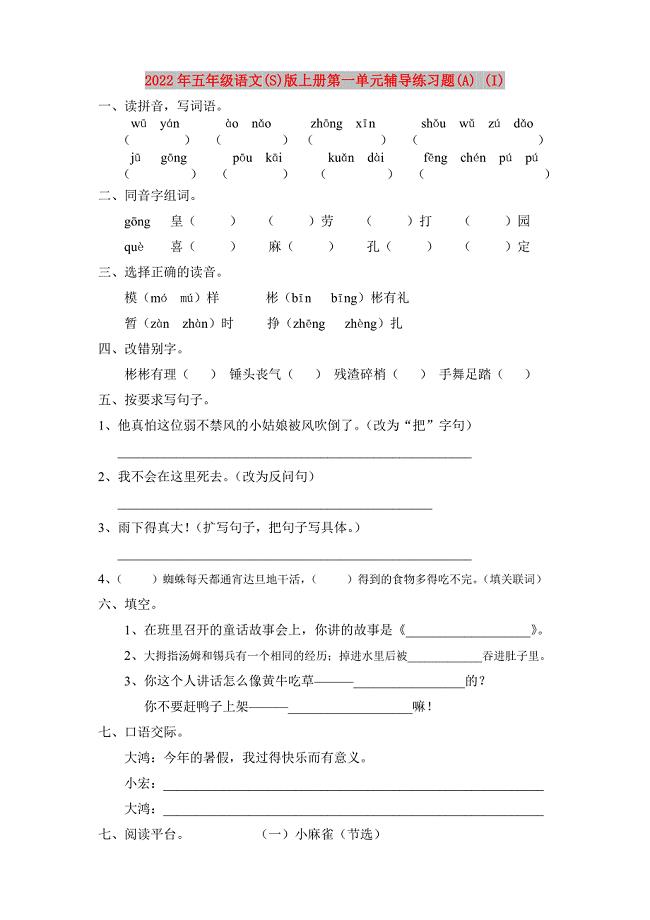

2022年五年级语文(S)版上册第一单元辅导练习题(A) (I)

江山市“十三五”规划研究报告

清洁煤项目可行性研究报告参考模板(DOC 77页)

清洁煤项目可行性研究报告参考模板(DOC 77页)

2023-09-30 77页

六年级奥数题和答案解析_20道题

六年级奥数题和答案解析_20道题

2023-10-14 12页

储罐基础工程施工组织设计范本(DOC 79页)

储罐基础工程施工组织设计范本(DOC 79页)

2022-11-11 79页

2016年全国代理营业机构负责人任职资格模拟考试(5)

2016年全国代理营业机构负责人任职资格模拟考试(5)

2023-02-10 13页

精编北师大六年级上册5.2复式折线统计图练习题及答案

精编北师大六年级上册5.2复式折线统计图练习题及答案

2022-12-18 3页

广东省深圳市龙岗区龙岗区横岗六约校2023届初中数学毕业考试模拟冲刺卷含解析

广东省深圳市龙岗区龙岗区横岗六约校2023届初中数学毕业考试模拟冲刺卷含解析

2023-04-27 16页

总结8篇园务工作总结

总结8篇园务工作总结

2023-11-19 52页

扩展语句,压缩语段之考向02:扩展语句(原卷版)

扩展语句,压缩语段之考向02:扩展语句(原卷版)

2023-01-07 6页

武汉建设监理规范用表a.b.c类表

武汉建设监理规范用表a.b.c类表

2023-01-03 23页

光交箱规范指导手册范本

光交箱规范指导手册范本

2023-01-21 21页