DDRSDRAM技术专题

20页1、DDR SDRAM技术专题DDRSDRAM是“双倍数据速率同步动态随机访问存储器”double date rate synchronous dynamic random access memory的缩写,是一种低成本、高容量的存储器,在计算机、消费类电子、通信等领域中一些要求高容量存储空间的场合有着广泛的应用。本技术专题试图以从事DDRSDRAM使用及其控制器设计的电子工程师的角度对DDRSDRAM进行较为详细的讨论。我们希望本技术专题能够为广大电子设计工程师提供有益的参考。1. DDR SDRAM概述SDRAM是同步动态随机访问存储器的缩写,是一种低成本、高容量的存储器。它在计算机、消费类电子、通信等领域中一些要求高容量存储空间的场合有着广泛的应用。传统的SDRAM采用一种单倍数据速率(SDR)的结构执行访问操作,它在每个时钟周期的上升沿传输数据,因此SDRSDRAM的带宽等于其时钟其频率乘以其数据总线宽度 w=f*bus。例如,如果SDRSDRAM的操作频率为100MHz,其数据总线宽度为16位,则其总线带宽为100MHzx16bit=1600Mbit/S,也就是1.6Gbps。而

2、对带宽的需求是无休止的!为了增加总线带宽,如果使用传统的方法,我们要么增加数据总线宽度,要么提高其操作频率。那么,有没有可能在既不增加数据总线宽度也不提高工作频率的条件下增加总线带宽呢?为适应这种需求,DDRSDRAM出现了!DDRSDRAM使用一种双倍数据速率的结构来获得高性能的操作。双倍数据速率结构本质上是一种2n预取结构,在输入/输出管脚上,每个时钟周期可以传输两个字。对于一次DDRSDRAM的访问操作(写操作、读操作),在芯片的内部,一个时钟周期执行一个位宽为2n的数据传输,而在DDRSDRAM器件的管脚上则每半个时钟周期执行一次n位的数据传输。因此,DDRSDRAM的总线带宽为:工作频率数据总线宽度2可见,在相同的数据总线宽度和工作频率下,DDRSDRAM的总线带宽比SDRSDRAM的总线带宽提高了一倍。概括起来,DDRSDRAM具有如下特点: 双倍数据速率结构,每个时钟周期完成两次数据传输; 双向的数据选通信号(DQS)伴随数据一起传输。在接收侧,它用来捕获数据; 在读操作过程中,DQS与数据沿对齐,在写操作过程中,DQS与数据中央对齐; 差分的时钟输入(CK与/CK);

3、DLL将DQ和DQS的跃变与CK的跃变对齐; 在每个CK的上升沿接收命令字;数据和数据掩码参考于DQS的上升沿和下降沿; 内部的四个BANK可以并发操作; 写数据时支持数据掩码(DM); 支持的突发长度:2、4、或8; CAS潜伏期:2或2.5,DDR400还包括CL=3 为每一次突发访问提供了AUTOPRECHARGE选项; 自动刷新与自刷新模式; 2.5V(SSTL_2兼容)I/O; 对于DDR200、DDR266、DDR333:VDDQ为+2.5V0.2V;对于DDR400:+VDDQ为2.60.1V; 对于DDR200、DDR266、DDR333:VDD为+3.3V0.3V或+2.5V0.2V;对于DDR400:+VDDQ为2.60.1V;2. DDR SDRAM与SDR SDRAM的功能比较在对DDRSDRAM进行详细描述之前,我们首先对DDRSDRAM与SDRSDRAM的功能作一个简要的对比。下表列出了它们之间在外部接口上的一些不同之处:SDRSDRAM与DDRSDRAM的内部存储核本质上是相同的。它们都具有相同的寻址和命令控制接口;都具有4个BANK的存储阵列;都具有相同

4、的刷新要求。它们之间基本的不同点在于数据接口。SDRSDRAM的数据接口是一个系统同步的设计,它仅仅在时钟的上升沿捕获数据。它的内、外部数据总线具有相同的宽度,当数据穿越I/O缓冲器时被顺序地锁存到内部存储阵列。SDRSDRAM还支持一个DQM信号,它在写操作过程中作为数据掩码使用;在读操作过程中作为输出使能使用。DDRSDRAM的数据接口是一个源同步的设计,数据在每个时钟周期被捕获两次,并伴随一个双向的数据选通信号。DDRSDRAM采用了一种2n预取结构,它的内部数据总线宽度是外部数据总线宽度的两倍。这就使得内部存储单元以成对的方式向I/O缓冲器传递数据。DDRSDRAM在读操作时没有输出使能信号,但它支持一个BURSTTERMINATE命令来快速中止正在执行的READ命令。在WRITE操作过程中,DM信号被用来屏蔽无效的写数据。DDRSDRAM的命令总线包括时钟使能、芯片选择、行地址、列地址、BANK地址、以及写使能信号。DDRSDRAM采用一对差分时钟(CK和CK#)进行工作,DDRSDRAM的命令信号(地址和控制信号)使用CK的上升沿锁存。与SDRSDRAM不同,DDRSDRA

《DDRSDRAM技术专题》由会员M****1分享,可在线阅读,更多相关《DDRSDRAM技术专题》请在金锄头文库上搜索。

有关绿色环保倡议书汇编9篇

中班美术活动教案熊猫教案

2022年安德学校体质健康测试实施方案

实验室管理程序

工作转正总结范文(二篇).doc

幼儿园中班安全教案

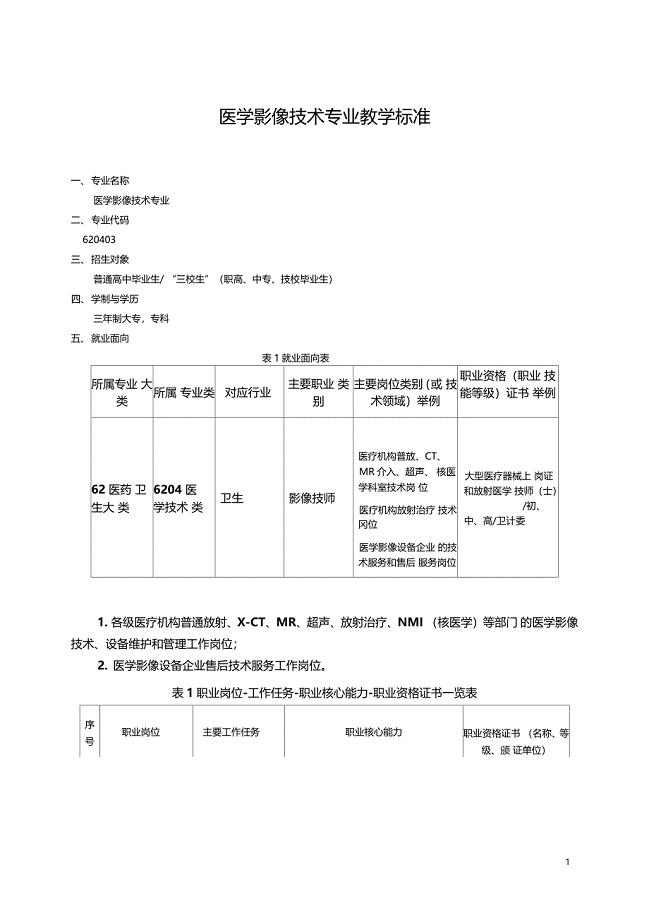

医学影像技术专业教学标准

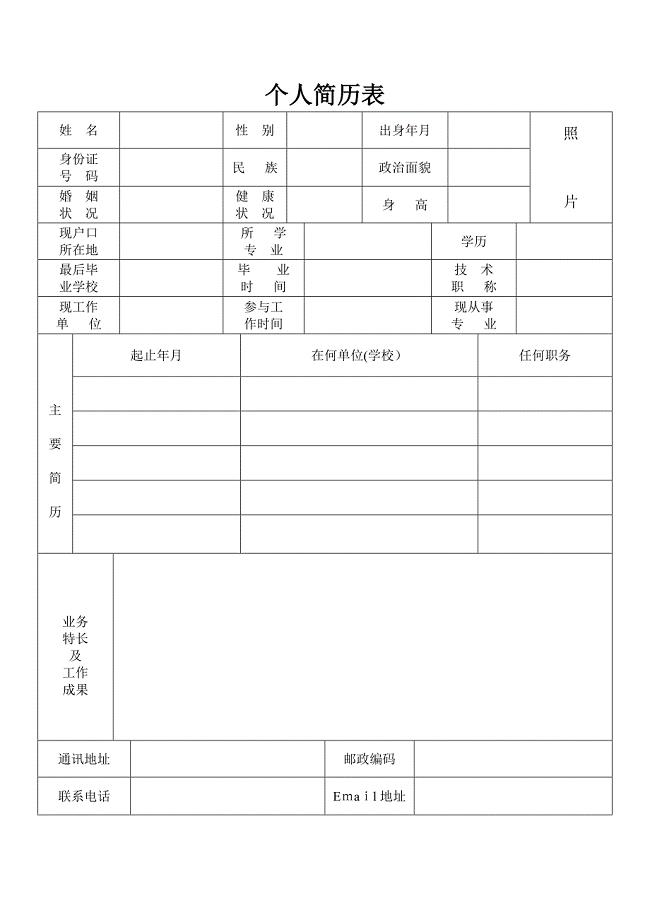

标准个人简历

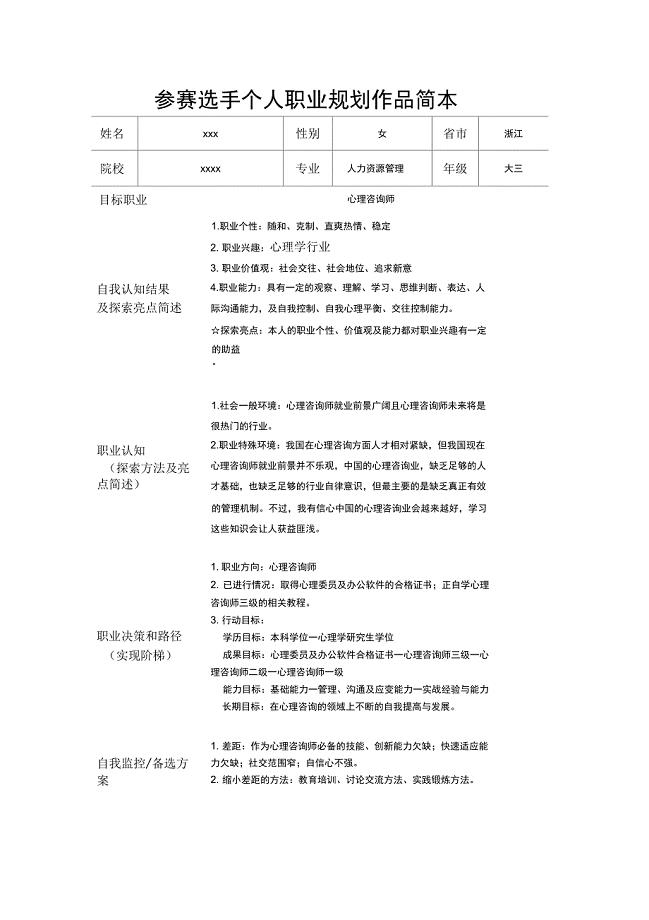

个人职业生涯规划(含简本)

劳动实践基地活动总结

QuEChERS方法在果蔬多种农药残留检测中的应用研究

在学校党的群众路线教育实践活动动员大会上的讲话

语文教学经验总结范文(三篇).doc

2022年考博英语-西南科技大学考前拔高综合测试题(含答案带详解)第143期

一级建造师项目管理考试(全考点覆盖)名师点睛卷含答案66

劳动力管理员及岗位实务试卷

托班新学期教师个人工作计划

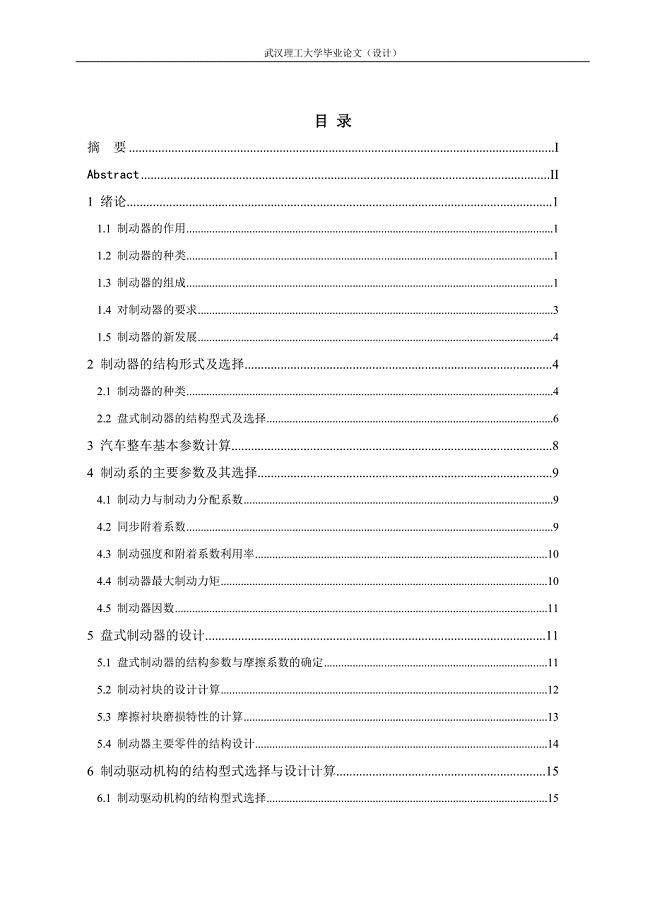

盘式制动器毕业设计说明书

做合格的班主任演讲稿

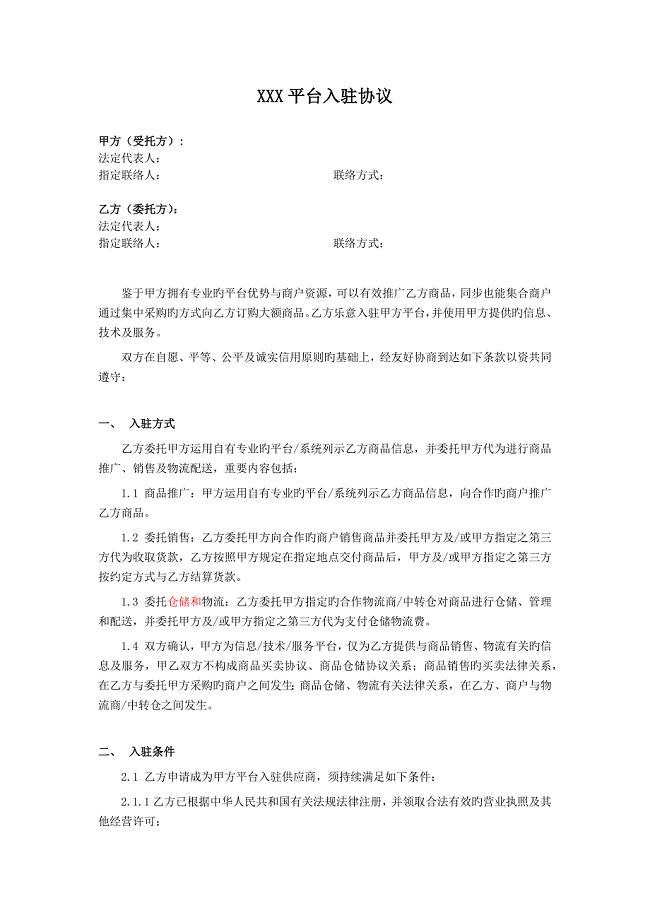

平台入驻协议

中心学校安全工作计划(四篇).doc

中心学校安全工作计划(四篇).doc

2024-01-10 17页

小班安全教育计划第一学期

小班安全教育计划第一学期

2024-01-14 7页

2023二年级的学期班主任工作计划范文(五篇).doc

2023二年级的学期班主任工作计划范文(五篇).doc

2023-04-07 17页

【最新资料】【教科版】语文六年级下册:第五单元提升练习Word版含答案

【最新资料】【教科版】语文六年级下册:第五单元提升练习Word版含答案

2024-01-27 6页

关于欢乐学习演讲稿5篇

关于欢乐学习演讲稿5篇

2023-11-24 12页

在侄儿婚宴上的致辞

在侄儿婚宴上的致辞

2023-01-24 4页

总裁助理岗位职责

总裁助理岗位职责

2023-05-16 4页

班主任校本培训计划标准模板(2篇).doc

班主任校本培训计划标准模板(2篇).doc

2022-08-17 5页

大学生干部个人工作计划

大学生干部个人工作计划

2023-10-16 4页

社区爱国卫生工作计划书

社区爱国卫生工作计划书

2024-01-15 4页