计算机组成原理复习资料

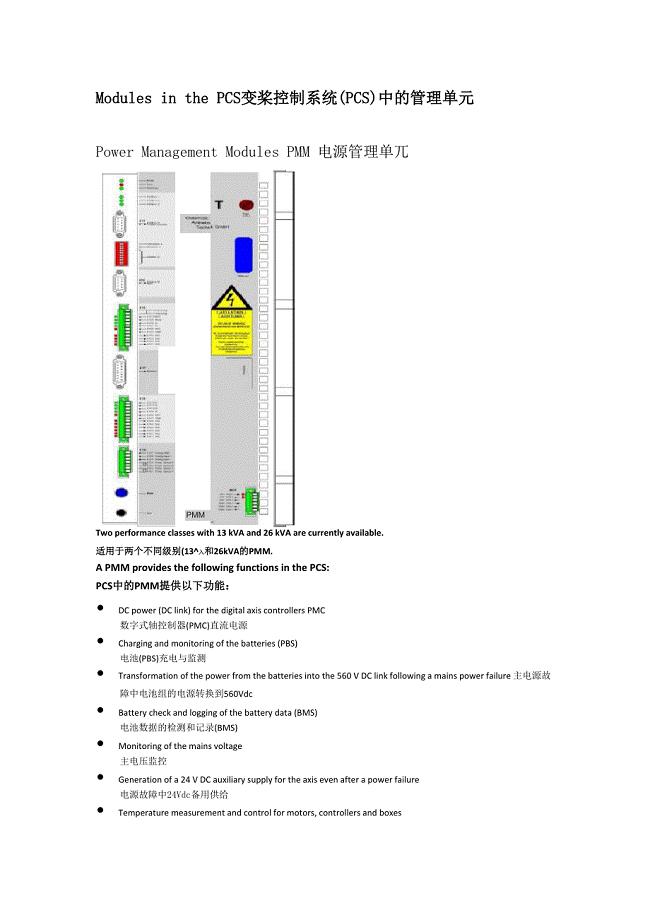

8页1、计算机组成原理复习大纲考试题型:一、 选择题:20题共20分二、 填空题:10空共10分三、 名词解释:3题共12分四、 简答题:4题共24分五、 综合题:4题共34分1 .什么是计算机系统、计算机硬件和计算机软件?硬件和软件哪个更重要? 计算机系统:由计算机硬件系统和软件系统组成的综合体。计算机硬件:指计算机中的电子线路和物理装置。计算机软件:计算机运行所需的程序及相关资料。硬件和软件在计算机系统中相互依存,缺一不可,因此同样重要。2 .冯?若依曼计算机的特点是什么?冯?i若依曼计算机的特点是:计算机由运算器、控制器、存储器、输入设备、输出设备五大部件组成;指令和数据以同同等地位存放于存储器内,并可以按地址访问;指令和数据均用二进制表示;指令由操作码、地址码两大部分组成,操作码用来表示操作的性质,地址码用来表 示操作数在存储器中的位置;指令在存储器中顺序存放,通常自动顺序取出执行;机器以运算器为中心(原始冯 ?若依曼机)。3 .画出计算机硬件组成框图,说明各部件的作用及计算机系统的主要技术指标。计算机硬件组成框图如下:I控制器I % Mx e jl|运器|存 存谪器 ; I in_I

2、 I_接口I ij. cpu : - ;=输 输入设备 输出设备| :!l II Ii主机:;外设各部件的作用如下:控制器:整机的指挥中心,它使计算机的各个部件自动协调工作。运算器:对数据信息进行处理的部件,用来进行算术运算和逻辑运算。存储器:存放程序和数据,是计算机实现存储程序控制”的基础。输入设备:将人们熟悉的信息形式转换成计算机可以接受并识别的信息形式的设备。 输出设备:将计算机处理的结果(二进制信息)转换成人类或其它设备可以接收和识 别的信息形式的设备。4 .解释下列概念:主机、CPU、主存、存储单元、存储元件、存储基元、存储元、存储字、存储字长、存储容 量、机器字长、指令字长。主机:是计算机硬件的主体部分,由 CPU和主存储器MM合成为主机。CP U:中央处理器,是计算机硬件的核心部件,由运算器和控制器组成;(早期的运算器和控制器不在同一芯片上,现在的CPU内除含有运算器和控制器外还集成了CACHE )。主存:计算机中存放正在运行的程序和数据的存储器,为计算机的主要工作存储器,可随机存取;由存储体、各种逻辑部件及控制电路组成。存储单元:可存放一个机器字并具有特定存储地址的存储

3、单位。存储容量:存储器中可存二进制代码的总量;(通常主、辅存容量分开描述)。机器字长:指 CPU 一次能处理的二进制数据的位数,通常与 CPU的寄存器位数有关。指令字长:机器指令中二进制代码的总位数。5 .解释下列英文缩写的中文含义:CPU、PC、IR、CU、ALU、ACC、MQ、X、MAR、MDR、I/O、MIPS、CPI、FLOPS 全面的回答应分英文全称、中文名、功能三部分。CPU : Central Processing Unit,中央处理机(器),是计算机硬件的核心部件,主要由 运算器和控制器组成。PC: Program Counter,程序计数器,其功能是存放当前欲执行指令的地址,并可自动 计数形成下一条指令地址。IR: Instruction Register,指令寄存器,其功能是存放当前正在执行的指令。CU: Control Unit,控制单元(部件),为控制器的核心部件,其功能是产生微操作命 令序列。ALU : Arithmetic Logic Unit,算术逻辑运算单元,为运算器的核心部件,其功能是进 行算术、逻辑运算。ACC: Accumulator ,累加器,是

4、运算器中既能存放运算前的操作数,又能存放运算结 果的寄存器。MQ : Multiplier-Quotient Register,乘商寄存器,乘法运算时存放乘数、除法时存放商 的寄存器。X:此字母没有专指的缩写含义,可以用作任一部件名,在此表示操作数寄存器,即 运算器中工作寄存器之一,用来存放操作数;MAR : Memory Address Register ,存储器地址寄存器,在主存中用来存放欲访问的存 储单元的地址。MDR : Memory Data Register,存储器数据缓冲寄存器,在主存中用来存放从某单元读出、或要写入某存储单元的数据。I/O : Input/Output equipment ,输入/输出设备,为输入设备和输出设备的总称,用于计 算机内部和外界信息的转换与传送。MIPS : Million Instruction Per Second,每秒执行百万条指令数,为计算机运算速度指 标的一种计量单位。6 .什么是总线?总线传输有何特点?为了减轻总线负载,总线上的部件应具备什么特点?总线是一种能由多个部件分时共享的公共信息传送线路。总线传输的特点是:某一时刻只允许有

《计算机组成原理复习资料》由会员汽***分享,可在线阅读,更多相关《计算机组成原理复习资料》请在金锄头文库上搜索。

探究3D奥秘

探究3D奥秘

2024-01-10 7页

洲际酒店集团企业文化介绍

洲际酒店集团企业文化介绍

2022-12-31 2页

2017年浙江省主治医师职业考试试卷

2017年浙江省主治医师职业考试试卷

2023-07-16 5页

宪法学试题及参考复习资料

宪法学试题及参考复习资料

2024-02-06 8页

矿井主排水系统设计方法探讨

矿井主排水系统设计方法探讨

2023-01-27 7页

2020年幼儿园秋天主题活动教案

2020年幼儿园秋天主题活动教案

2022-11-20 7页

分期付款买卖合同

分期付款买卖合同

2023-02-24 4页

“于是见公输盘子墨子解带为城以牒为械”阅读答案及翻译

“于是见公输盘子墨子解带为城以牒为械”阅读答案及翻译

2022-09-29 3页

乳制品工厂建厂可行性研究报告

乳制品工厂建厂可行性研究报告

2023-01-23 12页

供应链联合库存管理模式的利弊

供应链联合库存管理模式的利弊

2023-05-18 15页