Altera-FPGA详解

23页1、Altera中文资料FPGA在软件无线电中的应用介绍软件无线电(SDR)是具有可重配置硬件平台的无线设备,可以跨多种通信标准。它们因为更低的成本、更大的灵活性和更高的性能,迅速称为军事、公共安全和商用无线领域的事实标准。SDR成为商用流行的主要原因之一是它能够对多种波形进行基带处理和数字中频(IF)处理。IF处理将数字信号处理的领域从基带扩展到RF。支持基带和中频处理的能力增加了系统灵活性,同时减小了制造成本。基带处理无线标准不断地发展,通过先进的基带处理技术如自适应调制编码、空时编码(STC)、波束赋形和多入多出(MIMO)天线技术,支持更高的数据速率。基带信号处理器件需要巨大的处理带宽,以支持这些技术中大计算量的算法。例如,美国军事联合战术无线系统(JTRS)定义了军事无线中20多种不同的无线波形。一些更复杂的波形所需的计算能力在标准处理器上是每秒数百万条指令(MIPS),或者如果在FPGA实现是数千个逻辑单元。协处理器特性SDR基带处理通常需要处理器和FPGA。在这类应用中,处理器处理系统控制和配置功能,而FPGA实现大计算量的信号处理数据通道和控制,让系统延迟最小。当需要从一种

2、标准切换至另一种标准时,处理器能够动态地在软件的主要部分间切换,而FPGA能够根据需要完全重新配置,实现特定标准的数据通道。FPGA可以作为协处理器同DSP和通用处理相连,这样具有更高的系统性能和更低的系统成本。自由地选择在哪实现基带处理算法为实现SDR算法提供了另一种方式的灵活性。 基带部件也需要足够灵活让所需的SDR功能支持在同一种标准增强版本之间的移植,并能够支持完全不同的标准。可编程逻辑结合软核处理器和IP,具有了提供在现场远程升级的能力。图1 是一个框图,其中FPGA能够通过IP功能如Turbo编码器、Reed-Solomon编码器、符号交织器、符号映射器和IFFT,很容易地重配置支持WCDMA/HSPDA或802.16a标准的基带发送功能。 图1. 两种无线信号的SDR基带数据通道重配置例子数字IF处理数字频率变化具有比传统模拟无线处理方式更高的性能。FPGA提供了一种高度灵活和集成的平台,在这之上以合理的功率实现大计算量的数字IF功能,这在便携系统中是一个关键的因素。能够在FPGA实现的IF功能包括数字上变频器(DUC)和下变频器(DDC),以及数字预畸变(DPD)和波峰

3、系数削减(CFR),帮助降低功放的成本和功率(见图2)1. DUC:数字上变频器 2. CFR: 波峰系数削减 3. DPD: 数字预畸变 4. DDC: 数字下变频器 5. PA: 功放 6. LNA: 低噪放 图2. 在SDR架构中中频处理单元例子数字上变频器数字格式(在基带处理单元和上变频器之间一般需要)可以顺利地加到上变频器的前端。这项技术为上变频器提供了全定制的前端,容许信道化的高带宽输入数据。定制逻辑或软核嵌入式处理器可用来控制上变频器和FPGA中实现的基带处理单元之间的接口。在数字上变频中,输入数据在用可调的载波频率进行正交调制之前经过基带滤波和插值。为了实现插值基带有限冲激响应(FIR)滤波器,必须在速度面积之间进行权衡为特定的标准获得优化的固定或自适应架构。数控振荡器核也能够产生多种架构,它们具有超过115db无寄生动态范围和非常的高性能。根据支持的频率分配数量,在FPGA中可以很容易地例化多个上变频器。波峰系数削减3G 基于CDMA的系统和多载波系统如正交频分复用(OFDM)的信号具有很高的峰平比(波峰系数)。这样的信号会极大地降低基站中功放的效率。对多波形标准,在

4、FPGA中实现的波峰系数削减技术是一种降低功放成本和复杂度的合算的方式。数字预畸变高速移动数据传输采用非恒包络调制技术如QPSK和正交幅度调制(QAM)。这对PA的线性度有严格的要求。DPD线性化技术,包括查找表和多项式方式都可以有效地在包含DSP块的FPGA中实现。这些DSP块中的乘法器可以在很高的时钟速率下运行,可以有效地分时实现复数乘法。当SDR基站中使用FPGA时,FPGA可以为特定的标准重配置来实现合适的DPD算法,有效地线性化PA。数字下变频器在接收器侧,数字IF技术可以对IF信号进行采样,在数字域执行信道化和采样率转换。使用降采样技术,高频IF信号(同时100MHz以上)可以被量化。因为不同的标准有不同的码片/比特速率,对SDR应用需要非整数采样率,把采样数转换为任何标准基本码片/比特速率的整数倍。结论FPGA提供了通用的计算结构,非常适合于软件无线电中基带和IF数字处理的需要。另外,结合通用处理器或DSP,它们作为通用处理器或DSP软件处理的硬件协处理器,能够增强功能,改善吞吐量,减小系统成本和降低系统功率。作者:Joel A. SeelyTechnical Marke

《Altera-FPGA详解》由会员汽***分享,可在线阅读,更多相关《Altera-FPGA详解》请在金锄头文库上搜索。

【精选】小学二年级日记日记6篇

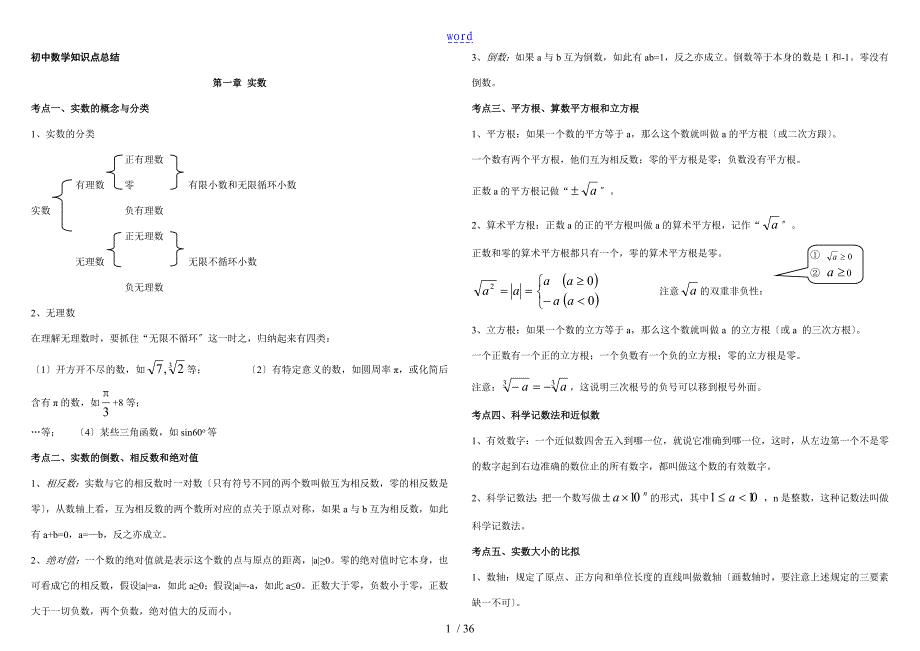

初中数学知识点总结材料

2023劳动就业合同书范文.doc

冬天领导致辞开场白

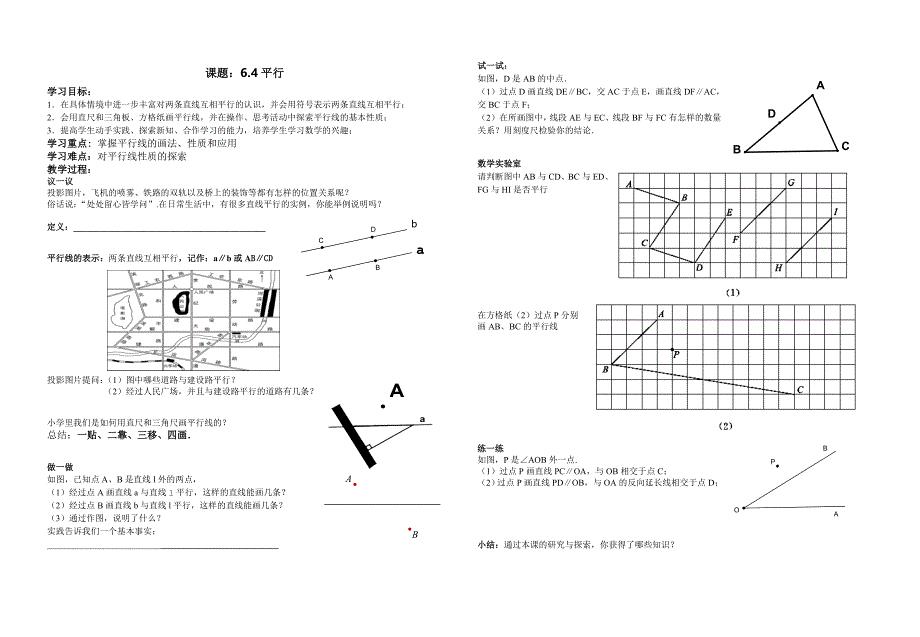

64平行教学案

学校法制教育和交通安全讲话稿

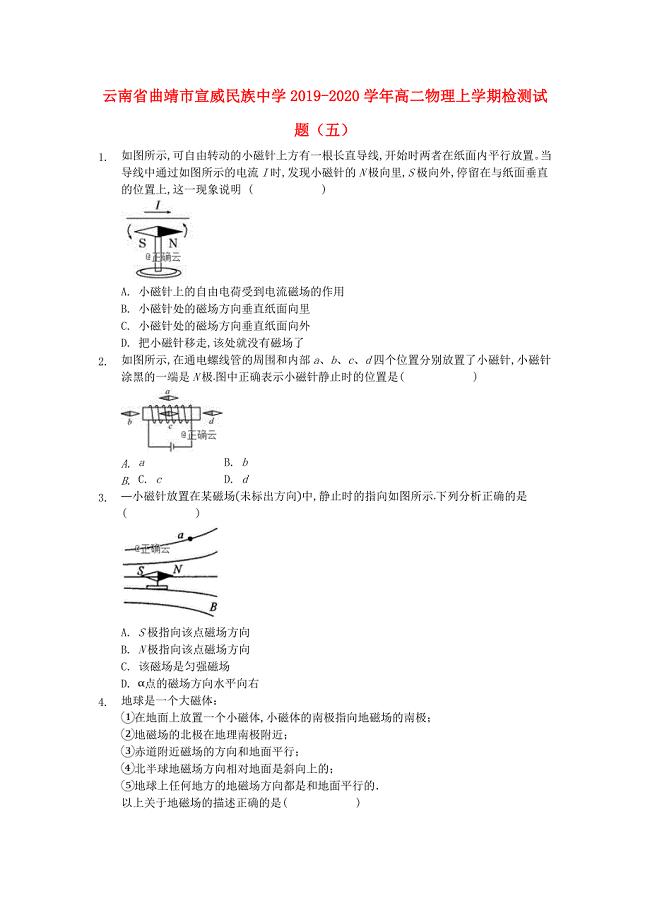

云南省曲靖市宣威民族中学2019-2020学年高二物理上学期检测试题五

学生实习老师工作的心得5篇

建设工程管理专业诊断报告(体例报告)

2023年文控管理办法4篇

2023年护士工作计划标准样本(3篇).doc

水产工作会议典型材料

软件产品代理合同书范文(六篇).doc

教学常规检查总结(2篇).doc

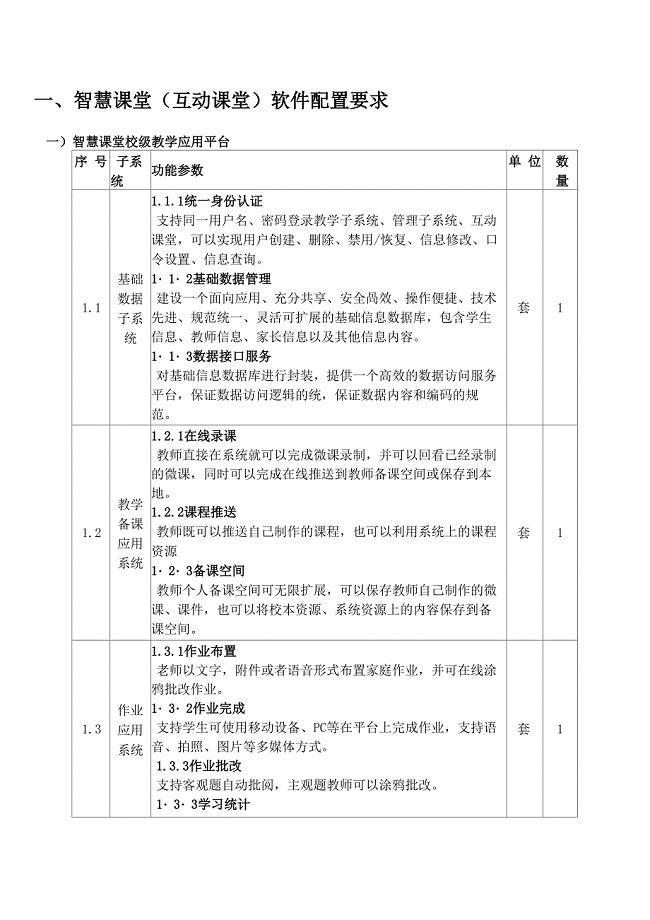

智慧课堂互动课堂软件配置要求

永城市社区公共服务项目分析报告

2023年大班教师个人工作计划(七篇).doc

单位工程竣工验收表常用

大连理工大学22春《外贸函电》综合作业一答案参考92

《班组现场管理》试题

人力资源管理师三级-培训与开发(课件)

人力资源管理师三级-培训与开发(课件)

2023-09-14 4页

职场中女职工的劳动保护

职场中女职工的劳动保护

2022-09-18 2页

![劳动合同法试题[1]](/Images/s.gif) 劳动合同法试题[1]

劳动合同法试题[1]

2023-06-29 6页

德国的秘书与秘书工作

德国的秘书与秘书工作

2023-04-02 3页

肉牛养殖场建设与设计(全)

肉牛养殖场建设与设计(全)

2023-12-31 14页

毕业设计(论文)_发动机水温不正常故障分析

毕业设计(论文)_发动机水温不正常故障分析

2023-10-20 62页

寿公司战略运营管理

寿公司战略运营管理

2022-07-26 40页

LinkeyBPM(业务流程管理)

LinkeyBPM(业务流程管理)

2024-02-25 2页

学校人事管理员工作流程

学校人事管理员工作流程

2023-12-19 8页

商铺工程施工设计方案

商铺工程施工设计方案

2023-11-15 82页