PCB课程设计--精选文档

10页1、PCB课程设计报告课题:8255并行口扩展设计学 院: 核工程与地球物理学院 班 级: 1221201 学 号: 201220120126 姓 名: 何鹏宇 目录一、 设计题目2二、设计内容与要求2三、设计目的意义2四、系统硬件电路图2五、程序流程图与源程序3六、系统功能分析与说明4七、设计体会8一、 设计题目8255并行口扩展控制系统设计。利用单片机AT89C52控制实现8255的PB口输出数据等于PA口输入数据。二、设计内容与要求 (1)利用单片机AT89C52与8255A设计一个扩展控制系统设计。(3)要求使用的元器件数目最少,电路尽可能简单。(4)电源电压为5V。三、设计目的意义1、 通过8255并行口扩展控制,进一步熟悉和掌握单片机的结构及工作原理,加深对单片机理论知识的理解;2、 掌握单片机内部功能模块的应用;3、 掌握单片机的接口及相关外围芯片的特性、使用与控制方法;4、 掌握单片机应用系统的构建和使用,为以后设计和实现单片机应用系统打下良好的基础。5、四、系统硬件电路图(1) 8255并行口扩展控制硬件电路原理图如下:图1:电路原理图三大元件: 各元件封装:(2) PC

2、B图如下:图2:PCB图五、程序流程图与源程序PB口输出PA状态开 始8255初始化读PA口状态5.1 程序流程图六、系统功能分析与说明6.1 总体功能实现说明本次设计单片机采用AT89C52,它是一种低功耗、高性能的8位CMOS微控制器。片内含有4KB的存储器(EPEROM),与8031引脚和指令系统完全兼容。89C52的VCC接+5V,VSS接地。复位引脚RESET外接RC电路和复位开关,可以实现人工复位。本系统采用按键电平复位,如硬件图所示。XTAL1和XTAL2引脚外接12MHZ晶振和两个30PF的电容。一般,单片机系统中高集成度芯片的电源端都应并联虑波电容,但此系统中只需扩展一个8255并对发光二极管进行控制,而不需要精确控制,所以没有接虑波电容。从系统实际运行情况看,没有接虑波电容未对系统稳定性造成影响。89C52单片机中,没有单独的地址总线和数据总线,而是和P0口和P2口公用的:P0口分时地作为低8位地址线和8位数据线用,P2口则作为高8位地址线用。所以有16条地址线和8条数据线,但要注意,他们不是独立的总线,而是和I/O端口合用的。本系统是扩展8255,用到了89C52

3、的P2口作为低8位地址线和数据线,通过寄存器74LS373连接到8255的的控制端口。本系统中要求实现8255的PB口输出数据等于PA口输入数据,我的做法是:在PA口接上开关,控制高低电平的变化;PB口则接上发光二极管,通过发光二极管的亮灭情况可知PB口的输出状态以及PA输入状态,从而达到系统的要求。为了很好地保护发光二极管,在每个发光二极管的回路上接上限流电阻,大小为1K,PA口的排阻大小为10K。当按下PA口的开关时,PB口相应的发光二极管将亮起。本设计可用于抢答器设计等领域。6.2 功能介绍 (1) ATM89C52主要功能特性: AT89C52是一个低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的Flash只读程序存储器和256 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器和Flash存储单元,AT89C52单片机在电子行业中有着广泛的应用。AT89C52有40个引脚,32个外部双向输入/输出(I/O)端口,同时内含2个外中断口,3个16位可编程定时

4、计数器,2个全双工串行通信口,2 个读写口线,AT89C52可以按照常规方法进行编程,也可以在线编程 VCC:供电电压。GND:接地。P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P0口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的低八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须接上拉电阻。P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为低八位地址接收。P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高

《PCB课程设计--精选文档》由会员pu****.1分享,可在线阅读,更多相关《PCB课程设计--精选文档》请在金锄头文库上搜索。

客服个人2023年终工作总结模板.doc

辅助用药采购使用管控措施

世界碳纤维巨头(东丽、东邦、西格里)综合实力透析上

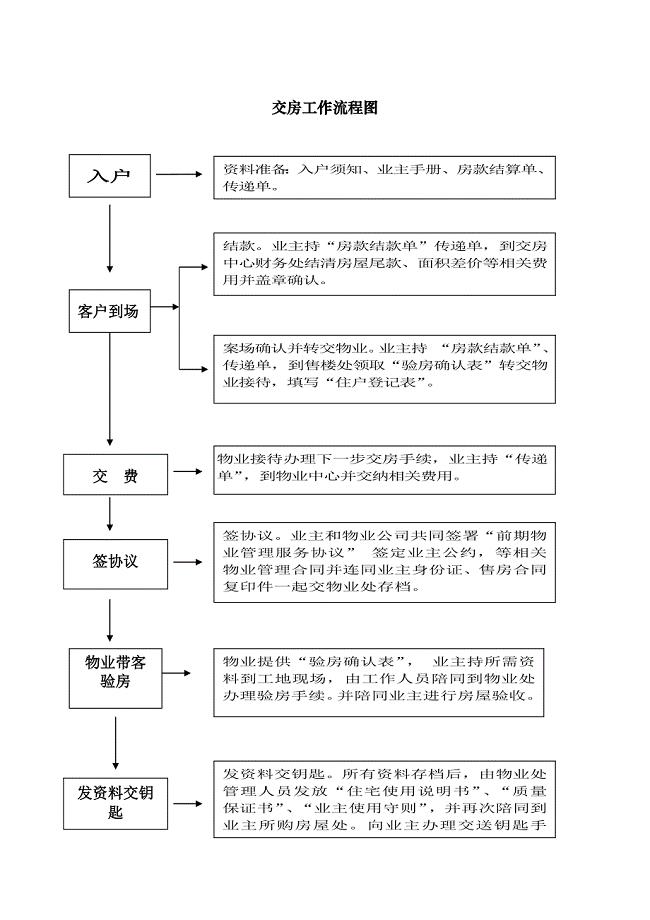

交房流程图drfs

现代人力资源管理与传统劳动人事管理的区别

九年级英语知识点-Unit-14

北京别墅项目

2023父亲节活动总结(2篇).doc

陕西化学制剂技术服务项目投资计划书_参考模板

2023年中级注册安全工程师之安全生产管理通关提分题库及完整答案

2022年02月四川内江市东兴区卫生计生系统考核招聘拟聘(第二批)历年参考题库答案解析

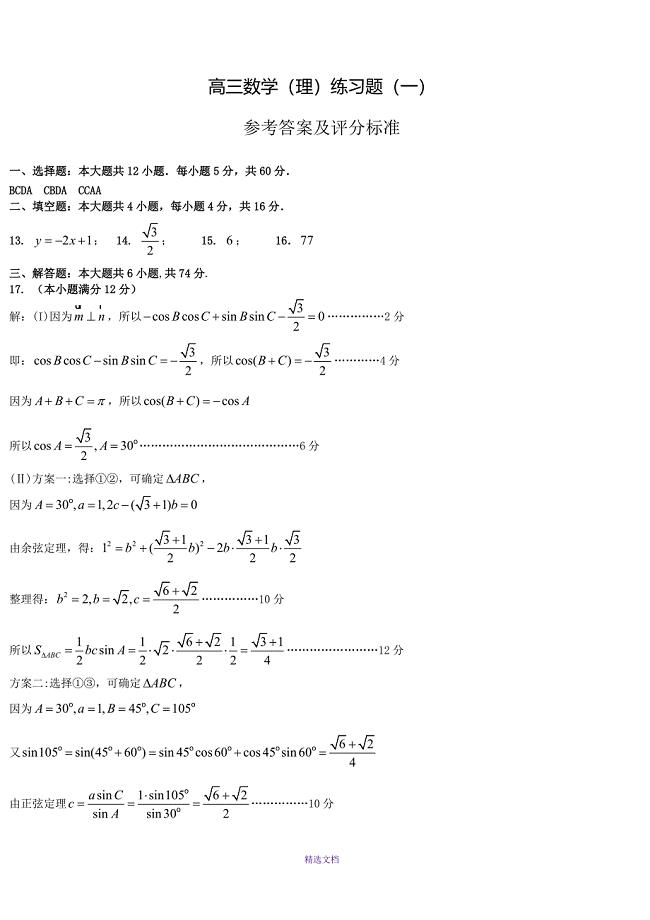

高三数学(理)练习题

猴子笑人读后感.doc

![最新[人教版] 小学6年级 数学上册 期末考试卷1](https://union.152files.goldhoe.com/2023-12/3/42670796-0488-4b2e-ac94-89ca361db285/pic1.jpg)

最新[人教版] 小学6年级 数学上册 期末考试卷1

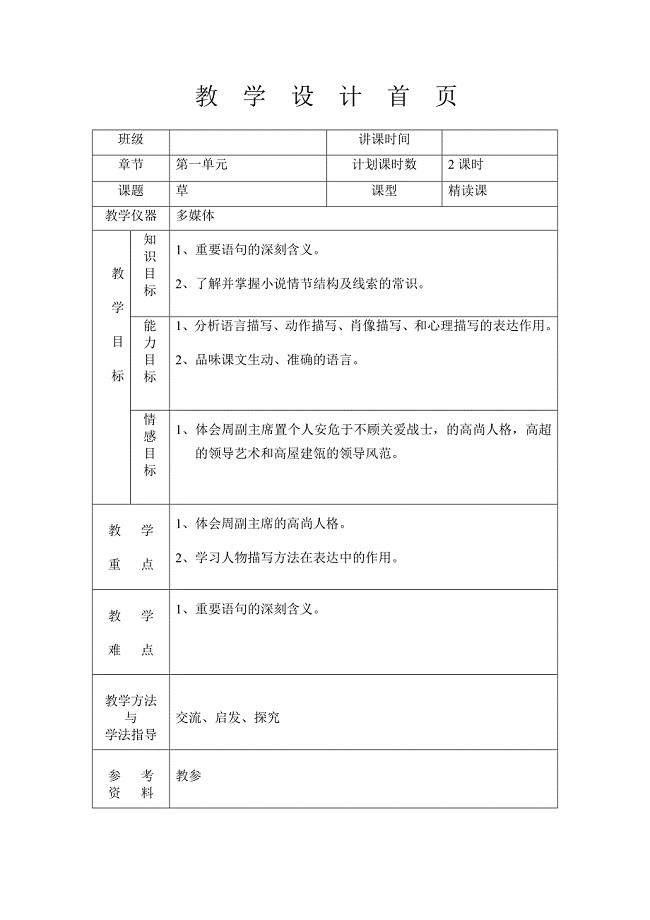

《草》教学设计

全新中秋节日活动方案

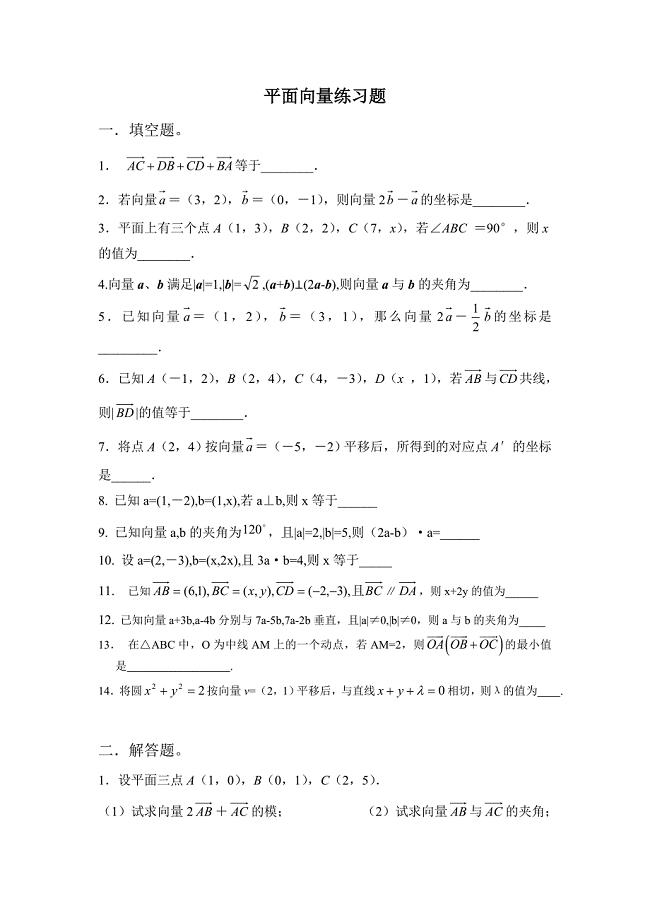

平面向量练习题(附答案)

初级银行从业《公司信贷》考前(难点+易错点剖析)押密卷答案参考28

火灾事故的应急预案(通用5篇)精选

圣诞节该怎样过

人口普查动员大会主持词.doc

人口普查动员大会主持词.doc

2023-06-10 2页

农村集体资产清产核资工作实施方案(三篇)

农村集体资产清产核资工作实施方案(三篇)

2023-08-07 34页

施工图设计说明书

施工图设计说明书

2023-06-25 7页

《计算机应用基础》自诊断报告.doc

《计算机应用基础》自诊断报告.doc

2023-10-16 9页

银行安保培训心得体会

银行安保培训心得体会

2023-08-10 15页

K线 组合图解--精选文档

K线 组合图解--精选文档

2023-08-26 28页

2021年银行“金融消费者权益日”宣传活动总结

2021年银行“金融消费者权益日”宣传活动总结

2022-12-26 4页

潇洒走上台(自学手册)

潇洒走上台(自学手册)

2023-03-16 21页

仪器仪表分类

仪器仪表分类

2023-05-17 5页

求职中判断公司好坏的13条技巧

求职中判断公司好坏的13条技巧

2023-11-02 5页