计算机组成原理zcyl(3)

17页1、计算机学院体系结构中心计算机学院体系结构中心由于CPU和主存储器之间在速度上是不匹配的,这种情况便成为限制高速计算机设计的主要问题。为了提高CPU和主存之间的数据传输率,除了主存采用更高速的技术来缩短读出时间外,还可以采用并行技术的存储器。3.5 并行存储器并行存储器2024/5/8计算机学院体系结构中心计算机学院体系结构中心3.5.1 双端口存储器 1、双端口存储器的逻辑结构 双端口存储器由于同一个存储器具有两组相互独立的读写控制电路而得名。由于进行并行的独立操作,因而是一种高速工作的存储器,在科研和工程中非常有用。举例说明,双端口存储器IDT7133的逻辑框图。如下页图。3.5 并行存储器并行存储器2024/5/8计算机学院体系结构中心计算机学院体系结构中心IDT71332K16的SRAM3.5 并行存储器并行存储器2024/5/8计算机学院体系结构中心计算机学院体系结构中心2、无冲突读写控制、无冲突读写控制 当两个端口的地址不相同时,在两个端口上进行读写操作,一定当两个端口的地址不相同时,在两个端口上进行读写操作,一定不会发生冲突。当任一端口被选中驱动时,就可对整个存储器进不会发

2、生冲突。当任一端口被选中驱动时,就可对整个存储器进行存取,每一个端口都有自己的片选控制和输出驱动控制。行存取,每一个端口都有自己的片选控制和输出驱动控制。3.5 并行存储器并行存储器2024/5/8计算机学院体系结构中心计算机学院体系结构中心3.5 并行存储器并行存储器3、有冲突读写控制、有冲突读写控制当两个端口同时存取存储器同一存储单元时,便发生读写冲突。当两个端口同时存取存储器同一存储单元时,便发生读写冲突。为解决此问题,特设置了为解决此问题,特设置了BUSY标志。由片上的判断逻辑决定标志。由片上的判断逻辑决定对哪个端口优先进行读写操作,而暂时关闭另一个被延迟的对哪个端口优先进行读写操作,而暂时关闭另一个被延迟的端口。端口。1.CE判断判断:如果地址匹配且在如果地址匹配且在CE之前有效,片上的控制逻之前有效,片上的控制逻辑在辑在CEL和和CER之间进行判断来选择端口。之间进行判断来选择端口。2.地址有效判断地址有效判断:如果如果CE在地址匹配之前变低,片上的控在地址匹配之前变低,片上的控制逻辑在左、右地址间进行判断来选择端口。制逻辑在左、右地址间进行判断来选择端口。2024/5/8

《计算机组成原理zcyl(3)》由会员资****亨分享,可在线阅读,更多相关《计算机组成原理zcyl(3)》请在金锄头文库上搜索。

输油设备计算机辅助仿真系统

数显式顶板离层仪B

树立科学发展观(1)

数电组合逻辑电路应用举例、竞争冒险

数电实验0GOS6051型二踪示波器实验一常用电子仪器的使用练习

数电84第五版—康华光

数码裂隙灯图像系统操作

数理统计12主成分分析

数控系统的备份与还原训练

数控技术及应用清华版7数控机床进给伺服系统的控制原理

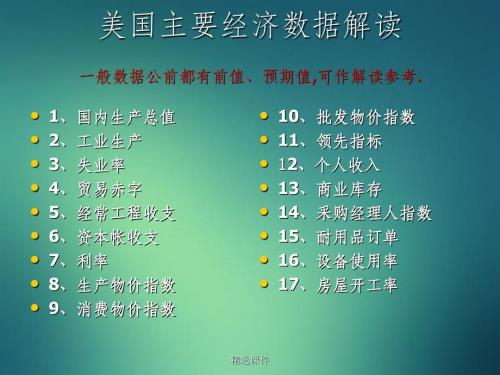

数据解读PPT(BNU金融协会)

数控技术及应用清华版8数控机床的精度

数控机床故障诊断 (2)

数据质量评估与控制体系-刘思琦组

数控技术及应用清华版17数控机床进给伺服系统的控制原理

数控技术2011-2-数控系统

数控加工工艺与设备》电子教案

数控加工的程序编制车床

数据通信与计算机网络第二版》电子教案西南

数据资料的收集方法

输油设备计算机辅助仿真系统

输油设备计算机辅助仿真系统

2024-05-14 5页

数显式顶板离层仪B

数显式顶板离层仪B

2024-05-14 6页

树立科学发展观(1)

树立科学发展观(1)

2024-05-14 40页

数电组合逻辑电路应用举例、竞争冒险

数电组合逻辑电路应用举例、竞争冒险

2024-05-14 38页

数电实验0GOS6051型二踪示波器实验一常用电子仪器的使用练习

数电实验0GOS6051型二踪示波器实验一常用电子仪器的使用练习

2024-05-14 15页

数电84第五版—康华光

数电84第五版—康华光

2024-05-14 22页

数码裂隙灯图像系统操作

数码裂隙灯图像系统操作

2024-05-14 31页

数理统计12主成分分析

数理统计12主成分分析

2024-05-14 42页

数控系统的备份与还原训练

数控系统的备份与还原训练

2024-05-14 23页

数控技术及应用清华版7数控机床进给伺服系统的控制原理

数控技术及应用清华版7数控机床进给伺服系统的控制原理

2024-05-14 25页