非常好的书PCB信号完整性设计

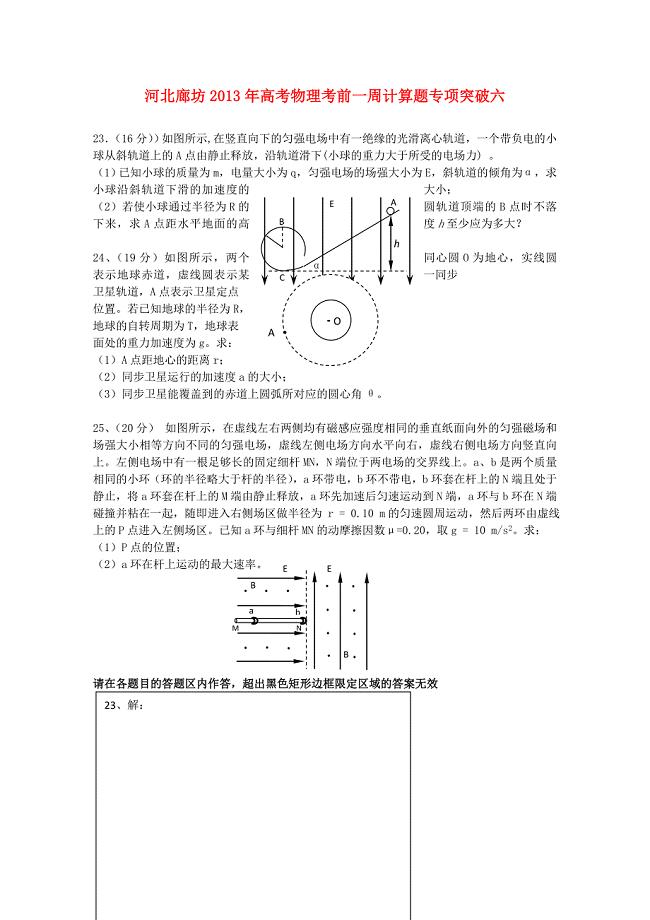

15页1、针对DDR2-800和DDR3的PCB信号完整性设计摘要本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数,特别是4层板的情况下的相关技术,其中一些设计方法在以前已经成熟的使用过。1. 介绍目前,比较普遍使用中的DDR2的速度已经高达800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已经高达1600 Mbps。对于如此高的速度,从PCB的设计角度来讲,要做到严格的时序匹配,以满足波形的完整性,这里有很多的因素需要考虑,所有的这些因素都是会互相影响的,但是,它们之间还是存在一些个性的,它们可以被分类为PCB叠层、阻抗、互联拓扑、时延匹配、串扰、电源完整性和时序,目前,有很多EDA工具可以对它们进行很好的计算和仿真,其中Cadence ALLEGRO SI-230 和Ansofts HFSS使用的比较多。表1: DDR2和DDR3要求比较表1显示了DDR2和DDR3所具有的共有技术要求和专有的技术要求。2. PCB的叠层(stackup)和阻抗对于一块

2、受PCB层数约束的基板(如4层板)来说,其所有的信号线只能走在TOP和BOTTOM层,中间的两层,其中一层为GND平面层,而另一层为 VDD 平面层,Vtt和Vref在VDD平面层布线。而当使用6层来走线时,设计一种专用拓扑结构变得更加容易,同时由于Power层和GND层的间距变小了,从而提高了PI。互联通道的另一参数阻抗,在DDR2的设计时必须是恒定连续的,单端走线的阻抗匹配电阻50 Ohms必须被用到所有的单端信号上,且做到阻抗匹配,而对于差分信号,100 Ohms的终端阻抗匹配电阻必须被用到所有的差分信号终端,比如CLOCK和DQS信号。另外,所有的匹配电阻必须上拉到VTT,且保持50 Ohms,ODT的设置也必须保持在50 Ohms。在 DDR3的设计时,单端信号的终端匹配电阻在40和60 Ohms之间可选择的被设计到ADDR/CMD/CNTRL信号线上,这已经被证明有很多的优点。而且,上拉到VTT的终端匹配电阻根据SI仿真的结果的走线阻抗,电阻值可能需要做出不同的选择,通常其电阻值在30-70 Ohms之间。而差分信号的阻抗匹配电阻始终在100 Ohms。图1 : 四层和六层

3、PCB的叠层方式3. 互联通路拓扑对于DDR2和DDR3,其中信号DQ、DM和DQS都是点对点的互联方式,所以不需要任何的拓扑结构,然而列外的是,在multi-rank DIMMs(Dual In Line Memory Modules)的设计中并不是这样的。在点对点的方式时,可以很容易的通过ODT的阻抗设置来做到阻抗匹配,从而实现其波形完整性。而对于 ADDR/CMD/CNTRL和一些时钟信号,它们都是需要多点互联的,所以需要选择一个合适的拓扑结构,图2列出了一些相关的拓扑结构,其中Fly- By拓扑结构是一种特殊的菊花链,它不需要很长的连线,甚至有时不需要短线(Stub)。对于DDR3,这些所有的拓扑结构都是适用的,然而前提条件是走线要尽可能的短。Fly-By拓扑结构在处理噪声方面,具有很好的波形完整性,然而在一个4 层板上很难实现,需要6层板以上,而菊花链式拓扑结构在一个4层板上是容易实现的。另外,树形拓扑结构要求AB的长度和AC的长度非常接近(如图2)。考虑到波形的完整性,以及尽可能的提高分支的走线长度,同事又要满足板层的约束要求,在基于4层板的DDR3设计中,最合理的拓扑结构

4、就是带有最少短线(Stub)的菊花链式拓扑结构。对于DDR2-800,这所有的拓扑结构都适用,只是有少许的差别。然而,菊花链式拓扑结构被证明在SI方面是具有优势的。对于超过两片的SDRAM,通常,是根据器件的摆放方式不同而选择相应的拓扑结构。图3显示了不同摆放方式而特殊设计的拓扑结构,在这些拓扑结构中,只有A和 D是最适合4层板的PCB设计。然而,对于DDR2-800,所列的这些拓扑结构都能满足其波形的完整性,而在DDR3的设计中,特别是在1600 Mbps时,则只有D是满足设计的。图2: 带有2片SDRAM的ADDR/CMD/CNTRL拓扑结构图3: 带有4片SDRAM的ADDR/CMD/CNTRL拓扑结构4. 时延的匹配在做到时延的匹配时,往往会在布线时采用trombone方式走线,另外,在布线时难免会有切换板层的时候,此时就会添加一些过孔。不幸的是,但所有这些弯曲的走线和带过孔的走线,将它们拉直变为等长度理想走线时,此时它们的时延是不等的,如图4所示。显然,上面讲到的trombone方式在时延方面同直走线的不对等是很好理解的,而带过孔的走线就更加明显了。在中心线长度对等的情况下,

《非常好的书PCB信号完整性设计》由会员cl****1分享,可在线阅读,更多相关《非常好的书PCB信号完整性设计》请在金锄头文库上搜索。

法院审理民事案件的相关知识

停车场安全管理制度参考范本(六篇)

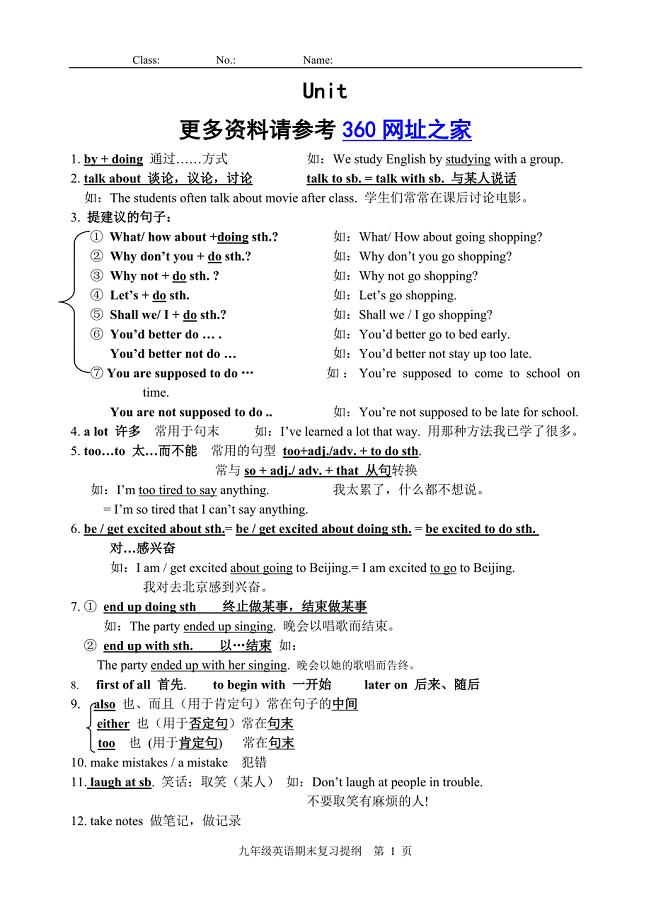

9年级1-10单元语法复习整理

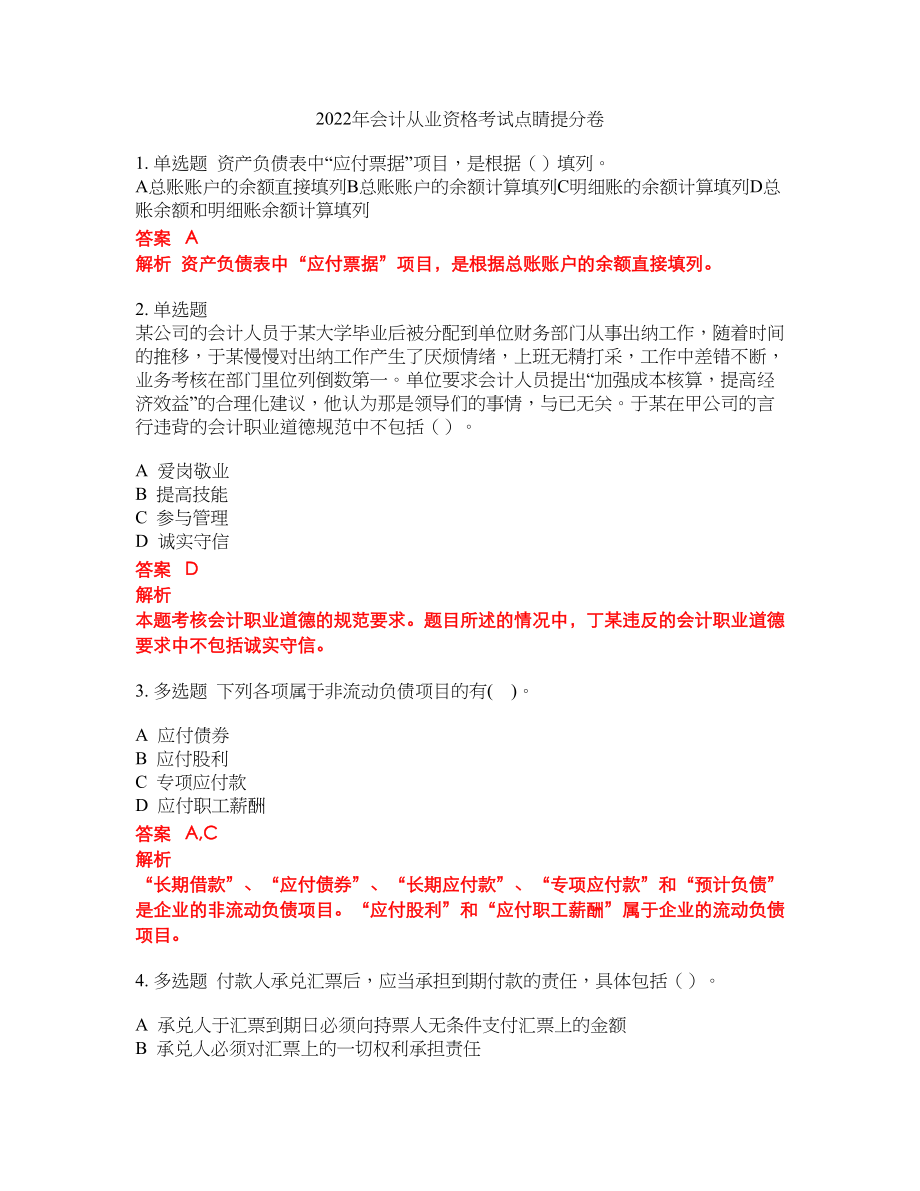

2022年会计从业资格考试点睛提分卷275

河北省廊坊2013年高考物理 考前一周计算题专项突破六

电气施工安全技术交底记录

简历中的座右铭

2023小学体育教师工作述职总结.doc

精品韶关市韶钢第一中学阶梯教室改造及装修音响平台项目12

攀枝花生物科研试剂技术应用项目招商引资方案【模板范文】

2023年小学生必读名著20本

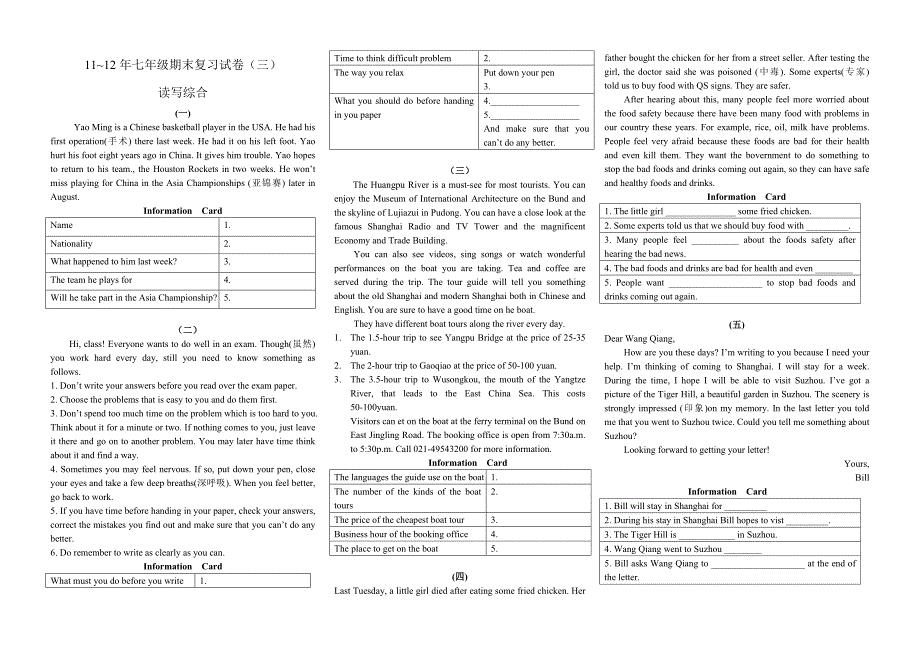

七年级复习试卷-看图填空和读写综合

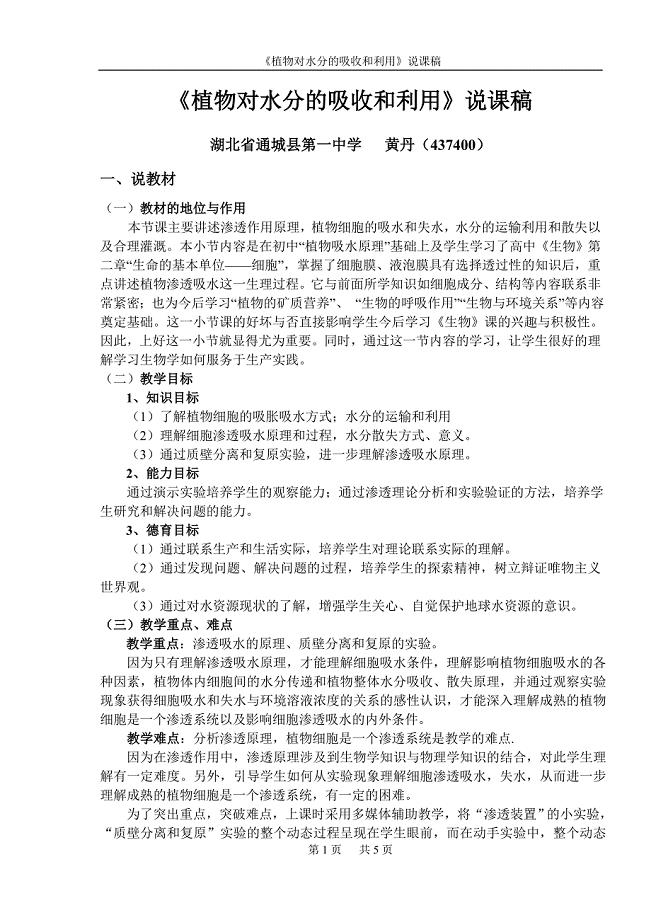

植物对水分的吸收和利用

工程建设招标投标合同官方版(4篇).doc

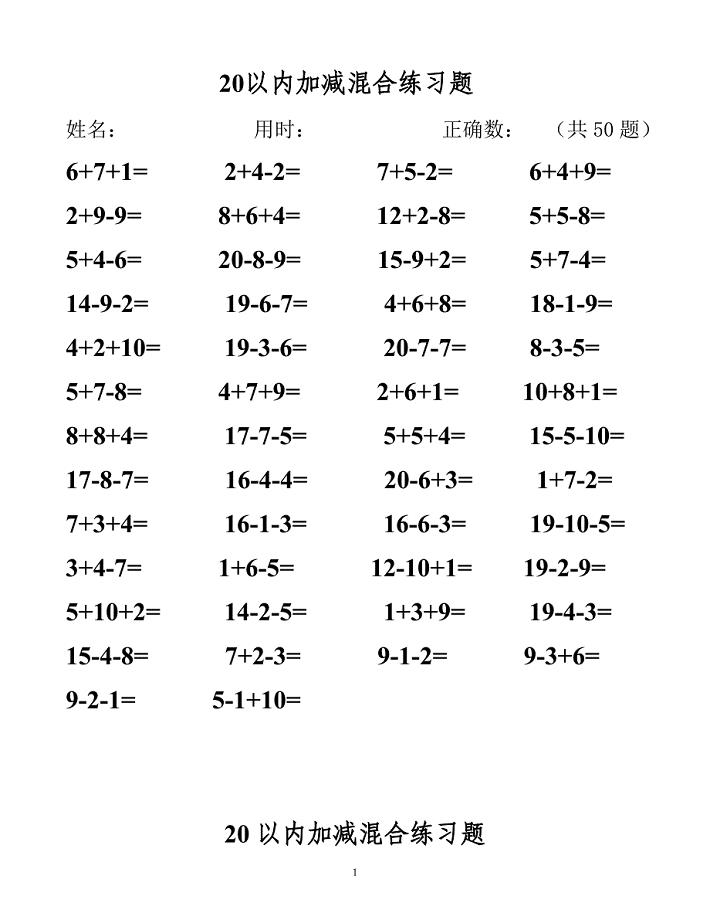

20以内加减法混合测试题(50道)

2022年秋季幼儿园教师个人工作总结

江苏省涟水县第四中学九年级物理上册11.3功学案无答案苏科版

教育法律法规:学生的权利与义务

红薯片项目资金申请报告写作模板-代写定制

临床医学检验相关专业知识考前突破试题附答案

课程整体设计与教学能力测试培训

课程整体设计与教学能力测试培训

2023-10-05 6页

林业站述职述 廉报告(精选多篇)

林业站述职述 廉报告(精选多篇)

2023-10-25 29页

普通电弧炉的设计与电极升降控制

普通电弧炉的设计与电极升降控制

2023-03-10 17页

2016年保密宣传月保密知识测试试题

2016年保密宣传月保密知识测试试题

2023-12-25 3页

新概念英语第一册全部语法.doc

新概念英语第一册全部语法.doc

2022-10-15 18页

高血压、糖尿病等慢性病健康管理评估报告.doc

高血压、糖尿病等慢性病健康管理评估报告.doc

2023-12-23 4页

机房巡检管理制度

机房巡检管理制度

2022-08-17 5页

行政管理流程设计及工作标准

行政管理流程设计及工作标准

2023-09-03 269页

《果品蔬菜加工工艺学》期末试题汇总.doc

《果品蔬菜加工工艺学》期末试题汇总.doc

2023-01-15 11页

不动产登记中心个人工作总结个人工作总结

不动产登记中心个人工作总结个人工作总结

2023-07-24 3页