IC设计面试笔试题目集合分类

21页1、编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页 共1页IC设计面试笔试题目集合分类 笔试/面试题目集合分类-IC设计基础1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。(仕兰微面试题目)2、FPGA和ASIC的概念,他们的区别。(未知)答案:FPGA是可编程ASIC。ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点模拟电路1、基尔霍夫定理的内容是什么?(仕兰微电子)2、平板电容公式(C=S/4kd)。(未知)3、最基本的如三极管曲线特性。(未知)4、描述反馈电路的概念,列举他们的应用。(仕兰微电子)5、负反馈种类(电压并联反馈,

2、电流串联反馈,电压串联反馈和电流并联反馈);负反馈馈 的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知)6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子)7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。(未知)8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。(凹凸)9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。(未知)10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。(未知)11、画差放的两个输入管。(凹凸)12、画出由运放构成加法、减法、微分、积分运算的电路原理图。并画出一个晶体管级的运放电路。(仕兰微电子)一三、用运算放大器组成一个10倍的放大器。(未知)14、给出一个简单电路,让你分析输出电压的特性(就是个积分电路),并求输出端某点的rise/fall时间。(Infineon笔试试题)一五、电阻R和电容C串联,输入电压为R和C之间的电压,输出电压分别为C上电压和R上电压,要求绘制

3、这两种电路输入电压的频谱,判断这两种电路何为高通滤波器,何为低通滤波器。当RC16、有源滤波器和无源滤波器的原理及区别?(新太硬件)17、有一时域信号S=V0sin(2pif0t)+V1cos(2pif1t)+V2sin(2pif3t+90),当其通过低通、带通、高通滤波器后的信号表示方式。(未知)一八、选择电阻时要考虑什么?(东信笔试题)19、在CMOS电路中,要有一个单管作为开关管精确传递模拟低电平,这个单管你会用P管还是N管,为什么?(仕兰微电子)20、给出多个mos管组成的电路求5个点的电压。(Infineon笔试试题)21、电压源、电流源是集成电路中经常用到的模块,请画出你知道的线路结构,简单描述其优缺点。(仕兰微电子)22、画电流偏置的产生电路,并解释。(凹凸)23、史密斯特电路,求回差电压。(华为面试题)24、晶体振荡器,好像是给出振荡频率让你求周期(应该是单片机的,12分之一周期.) (华为面试题)25、LC正弦波振荡器有哪几种三点式振荡电路,分别画出其原理图。(仕兰微电子)26、VCO是什么,什么参数(压控振荡器?) (华为面试题)27、锁相环有哪几部分组成?(仕兰微

4、电子)28、锁相环电路组成,振荡器(比如用D触发器如何搭)。(未知)29、求锁相环的输出频率,给了一个锁相环的结构图。(未知)30、如果公司做高频电子的,可能还要RF知识,调频,鉴频鉴相之类,不一一列举。(未知)31、一电源和一段传输线相连(长度为L,传输时间为T),画出终端处波形,考虑传输线无损耗。给出电源电压波形图,要求绘制终端波形图。(未知)32、微波电路的匹配电阻。(未知)33、DAC和ADC的实现各有哪些方法?(仕兰微电子)34、A/D电路组成、工作原理。(未知)35、实际工作所需要的一些技术知识(面试容易问到)。如电路的低功耗,稳定,高速如何做到,调运放,布版图注意的地方等等,一般会针对简历上你所写做过的东西具体问,肯定会问得很细(所以别把什么都写上,精通之类的词也别用太多了),这个东西各个人就不一样了,不好说什么了。(未知)_数字电路1、同步电路和异步电路的区别是什么?(仕兰微电子)2、什么是同步逻辑和异步逻辑?(汉王笔试)同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。3、什么是线与逻辑,要实现它,在硬件特性上有什么具体要求?(汉王笔试)线与

《IC设计面试笔试题目集合分类》由会员大米分享,可在线阅读,更多相关《IC设计面试笔试题目集合分类》请在金锄头文库上搜索。

2023年关于写景作文的素材4篇语文作文素材写景

老乡联谊活动策划书(四)

机动车维修经营备案所需全全资料、材料实用模板和受理条件

岩浆岩野外描述

年会计年度工作计划范文

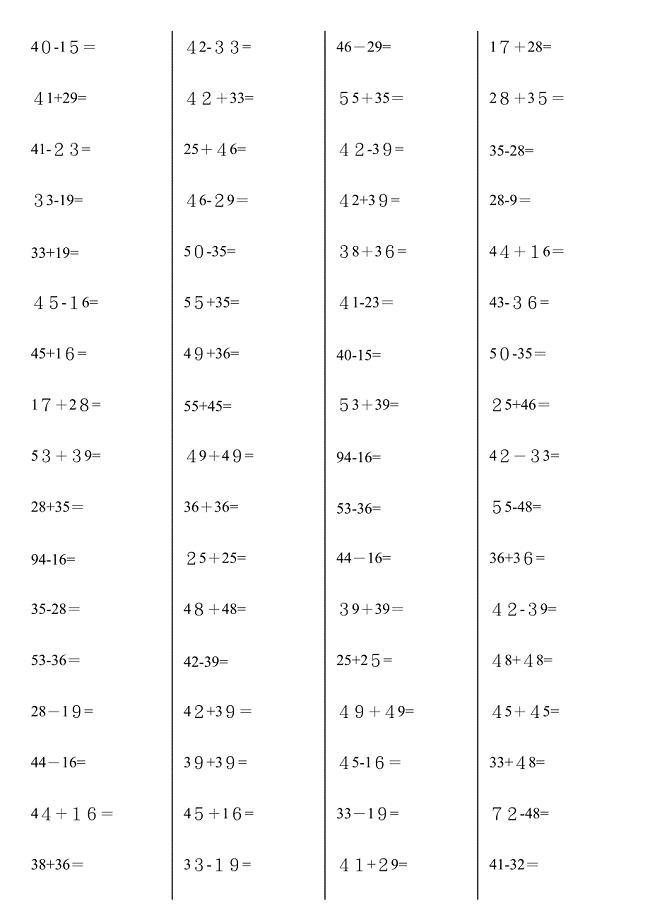

100以内两位数进位加法和退位减法计算题

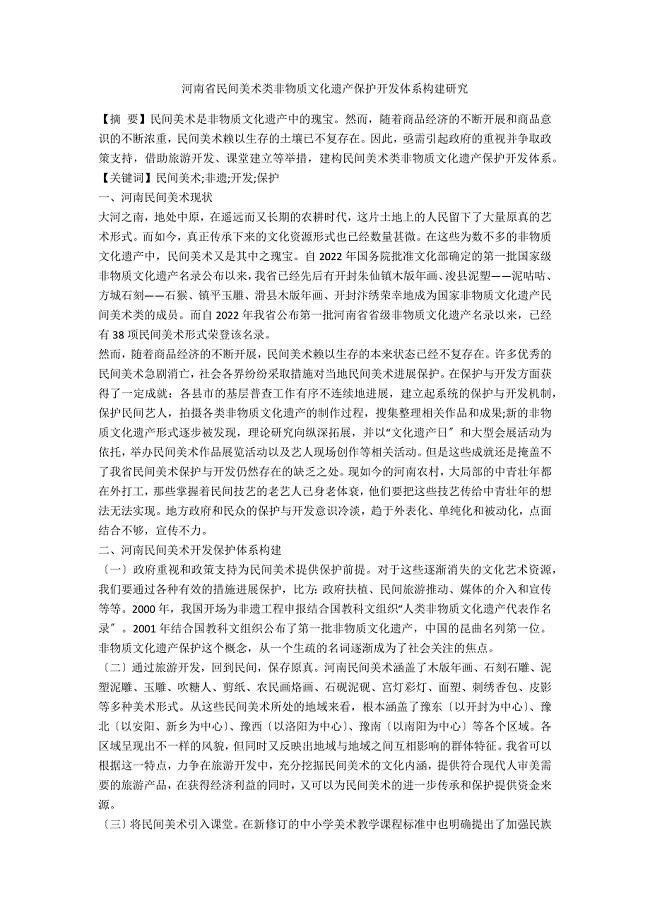

河南省民间美术类非物质文化遗产保护开发体系构建研究

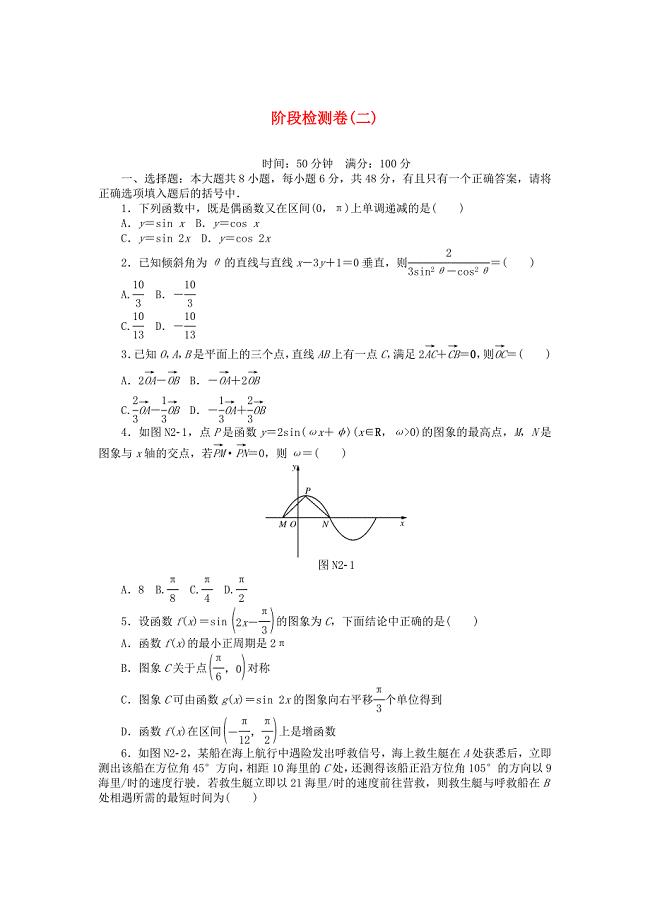

2019版高考数学一轮复习阶段检测卷二理

露天采矿课程设计说明

高中排列组合问题的解答技巧和记忆方法

农村建房申请书

传染病防控及食品安全检查总结

思南县科协财务管理制度

小学生怎样才能学好语文

《动物农庄》读书笔记

环境评价师《环境影响评价相关法律法规》资格考试内容及模拟押密卷含答案参考48

班组长技术比武学习提纲

大桥高墩爬模工程安全专项施工方案培训资料(DOC 34页)

城排水管网建设工程项目可行性研究报告

2022年最新人教版六年级数学下册期末测试题(3套)

深圳龙岗路污水管线改造施工方案

深圳龙岗路污水管线改造施工方案

2023-05-19 29页

2023年学校停课不停学个人工作总结(三篇).doc

2023年学校停课不停学个人工作总结(三篇).doc

2022-08-11 6页

新版大学生寒假实习总结:广告设计实习

新版大学生寒假实习总结:广告设计实习

2023-04-11 3页

酒店员工转正申请范文

酒店员工转正申请范文

2023-10-25 2页

优思达KTV量贩会员储值卡管理制度

优思达KTV量贩会员储值卡管理制度

2023-08-25 53页

保安年终考核个人工作总结范文

保安年终考核个人工作总结范文

2023-01-15 2页

传染病防控及食品安全检查总结

传染病防控及食品安全检查总结

2022-09-12 6页

腊八节活动总结参考样本(3篇).doc

腊八节活动总结参考样本(3篇).doc

2024-02-09 4页

走过才明白记叙文

走过才明白记叙文

2022-08-14 8页

人事科年终工作总结模板(4篇).doc

人事科年终工作总结模板(4篇).doc

2023-07-13 11页