VHDL音乐播放器

20页1、洛 阳 理 工 学 院课 程 设 计 报 告课程名称EDA 技术与 VHDL设计题目音乐播放器的设计与仿真专业通信工程班级B1105学号B1105姓名完成日期2014 年 12 月 22 日前言随着科学技术的进步,电子器件和电子系统设计方法日新月异,电子设计自动化(Electronics Design Automation ,EDA)技术正是适应了现代电子产品设计的要求,吸收了多学科最新成果而形成的一门新技术。 现如今掌握 EDA技术是电子信息类专业的学生、工程技术人员所必备的基本能力和技能。传统电子电路的设计, 首先要对系统进行分析, 然后按功能对系统进行划分,接下来就要选择特定芯片, 焊接成 PCB电路板,最后对成品 PCB电路板进行调试。这样的设计没有灵活性可言, 搭成的系统需要的芯片种类多且数目大, 而且对于电路图的设计和电路板的设计都需要很大的工作量, 工作难度也很高。 随着可编程器件和 EDA技术的发展,传统设计的劣势被克服, 采用可编程逻辑器件基于芯片的设计方法, 期间的内部逻辑和引脚可以由设计者自行决定, 提高了设计的灵活性和工作效率;同时,将系统集成在一个芯片上的设计

2、,使系统具有体积小、功耗低、可靠性高等特点。EDA技术即电子设计自动化技术, 它是以可编程逻辑器件 (PLD)为载体,以硬件描述语言 (HDL)为主要的描述方式,以 EDA软件为主要的开发软件的电子设计过程。它主要采用“自顶向下”的设计方法,设计流程主要包括:设计输入、综合、仿真、适配、下载。EDA技术主要有以下特征:(1)高层综合的理论和方法取得进展,从而将EDA设计层次由 RT级提高到了系统级,并推出了系统级综合优化工具,缩短了复杂ASIC 的设计周期。( 2)采用硬件描述语言来描述10 万门以上的设计,并形成了VHDL和Verilog-HDL 两种标准硬件描述语言。(3)采用平面规划技术对逻辑综合和物理版图设计联合管理,做到在逻辑设计综合早期阶段就考虑到物理设计信息的影响。(4)可测性综合设计。(5)为带有嵌入式IP 核的 ASIC设计提供软、硬件协同设计工具。(6)建立并设计工具框架结构的集成化设计环境,以适应当今ASIC 规模大而复杂、数字与模拟电路并存、硬件与软件设计并存、产品上市速度快等特点。总而言之, EDA技术的出现,给电子信息产业带来了革命性的变革。一.设计任务及要

《VHDL音乐播放器》由会员m****分享,可在线阅读,更多相关《VHDL音乐播放器》请在金锄头文库上搜索。

猪传染性萎缩性鼻炎的几种新疗法

【最新】九年级化学下册第十单元化学与降综合测试鲁教版

教师年度考核自我鉴定

家长会家长发言稿范文(3篇)

2023学校财务年终工作总结模板(4篇).doc

莫尔道嘎边防派出所建设项目工程施工投标文件

抗车撤剂项目申请报告写作参考模板

品牌原理与品牌构成元素

2022精选关于试用期辞职信范文2篇(试用期辞职用写辞职信吗)

借贷纠纷刑法边界与刑事规制分析

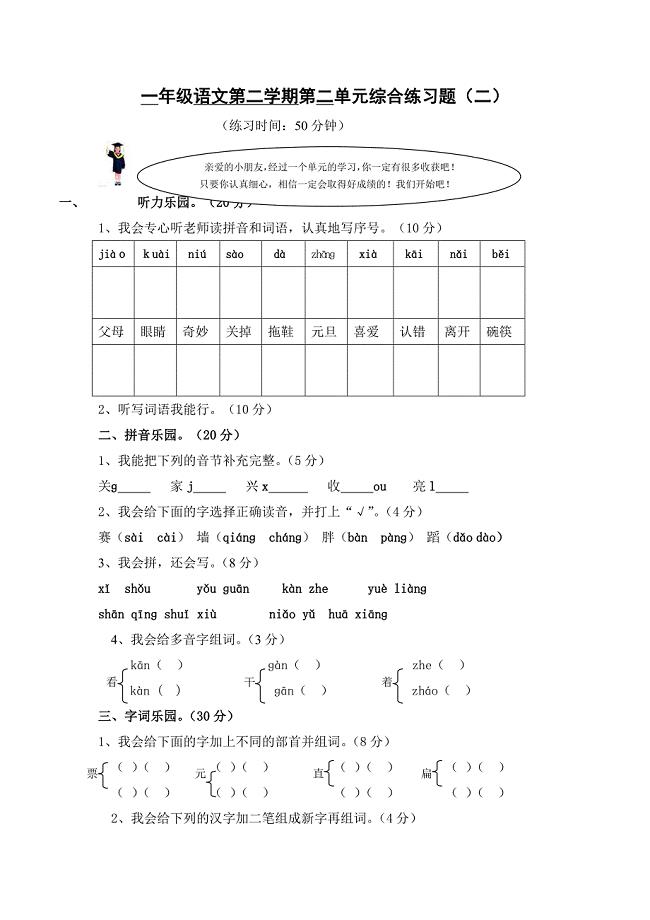

一年级语文科第二单元综合题

城市路灯节能设计标准

![工程热力学复习题[优选试题]](https://union.152files.goldhoe.com/2022-8/21/01f3410a-e373-4b71-bbbe-a6570da22182/pic1.jpg)

工程热力学复习题[优选试题]

优秀班组长培训心得总结(三篇).doc

高压电气容器罐体项目资金申请报告模板定制

研发组织管理制度

20XX中学总务处工作总结

电器维修设备标书

电气安装工程施工设计方案

校园真美作文范文300字(14篇)

细胞生物学复习题全

细胞生物学复习题全

2022-09-20 29页

某县“七五”普法中期工作汇报材料

某县“七五”普法中期工作汇报材料

2023-01-30 9页

东莞城区商业项目市场调研分析报告(47页).doc

东莞城区商业项目市场调研分析报告(47页).doc

2023-01-20 48页

小学宪法演讲比赛主持词2篇

小学宪法演讲比赛主持词2篇

2023-04-24 8页

年产30万吨甲醇生产工艺初步设计.doc

年产30万吨甲醇生产工艺初步设计.doc

2024-01-15 159页

安全生产_幼儿园安全教材

安全生产_幼儿园安全教材

2023-07-01 31页

(最新整理)受伤游客处理流程

(最新整理)受伤游客处理流程

2023-03-05 2页

高边坡脚手架专项施工方案

高边坡脚手架专项施工方案

2022-08-14 18页

煤化工公司气柜基础及气柜水封房工程竣工验收报告.doc

煤化工公司气柜基础及气柜水封房工程竣工验收报告.doc

2023-08-07 26页

2013年搜集某一上市公司近期的资产负债表和利润表-试计算如下指标并加以分析.doc

2013年搜集某一上市公司近期的资产负债表和利润表-试计算如下指标并加以分析.doc

2023-05-17 5页