vhdl基本语法(简略共34页)

49页1、VHDL硬件描述语言1.1 VHDL概述1.1.1 VHDL的特点VHDL语言作为一种标准的硬件描述语言,具有结构严谨、描述能力强的特点,由于VHDL语言来源于C、 Fortran 等计算机高级语言,在VHDL 语言中保留了部分高级语言的原语句,如if 语句、子程序和函数等,便于阅读和应用。具体特点如下:1. 支持从系统级到门级电路的描述,既支持自底向上(bottom-up )的设计也支持从顶向下( top-down )的设计,同时也支持结构、行为和数据流三种形式的混合描述。2. VHDL 的设计单元的 基本组成部分是实体( entity )和结构体( architecture),实体包含设计系统单元的输入和输出端口信息,结构体描述设计单元的组成和行为,便于各模块之间数据传送。 利用单元( componet)、块( block )、过程( procure)和函数( function )等语句,用结构化层次化的描述方法,使复杂电路的设计更加简便。采用包的概念,便于标准设计文档资料的保存和广泛使用。3. VHDL 语言有常数、信号和变量三种数据对象,每一个数据对象都要指定数据类型, VHD

2、L的数据类型丰富,有数值数据类型和逻辑数据类型,有位型和位向量型。既支持预定义的数据类型,又支持自定义的数据类型,其定义的数据类型具有明确的物理意义,VHDL是强类型语言。4. 数字系统有组合电路和时序电路,时序电路又分为同步和异步,电路的动作行为有并行和串行动作, VHDL 语言常用语句分为并行语句和顺序语句,完全能够描述复杂的电路结构和行为状态。1.1.2 VHDL语言的基本结构VHDL语言是数字电路的硬件描述语言,在语句结构上吸取了Fortran 和 C 等计算机高级语言的语句,如IF 语句、循环语句、函数和子程序等,只要具备高级语言的编程技能和数字逻辑电路的设计基础,就可以在较短的时间内学会VHDL 语言。但是VHDL毕竟是一种描述数字电路的工业标准语言,该种语言的标识符号、数据类型、数据对象以及描述各种电路的语句形式和程序结构等方面具有特殊的规定,如果一开始就介绍它的语法规定,会使初学者感到枯燥无味,不得要领。较好的办法是选取几个具有代表性的VHDL 程序实例,先介绍整体的程序结构,再逐步介绍程序中的语法概念。一个 VHDL 语言的设计程序描述的是一个电路单元,这个电路单元可

3、以是一个门电路,或者是一个计数器,也可以是一个CPU。一般情况下,一个完整的VHDL 语言程序至少要包含程序包、实体和结构体三个部分。实体给出电路单元的外部输入输出接口信号和引脚信息,结构体给出了电路单元的内部结构和信号的行为特点, 程序包定义在设计结构体和实体中将用到的常数、数据类型、子程序和设计好的电路单元等。一位全加器的逻辑表达式是:S=A B CiCo=AB+ACi+BCi全加器的 VHDL 程序的文件名称是 fulladder.VHD ,其中 VHD 是 VHDL 程序的文件扩展名,程序如下:LIBRARY IEEE;-IEEE 标准库USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY fulladder IS- fulladder 是实体名称PORT(A, B, Ci : IN STD_LOGIC; -定义输入 /输出信号Co, S : OUT STD_LOGIC);END fulladder;是结构体名BEGINS = A XOR B

《vhdl基本语法(简略共34页)》由会员枫**分享,可在线阅读,更多相关《vhdl基本语法(简略共34页)》请在金锄头文库上搜索。

八年级数学教学设计:正方形7

四六级英语听力25必备词汇

南开大学22春《生产运营管理》补考试题库答案参考28

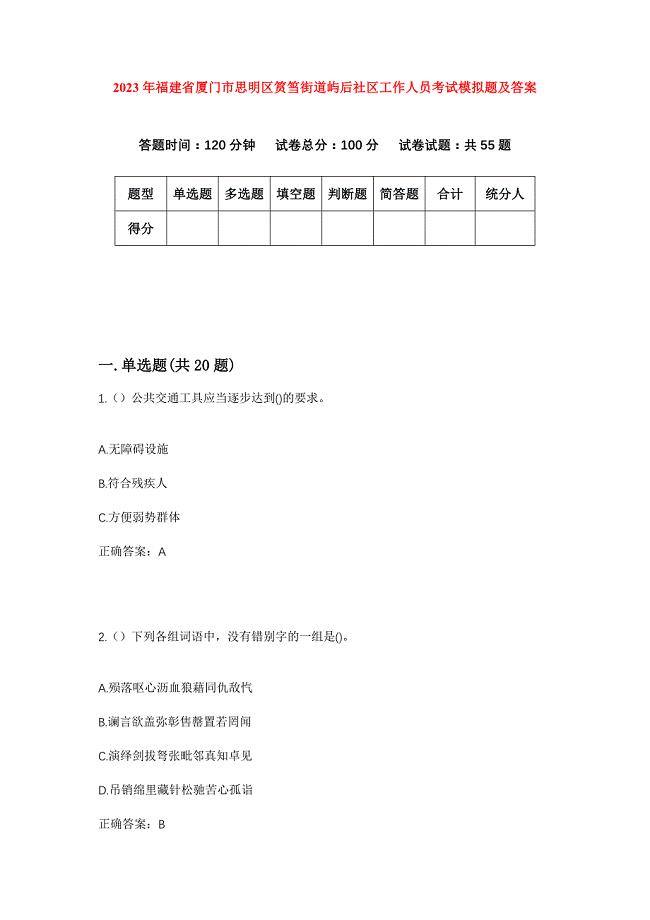

2023年福建省厦门市思明区筼筜街道屿后社区工作人员考试模拟题及答案

餐厅服务员国家职业标准

物业管理公司节约用电规定

2007年春06级外语听力课表汇总

石化施工安全规范

定州市智慧社区项目创业计划书

有效支持主产区保证粮食安全

汽车维修高级技能岗位分析与设计

2023年度工作总结优秀结尾(3篇).doc

春节促销方案(雅客V9)-成功案例

南京家庭储能产品项目招商引资方案(模板范本)

数字存储示波器的原理及使用

有关同学聚会倡议书三篇

2022年高一下学期期中教学质量调查语文试题含答案

商标恶意注册的法律规制(共3页)

中秋节英文作文400字

小学四年级语文教学随笔集锦小学四年级下学期班主任工作计划

StarterUnit1Goodmorning素材

StarterUnit1Goodmorning素材

2023-10-17 2页

译林英语3BU1考点精练

译林英语3BU1考点精练

2023-09-16 6页

2017考研英语高频词汇(选自历年真题)

2017考研英语高频词汇(选自历年真题)

2022-08-24 54页

英语手抄报比赛方案

英语手抄报比赛方案

2023-03-16 2页

石油英语词汇d4

石油英语词汇d4

2023-06-26 35页

英语专业实习心得体会的范文

英语专业实习心得体会的范文

2023-06-19 11页

中国石油大学英语四第三次作业

中国石油大学英语四第三次作业

2024-02-06 5页

大学英语四级试题听力理解及注释

大学英语四级试题听力理解及注释

2023-11-05 7页

大学英语二考题大纲

大学英语二考题大纲

2023-01-07 5页

英语新课改与素质教育

英语新课改与素质教育

2023-07-31 4页