基于FPGA的数字秒表的设计毕业论文

56页1、基于 FPGA 的数字秒表的设计第 1 章绪 论电子设计的必由之路是数字化已成为共识。在数字化的道路上,我国电子设计技术的发展经历了,并将继续经历许多重大的变革与飞跃、从应用 SSI 通用数字电路芯片构成电路系统,到广泛地应用 MCU(微控制器或单片机),在电子系统设计上发生厂具有里程碑意义的飞跃,这一飞跃不但克服了纯 SSI 数字电路系统许多不可逾越的困难,同时也为电子设计技术的应用开拓了更广阔的前景。它使得电子系统的智能化水平在广度和深度上产生了质的飞跃。MCU 的广便应用并没有抛弃 SSI 的应用,而是为它们在电于系统中找到了更合理的地位。随着社会经济发展的延伸、各类新型电子产品的开发为我们提出了许多全新的课题和更高的要求。FPGA/CPLD(现场可编程逻辑器件复杂可编程逻辑器件)在 EDA 基础上的广泛应用从某种意义上说,新的电子系统运转的物理机制又将回到原来的纯数字电路结构,但这是种更高层次的循环,应是一次否定之否定的运动, 它在更高层次上容纳了过去数字技术的优秀部分,对 MCU 系统将是种扬弃, 但在电子设计的技术操作和系统构成的整体上却发生质的飞跃。如果说 MCU 在逻辑

2、的实现上是无限的话,那么高速发展的FPGA/CPLD 不但包括了 MCU 这一特点,并兼有串、并工作方式和高速、高可靠性以及宽口径适用等诸多方面的特点、不仅如此,随着EDA 技术的发展和 FPGACPLD 在深亚微米领域的进军、它们与 MCU、MPU、DSP、AD、DA、RAM 和 ROM 等独立器件问的物理与功能界限正日趋模糊。特别是软硬 IP 芯核产业的迅猛发展,嵌入式通用与标准 CPLD 和 FPGA 器件的出现,片上系统已近在咫尺。以大规模集成电路为物质基础的 EDA 技术终于打破了软硬件之间最后的屏障,使软硬件工程师们有了共同的语言1。1.1 课题背景当前电子系统的设计正朝着速度快,容量大,体积小,质量轻,用电省的方向发展。推动该潮流迅速发展的决定性因素就是使用了现代化的 EDA 设计工具。EDA 是电子设计自动化(Electronic Design Automation)的缩写,是 90 年代初,从CAD(计算机辅助没计)、CAM(算机辅助制造)、CAT(计算机辅助测试)和 CAE(计算机辅助工程)的概念发展而来的。EDA 技术就是以计算机为工具,在 EDA 软件平台上,对

3、以硬件描述语言 HDL 为系统逻辑描述手段完成的设计文件自动地完成逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑行局布线、逻辑仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。设计者的工作仅限于利用软件的方式,即利用硬件描述语言来完成对系统硬件功能的描 述,在 EDA 工具的帮助下就可以得到最后的设计结果。尽管目标系统是硬件, 但整个设计和修改过程如同完成软件设计一样方便和高效2。EDA 技术中最为瞩目的功能,即最具现代电子设计技术特征的功能就是日益强大的逻辑设计仿真测试技术。EDA 仿真测试技术只需通过计算机就能对所设计的电子系统从各种不同层次的系统性能特点完成一系列准确的测试与仿真操作,在完成实际系统的安装后还能对系统上的目标器件进行所谓边界扫锚测试。这一切都极大地提高了大规模系统电子设计的自动化程度。另一方面,高速发展的 CPLD/FPGA 器件又为 EDA 技术的不断进步奠定可坚实的物质基础。CPLD/FPGA 器件更广泛的应用及厂商间的竞争,使得普通的设计人员获得廉价的器件和 EDA 软件成为可能。现代的 EDA 工具软件已突破了早期仅能进行 PCB 版图设

4、计,或类似某些仅限于电路功能模拟的、纯软件范围的局限,以最终实现可靠的硬件系统为目标, 配备了系统设计自动化的全部工具。如配置了各种常用的硬件描叙平台 VHDL、Verilog HDL、ABEL HDL 等;配置了多种能兼用和混合使用的逻辑描述输入工具,如硬件描述语言文本输入法(其中包括布尔方程描述方式、原理图描述方式、状态图描述方式等)以及原理图输入法、波形输入法等;同时还配置了高性能的逻辑综合、优化和仿真模拟工具3。1.2 硬件描述语言硬件描述语言(Hardware Description Language)是硬件设计人员和电子设计自动化(EDA)工具之间的界面。其主要目的是用来编写设计文件,建立电子 系统行为级的仿真模型。即利用计算机的巨大能力对用erilog HDL 或VHDL 建模的复杂数字逻辑进行仿真,然后再自动综合以生成符合要求且在电路结构上可以实现的数字逻辑网表( Netlist),根据网表和某种工艺的器件自动生成具体电路,然后生成该工艺条件下这种具体电路的延时模型。仿真验证无误后,用于制造 ASIC 芯片或写入 CPLD 和 FPGA 器件中。随着 PC 平台上的 E

《基于FPGA的数字秒表的设计毕业论文》由会员小鱼****猫分享,可在线阅读,更多相关《基于FPGA的数字秒表的设计毕业论文》请在金锄头文库上搜索。

基于nRF2401模块的无线温度监测系统设计_毕业论文

庄浪县梯田农业生态-经济效益分析_毕业论文

基于JAVA的航空售票系统毕业论文 (1)

楼宇智能化本科毕业论文

六轴工具磨床转动平台设计毕业论文设计

基于bs模式的酒店住宿管理系统的设计与实现

基于MODBUS协议的通讯系统_毕业设计论文

基于FPGA的数字秒表的设计毕业论文

基于FPGA的串口设计_毕业设计论文

基于fpga技术的数字存储示波器设计

酒店就业大学生流失现象的透析及对策研究—毕业论文

建筑工程项目质量控制研究毕业论文

交通灯控制系统模拟设计_毕业设计论文

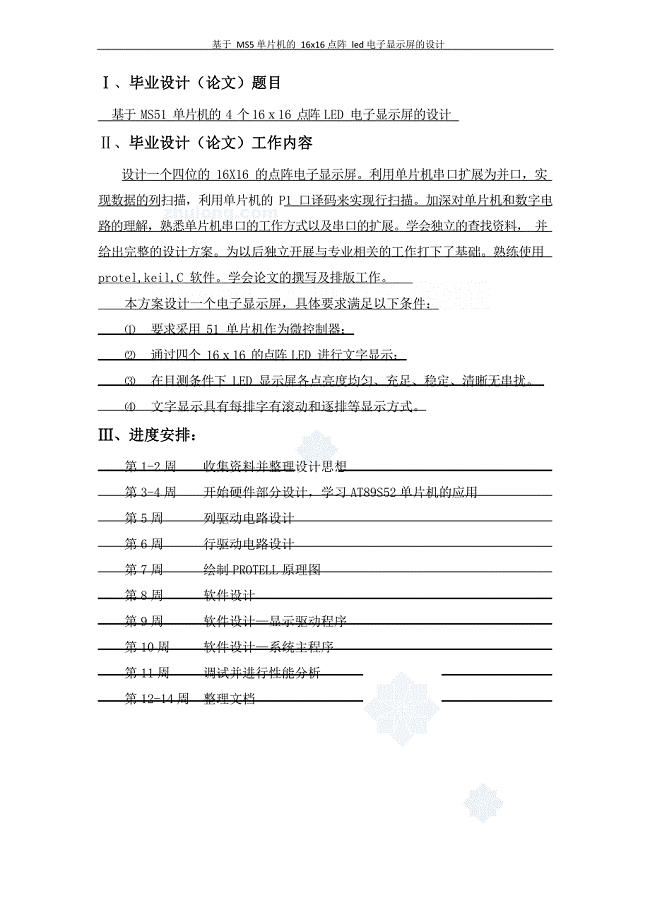

基于MS5单片机的16x16点阵led电子显示屏的设计本科毕业设计

基于MATLAB的电力系统故障分析与仿真_毕业论文设计

Android毕业设计论文

教学用小型数控钻铣床设计说明书论文

基于FX系列PLC的机械手传送带设计本科毕业设计

基于LabVIEW的科学计算器毕业设计

链驱动双层升降横移式立体车库设计毕业论文

毕业设计(论文)-具有安防监测功能门禁系统中门禁控制器的设计

毕业设计(论文)-具有安防监测功能门禁系统中门禁控制器的设计

2022-08-07 86页

客运从业资格证模拟考试题附答案2016年

客运从业资格证模拟考试题附答案2016年

2023-09-13 11页

![数控车床上下工件机械手设计论文[带图纸].doc](/Images/s.gif) 数控车床上下工件机械手设计论文[带图纸].doc

数控车床上下工件机械手设计论文[带图纸].doc

2023-12-09 37页

电子技术基础课程设计-交通灯控制器的设计

电子技术基础课程设计-交通灯控制器的设计

2022-09-03 15页

公共关系管理在企业中的价值

公共关系管理在企业中的价值

2022-10-28 18页

机电一体化课程设计-铣床X-Y数控工作台机电系统设计

机电一体化课程设计-铣床X-Y数控工作台机电系统设计

2022-08-29 19页

毕业设计(论文)-镇江某综合建筑空调系统设计

毕业设计(论文)-镇江某综合建筑空调系统设计

2022-09-28 46页

幼儿园组织构架图

幼儿园组织构架图

2023-12-05 19页

市政道路施工组织设计

市政道路施工组织设计

2023-12-02 74页

毕业设计(论文)-基于PLC的霓虹灯控制系统设计

毕业设计(论文)-基于PLC的霓虹灯控制系统设计

2023-09-11 43页