基于FPGA的串口设计_毕业设计论文

49页1、目录基于 FPGA 的串口设计目录任务书开题报告指导教师审查意见评阅教师评语答辩会议记录中文摘要外文摘要前言31 引言31.1 课题来源31.2 课题研究的研究背景31.3 国内外的发展现状、发展趋势及存在的主要问题51.4 课题研究的指导思想与技术路线错误!未定义书签。1.5 基于 FPGA 串口设计的技术要求错误!未定义书签。2 UART 原理介绍82.1 UART 结构和工作原理83 方案选择83.1 设计语言的选择93.2 电平转换方式的选择错误!未定义书签。3.3 FPGA 核心芯片的选择104 系统硬件设计114.1 器件芯片介绍114.2 系统硬件框图184.3 主要组成电路分析184.4 总电路图设计255 系统软件设计265.1 主程序流程图265.2 中断子程序流程图275.3 DDS 控制软件设计错误!未定义书签。5.4 AD7886 软件驱动设计错误!未定义书签。5.5 系统源程序286 制作位移测量装置的步骤287总结 .- 28 -参考文献 .- 28 -致 谢31附录 132附录 21附录 32前言基于 FPGA 的串口设计冉 峰:陈晓静,电子信息学院陈晓

2、静:电子信息学院摘要随着微电子技术的快速发展,电子设备逐渐向着小型化 .集成化方向的发展。人们在要求设备性能不断提升的同时,还要求设备功耗低体积小重量轻 可靠性高。UART 因其可靠性高,传输距离远线路简单而成为比较广泛的串行数据通信电路,而现在大部分集成电路通信用的 UART 芯片,存在成本高,电路复杂, 移植性较差等缺点。本设计是基于 FPGA 的嵌入式 UART 模块化设计方法,将 UART 模块集成到 FPGA 上,而这些模块功能全部基于 VHDL 硬件描述语言,并通过有限状态机来实现,增强了设计的灵活性,降低了成本。论文的主要目标是利用 FPGA 实现 UART 的功能与 PC 机实现串口通信,UART 的功能模块通过 MAX232 将电平转换后与 PC 机相连达到设计目的。 UART 的功能模块主要包括波特率产生模块,数据发送模块,数据接收模块三个部分,对各模块的功能在文中都有详细的介绍。整个设计都采用硬件描述语言(VHDL)实现,并且采用了分模块的设计风格,使设计的思路更清晰。关键字FPGAUARTVHDLPC 机MAX232第 1 页 (共 37 页)基于 FPGA 的

3、串口设计The Design Of Serial Base on FPGAFengRan: Chen Xiaojing, Electronic Information ChenXiaojing: Electronic InformationAbstract With the rapid development of microelectronics technology, electronicequipment become smaller and integratedin the continuous upgrading of equipment requlrements at the same time,also called low-power devices,small size,light weight, high reliabilityUART because of its high reliability, long transmission distance lines become broader and simple serial data communicatio

4、n circuit, but now most of the communication with the UART integrated circuit chip, high cost, circuit complexity, less portable, and other shortcomings. The design is based on modular FPGA design methodology for embedded UART, UART modules will be integrated into the FPGA, all based on these modules feature hardware description language VHDL and implemented through the finite state machine, and enhance design flexibility, reduced costs.第 2 页 (共 40 页)前言前言随着 FPGA/CPLD 器件在控制领域的广泛使用,开发嵌于 FPGA/CPLD

《基于FPGA的串口设计_毕业设计论文》由会员小鱼****猫分享,可在线阅读,更多相关《基于FPGA的串口设计_毕业设计论文》请在金锄头文库上搜索。

基于nRF2401模块的无线温度监测系统设计_毕业论文

庄浪县梯田农业生态-经济效益分析_毕业论文

基于JAVA的航空售票系统毕业论文 (1)

楼宇智能化本科毕业论文

六轴工具磨床转动平台设计毕业论文设计

基于bs模式的酒店住宿管理系统的设计与实现

基于MODBUS协议的通讯系统_毕业设计论文

基于FPGA的数字秒表的设计毕业论文

基于FPGA的串口设计_毕业设计论文

基于fpga技术的数字存储示波器设计

酒店就业大学生流失现象的透析及对策研究—毕业论文

建筑工程项目质量控制研究毕业论文

交通灯控制系统模拟设计_毕业设计论文

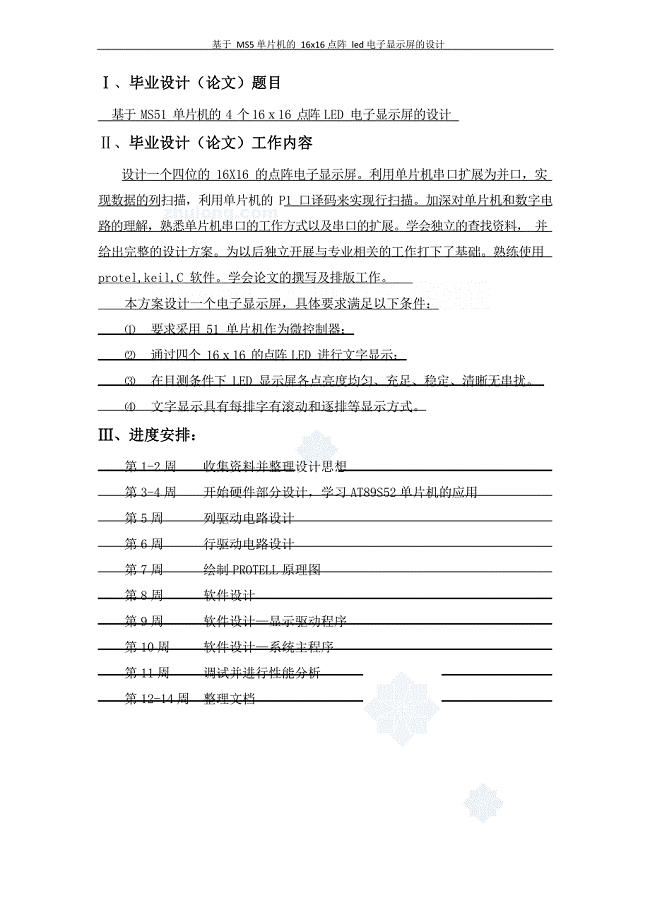

基于MS5单片机的16x16点阵led电子显示屏的设计本科毕业设计

基于MATLAB的电力系统故障分析与仿真_毕业论文设计

Android毕业设计论文

教学用小型数控钻铣床设计说明书论文

基于FX系列PLC的机械手传送带设计本科毕业设计

基于LabVIEW的科学计算器毕业设计

链驱动双层升降横移式立体车库设计毕业论文

大规模定制的生产管理模式研究.doc

大规模定制的生产管理模式研究.doc

2022-10-10 35页

深度分析及挖掘会员消费行为数据 实现精准会员营销及服务.doc

深度分析及挖掘会员消费行为数据 实现精准会员营销及服务.doc

2024-02-05 7页

毕业设计(论文)-专用钻床设计(全套图纸)

毕业设计(论文)-专用钻床设计(全套图纸)

2023-04-09 29页

cai的毕业设计手册.doc

cai的毕业设计手册.doc

2023-01-05 19页

浅谈企业文化建设如何适应市场经济的发展要求.doc

浅谈企业文化建设如何适应市场经济的发展要求.doc

2023-01-20 17页

试论无效合同转换制度.doc

试论无效合同转换制度.doc

2023-07-26 14页

基于STC89C52单片机的温度报警器

基于STC89C52单片机的温度报警器

2023-03-04 26页

云南大学药物分析2018试题库答案.doc

云南大学药物分析2018试题库答案.doc

2024-01-30 23页

毕业设计(论文)——基于无线传感器网络的精准农业环境监测系统设计.doc

毕业设计(论文)——基于无线传感器网络的精准农业环境监测系统设计.doc

2023-11-16 62页

毕业设计(论文)-摇臂轴支座加工工艺与专用机床夹具设计(全套图纸)

毕业设计(论文)-摇臂轴支座加工工艺与专用机床夹具设计(全套图纸)

2024-01-02 41页