离子注入课程设计

16页1、燕山大学课程设计说明书题目:利用SILVACO设计MOS器件及其性能模拟学院(系):理学院年级专业:08级电子信息科学与技术学 号:080108040028学生姓名:杨丹指导教师:郭得峰教师职称:讲师燕山大学课程设计(论文)任务书院(系):理学院基层教学单位:电子信息科学与技术学号080108040028学生姓名杨丹专业(班级)08级微电子设计题目设计技术参数利用SILVAC0设计mos器件及其性能模拟,离子扩散、离子注入过程模拟 要精确;光刻、氧化、淀积、离子注入、刻蚀、热退火、金属化等步骤要完整 精确。设计要求通过阅读相关资料,了解目前集成电路工艺及模拟软件现状;了解工艺模 拟软件并学习Silvaco软件;利用Silvaco软件进行MOS器件的设计及其性能 模拟;分析数据,获得工艺参数对MOS器件的影响规律。工作量1. 一周时间选定课题并查阅相关资料;2. 一周时间设计步骤;3. 一周时间完成程序的编写与调试;4. 一周时间整理数据,完成分析及报告书。工作计划1. 选定课程工艺设计题目并查阅相关资料;2. 设计实验步骤;3. 编写与调试程序;4. 整理资料完成实验报告。参考资料指导

2、教师签字基层教学单位主任签字说明:此表一式四份,学生、指导教师、基层教学单位、系部各一份。年 月 日共15页第2页利用SILVACO设计MOS器件及其性能模拟Using SILVACO to design MOS device and its performance Simulation摘要:离子注入首先是作为一种半导体材料的掺杂技术发展起来的,它所 取得的成功是其优越性的最好例证。低温掺杂、精确的剂量控制、掩蔽容 易、均匀性好这些优点,使得经离子注入掺杂所制成的几十种半导体器件 和集成电路具有速度快、功耗低、稳定性好、成品率高等特点。对于大规 模、超大规模集成电路来说,离子注入更是一种理想的掺杂工艺。如前所 述,离子注入层是极薄的,同时,离子束的直进性保证注入的离子几乎是 垂直地向内掺杂,横向扩散极其微小,这样就有可能使电路的线条更加纤 细,线条间距进一步缩短,从而大大提高集成度。此外,离子注入技术的高精度和高均匀性,可以大幅度提高集成电路的成品率。随着工艺上和理 论上的日益完善,离子注入已经成为半导体器件和集成电路生产的关键工 艺之一。在制造半导体器件和集成电路的生产线上,已经广泛

3、地配备了离 子注入机。Abstract:Ion implantation is used as a semiconductor material is doped technology developed, its success is its superiority to the best example. Low temperature dopant, accurate dose control, masking easily, good uniformity of these advantages, made by ion implantation doping made dozens of semiconductor devices and integrated circuits with high speed, low power consumption, good stability, high yield. For large, very large scale integrated circuit, ion implantation is an ideal doping

4、 process. As mentioned before, the ion implanted layer is very thin, at the same time, the ion beam straight into the guarantee of ion implantation is almost perpendicular to the lateral diffusion of doped inward, extremely small, so that it is possible to make the circuit lines more slender, line spacing further reduced, thereby greatly improving the degree of integration. In addition, ion implantation technology of high precision and high uniformity, can greatly improve the yield of integrated

《离子注入课程设计》由会员博****1分享,可在线阅读,更多相关《离子注入课程设计》请在金锄头文库上搜索。

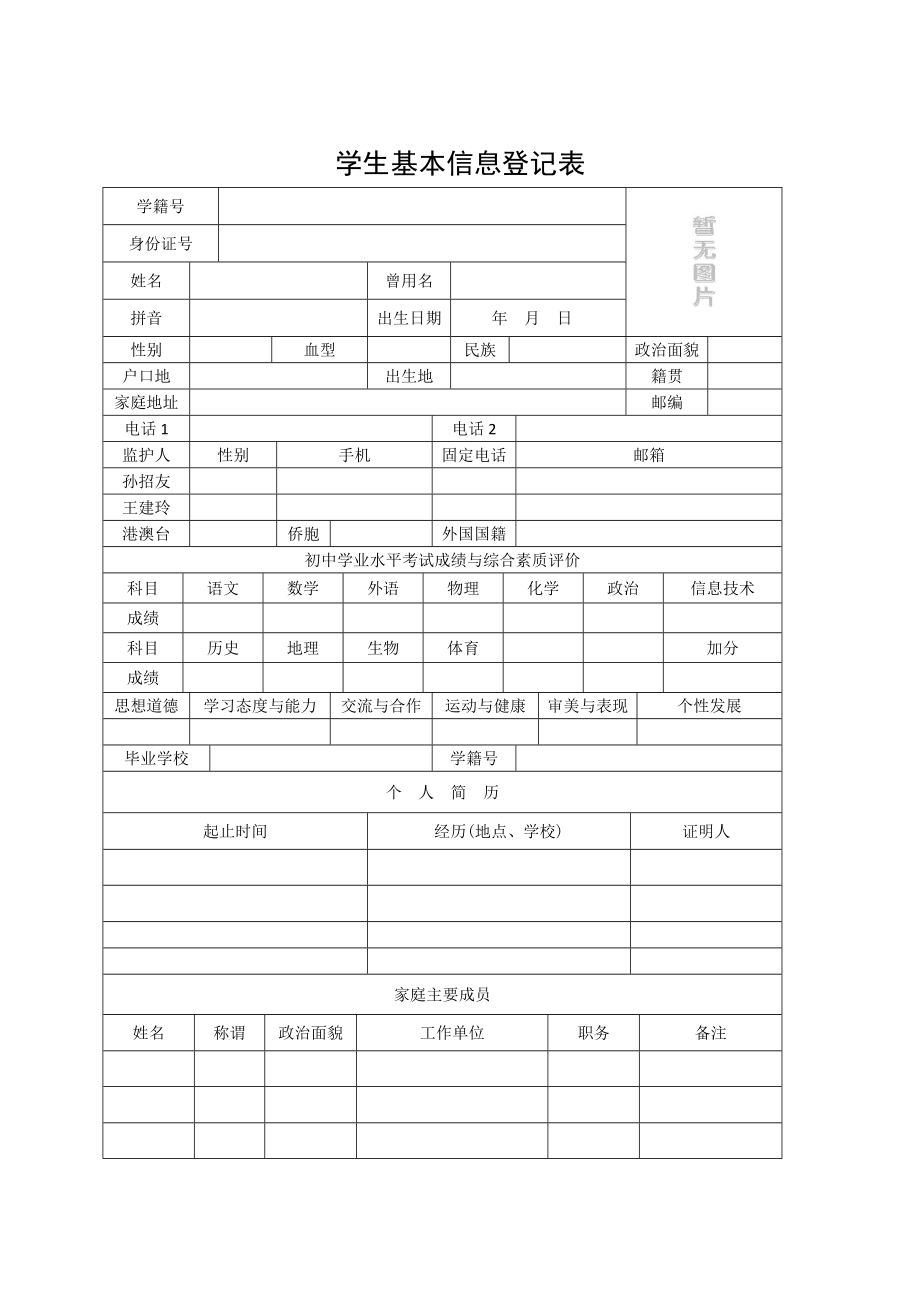

云南省普通高中学生成长记录手册完整版

画不同的正方形并发现规律

最新【金版学案】地理人教版必修1练习:第二章第一节第1课时大气的受热过程、热力环流 Word版含解析

教育培训机构实习期工作总结

幼儿园小班年终工作总结模板(2篇).doc

洗胃过程中洗胃机出现故障时的应急预案及程序

提高初中英语教学质量措施

读书报告格式及范文

2023维修工年度工作总结标准样本(二篇).doc

男女平等是可能实现的四辩(原创,内部宝贵资料)

药品进销存管理系统数据库课程设计报告

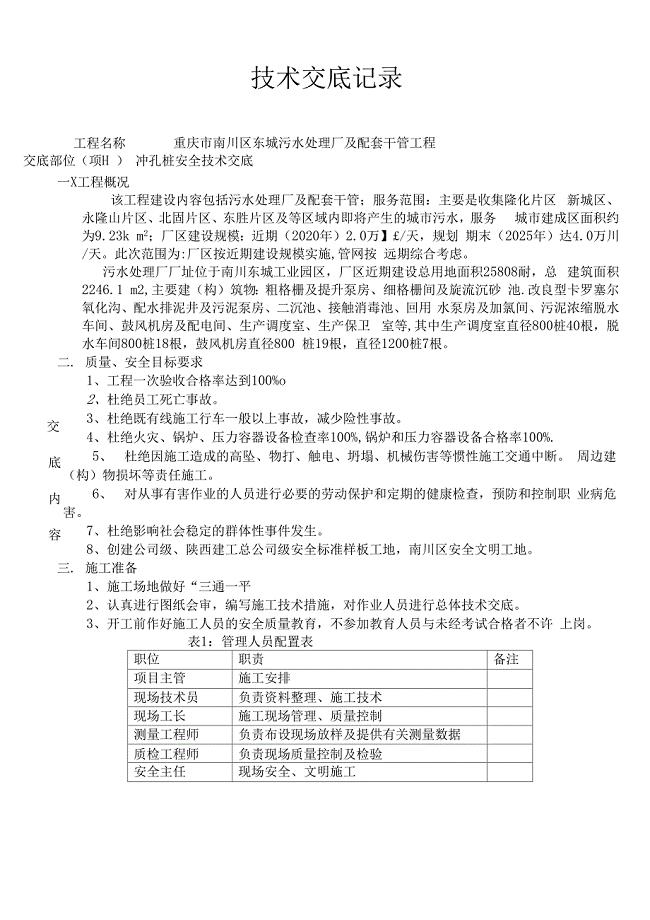

冲孔桩技术交底汇总

岗位职责及管理

关于我国民营经济的调查报告

二年级下期末试卷二下期末试卷

运动平板试验知情同意书

热处理厂房辅楼暖通空调安装工程项目计划

东莞光伏设备设计项目实施方案(模板范本)

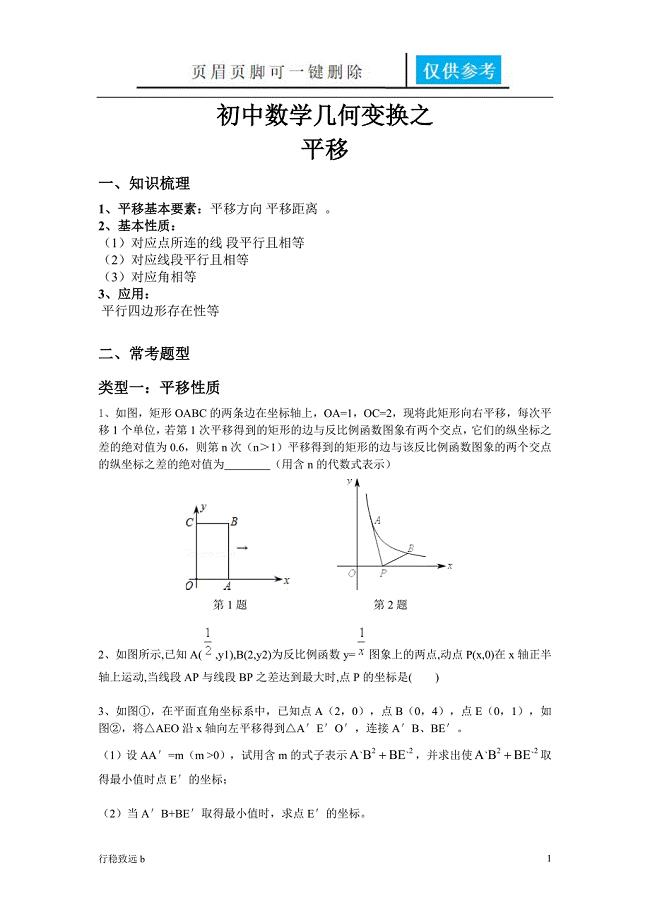

初中几何变换平移行稳书屋

单价合同范文集锦8篇

石墨制压力容器的浸渍、粘结培训教材

石墨制压力容器的浸渍、粘结培训教材

2022-09-21 17页

房屋零星维修改造工程投标文件样本

房屋零星维修改造工程投标文件样本

2023-03-26 16页

纯毛织物防毡缩整理

纯毛织物防毡缩整理

2024-01-01 8页

国际工程承包合同(样本)

国际工程承包合同(样本)

2024-02-20 33页

2021年消防工程监理实施细则

2021年消防工程监理实施细则

2022-07-18 12页

60、全价值链财务信息体系化探索与实践

60、全价值链财务信息体系化探索与实践

2023-10-06 11页

2015顾嘉辉广州演唱会

2015顾嘉辉广州演唱会

2024-01-31 9页

动植物检验检疫

动植物检验检疫

2024-01-20 11页

第五章 矿井瓦斯防治

第五章 矿井瓦斯防治

2023-09-07 29页

IPTV系统中几种编码格式的分析和比较

IPTV系统中几种编码格式的分析和比较

2023-01-19 5页