基于.FPGA的数字信号发生器设计说明书

17页1、基于FPGA的数字信号发生器设计作者:杨家兴XX理工学院物电学院电子通信1104班.XXXX 723000指导教师:薛转花摘要数字信号发生器是数字信号处理中不可缺少的调试设备.在生产生活中的应用非常广泛。本文所设计的内容就是基于Altera公司的现场可编程门阵列FPGA实现数字信号发生器的设计,本设计中应用VHDL硬件描述语言进行描述.使该数字信号发生器可以产生正弦波、方波、三角波、锯齿波四个独立的波形。关键词:数字波形发生器;FPGA;VHDLDesign OfFPGA-based Digital Signal GeneratorAuthor:Yang JiaxingTutor: Xue Zhuanhua AbstractDigital signal transmitter as a test facility is an important part of information processing system. In the production of a wide range of application of life. This content is designed

2、by Altera, based on field programmable gate array design of digital signal generator, the design of the application of VHDL hardware description language to describe, so that the digital signal generator can produce sine, square, triangle, sawtooth waveforms of four independent.Key words:Digital Waveform Generator; FPGA;VHDL目 录第一章绪论31.1 背景与意义31.2 国内外发展现状3第二章相关资料42.1 FPGA简介42.3 VHDL简介52.4 Quartus简介6第三章系统软件设计73.1软件系统流程图73.2 数字信号发生器的软件设计83.2.1 主控制模块83.2.2 波形数据产生模块9结束语12致谢12参考文献12附录13 / 1.绪论1.1 背景与意

3、义在电子技术领域.常常需要波形、频率、幅度都可调的电信号.用于产生这种电信号的电子仪器称作信号发生器。信号发生器是一种常用的信号源.广泛运用于科学研究、生产实践和教学试验等领域。特别是在通信系统的科研实验中.常常需要用到不同频率和幅度的信号.如正弦波、三角波、方波和锯齿波等。作为一种为电子测量和计量提供电信号的设备.它和万用表、示波器、频率计等仪器一样.是最普通、最基本.也是运用最广泛的电子仪器之一.几乎所有电参量的测量都需要用到信号发生器。传统的波形发生器多采用模拟分立元件实现.产生的波形种类要受到电路硬件的限制.体积大、灵活性和稳定性也相对较差。近年来.以数字技术为基础的数字信号发生器得到了飞速的发展.性能指标都达到了一个新的水平。现场可编程门阵列器件具有容量大、运算速度快、现场可编程等优点.使得许多复杂的电路有了新的实现途径.越来越被广泛地应用到实际系统中。而且随着当今电子系统的越来越复杂.毫无疑问.数字信号发生器正在成为模拟复杂信号的事实标准。凡是能产生测试信号的仪器.统称为信号源.也称为信号发生器.它用于产生被测电路所需特定参数的电测试信号。信号源是根据用户对其波形的命令来产

4、生信号的电子仪器。信号源主要给被测电路提供所需要的已知信号各种波形.然后用其它仪表进行测量的参数。信号源有很多种分类方法.其中一种方法可分为混和信号源和逻辑信号源两种。其中混和信号源主要输出模拟波形;逻辑信号源输出数字码形。混和信号源又可分为函数信号发生器和任意波形/函数发生器.其中函数信号发生器输出标准波形.如正弦波、方波等.任意波/函数发生器输出用户自定义的任意波形;逻辑信号发生器又可分为脉冲信号发生器和码型发生器.其中脉冲信号发生器驱动较小个数的的方波或脉冲波输出.码型发生器生成许多通道的数字码型。1.2 国内外发展现状采用可变时钟和计数器寻址波形存储器的任意波形发生器4在一段时期内曾得到广泛的应用.其取样时钟频率较高且可调节.然而这种波形发生器对硬件要求比较高.需要高性能的锁相环和截止频率可调的低通滤波器.且频率分辨率低.频率切换速度较慢.已经逐步退出市场。目前市场上的数字信号发生器主要采用直接数字合成Direct Digital Synthesuzer.DDS技术.这种波形发生器不仅可以产生可变频的载频信号、各种调制信号.同时还能和计算机配合产生用户自定义的有限带宽的任意信号

《基于.FPGA的数字信号发生器设计说明书》由会员M****1分享,可在线阅读,更多相关《基于.FPGA的数字信号发生器设计说明书》请在金锄头文库上搜索。

锦州温控技术应用项目投资计划书范文

人事专员年度工作总结(3篇).doc

2019年初考试小结(四篇)

让陆离的光影为思品课教学添彩

中小型组织质量手册

中班美术添画教案详案反思《圆形变变变》

2022暖心重阳节祝福语汇总

保险公司民主评议日常工作考核材料

龙门吊安装及拆卸方案.总结

![项目管理目标责任书[最终版]](https://union.152files.goldhoe.com/2022-8/2/26ec9ef9-3ae4-4b99-97db-c7758a829fc2/pic1.jpg)

项目管理目标责任书[最终版]

地区产业结构变动导向

物业管理人员述职报告

双方自愿离婚协议格式范文(十篇).doc

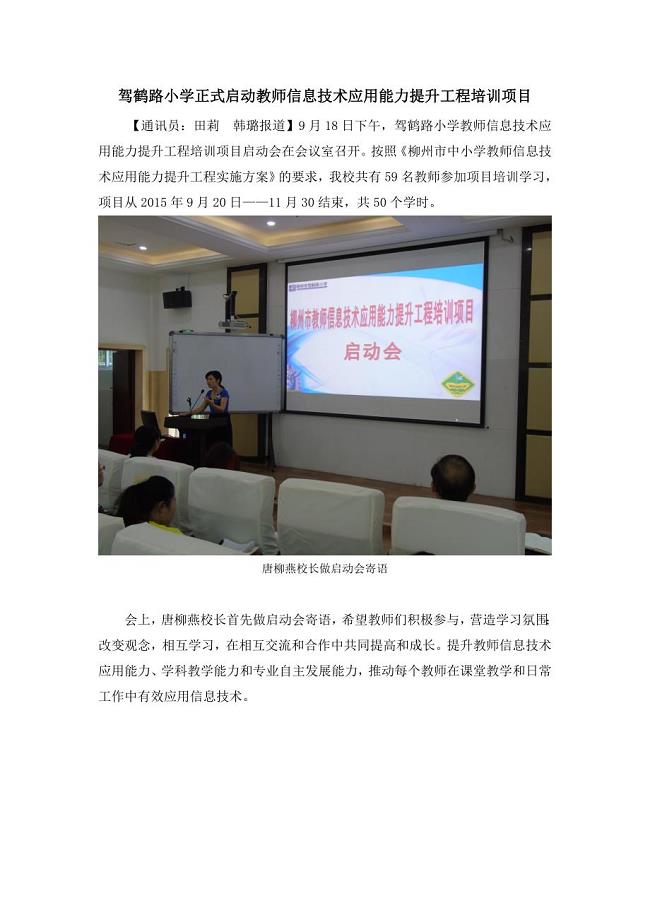

驾鹤路小学正式启动教师信息技术应用能力提升工程培训项目

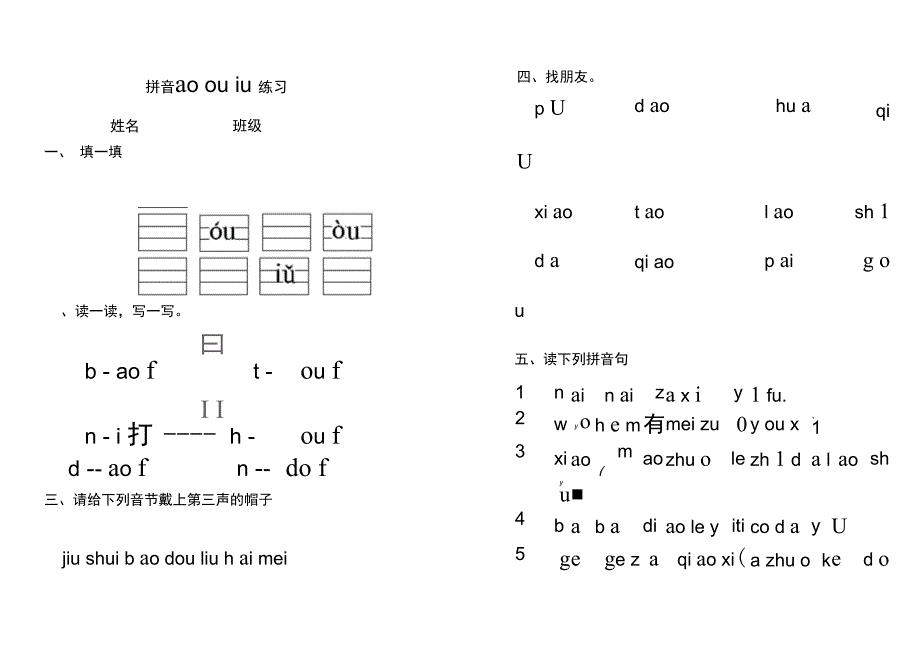

拼音aoouiu练习试题

profibus-DP通信样例安川电机

房地产开发企业会计教案文本

委托转供电协议范文

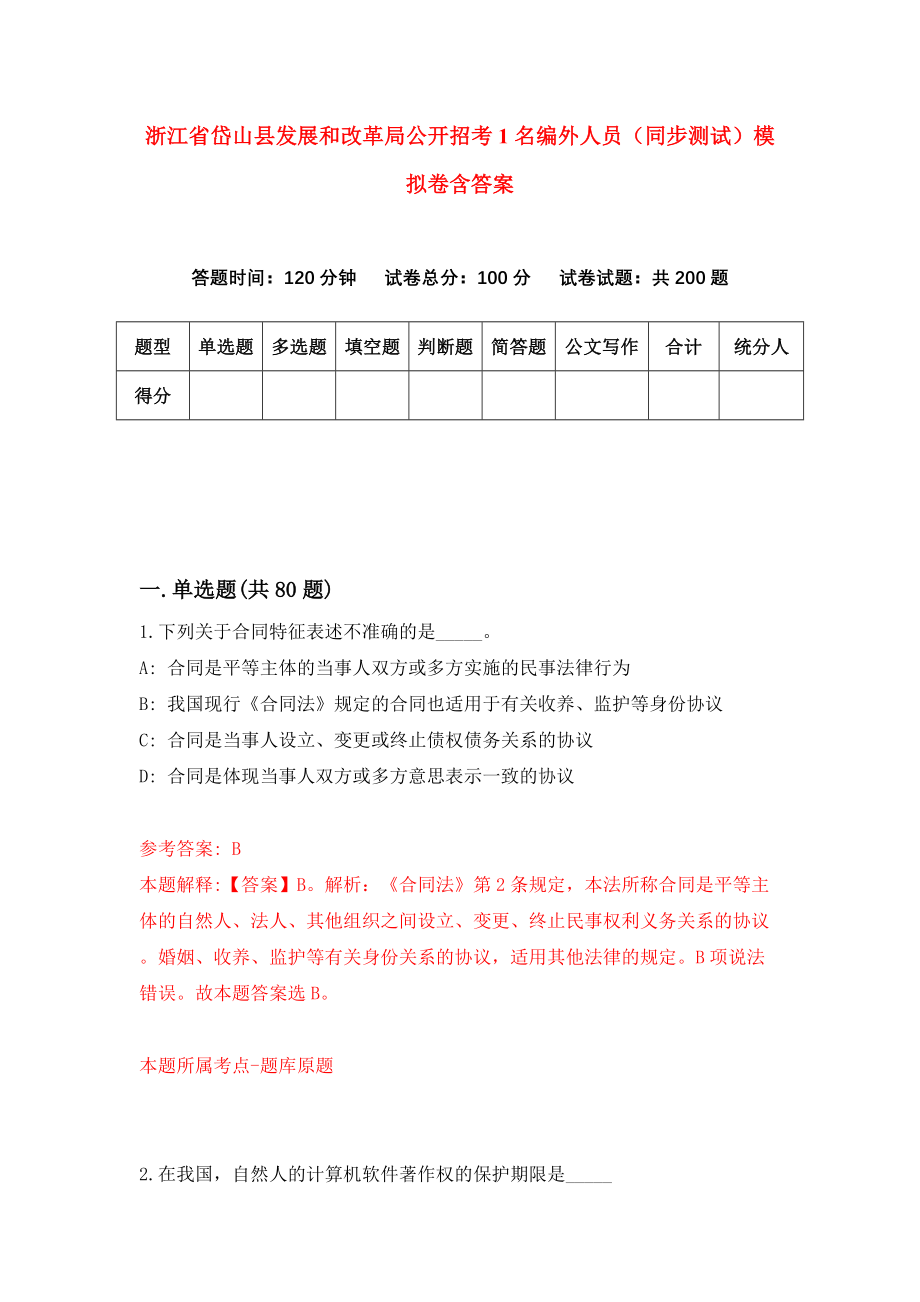

浙江省岱山县发展和改革局公开招考1名编外人员(同步测试)模拟卷含答案【7】

小学生语文阅读能力测评

XXX路DN1000上水钢管施工方案(DOC 15页)

XXX路DN1000上水钢管施工方案(DOC 15页)

2023-04-21 25页

第四节八年级物理平均速度的测量练习题

第四节八年级物理平均速度的测量练习题

2023-08-18 3页

公司企业合同 外销商品房预售契约补充协议

公司企业合同 外销商品房预售契约补充协议

2022-12-16 9页

764837243互联网行业薪酬现状分析

764837243互联网行业薪酬现状分析

2023-12-27 3页

212指数函数及其性质

212指数函数及其性质

2023-06-03 7页

部编人教版一年级语文上册期末综合复习强化练习

部编人教版一年级语文上册期末综合复习强化练习

2022-10-18 11页

世界上最神奇堂课—我能成就一切

世界上最神奇堂课—我能成就一切

2022-11-27 9页

精品高中化学选修四鲁科版练习:第1章第1节第1课时反应热焓变 Word版含解析

精品高中化学选修四鲁科版练习:第1章第1节第1课时反应热焓变 Word版含解析

2023-12-10 9页

2012年江苏苏州中考数学及答案(word版)

2012年江苏苏州中考数学及答案(word版)

2023-06-28 12页

制作原版系统U盘启动并隐藏启动分区

制作原版系统U盘启动并隐藏启动分区

2022-07-29 1页