VHDL数字秒表格设计说明书

25页1、word通达学院2017/2018学年 第一学期课程设计 实验报告模 块 名 称 VHDL课程设计 专 业 学 生 班 级 学 生 学 号 学 生 姓 名 指 导 教 师 设计题目数字秒表设计任务要求(1)计时精度10ms,计时围04分59.99秒;(2)设置启动、停止和复位键控制秒表的工作(3)用数码管实时显示计时结果。设备及软件Quaster 目 录一、课程设计目的与要求11.1 课程设计目的11.2 基本要求1二、设计方案-数字秒表的设计12.1 设计功能12.2 秒表基本原理及设计方法22.3 数字秒表设计原理2三、开发环境3四、模块结构44.1 数字秒表RTL级电路4 计时器模块54.3 取数模块74.4 编码模块84.5 数码管显示控制模块124.6 数码管地址选择模块13五、 设计仿真和实验155.1 计时器模块仿真155.2 秒表仿真155.3 pin引脚接口图165.4 实验结果图17六、总结与体会196.1 错误分析196.2 心得体会19七、参考文献20 / 一、课程设计目的与要求1.1 课程设计目的EDA 技术综合设计与实践(注:EDA 即电子设计自动化,Ele

2、ctronics Design Automation)是继模拟电子技术基础、数字电子技术基础、电子技术基础实验、EDA等课程后,电子类等专业学生在电子技术实验技能方面综合性质的实验训练课程,是电子技术基础的一个部分,其目的和任务是通过一周的时间,让学生掌握 EDA 的基本方法,熟悉一种 EDA 软件(Quartus II),并能利用 EDA 软件设计一个电子技术综合问题,并在实验板上成功下载,为以后进行工程实际问题的研究打下设计基础。1.2 基本要求(1)通过课程设计使学生能熟练掌握一种 EDA 软件(Quartus II)的使用方法,能熟练进行设计输入、编译、管脚分配、下载等过程。(2)通过课程设计使学生能利用 EDA 软件(Quartus II)进行至少一个电子技术综合问题的设计(容可由老师指定或自由选择),设计输入采用 VerilogHDL 硬件描述语言输入法。(3)通过课程设计使学生初步具有分析、寻找和排除电子电路中常见故障的能力。(4)通过课程设计使学生能独立写出严谨的、有理论根据的、实事的、文理通顺的课程设计报告。二、设计方案-数字秒表的设计2.1 设计功能(1)计时功能:

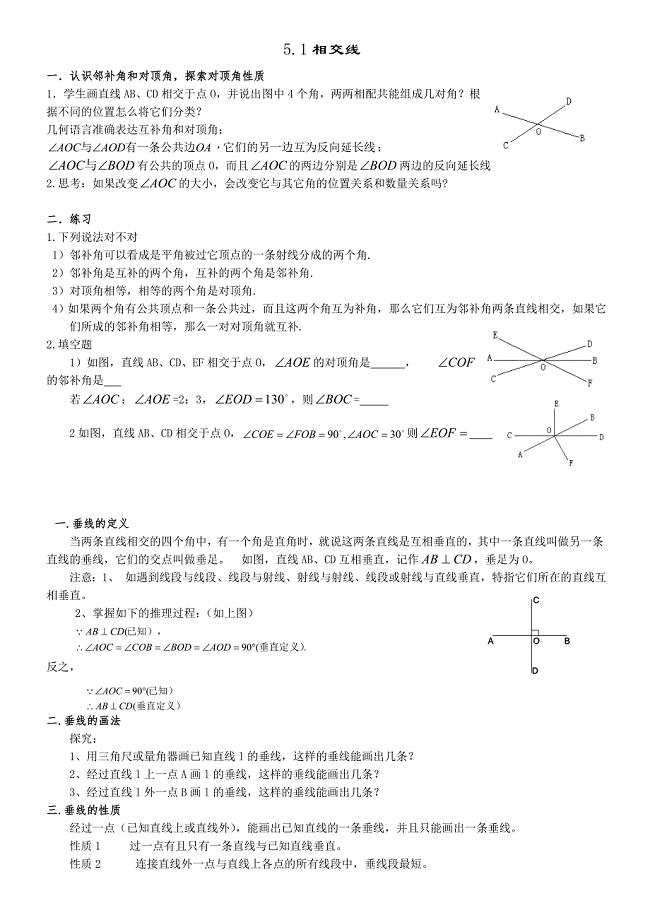

3、设计一个秒表,该秒表计时围为 0-59 分 59 秒 990 毫秒,分辨率为 10 毫秒(秒)。(2)显示功能:分、秒、毫秒各用 2 位数码管(共 6 位数码管)显示。(3)清零,启动计时,暂停及继续计时功能:2.2 秒表基本原理及设计方法(1)秒表的基本结构:该秒表有 3 个输入端,分别为时钟输入(输入时钟为 1 毫秒)、复位输入和启动/暂停。(2)复位信号高电平有效,可以对整个系统异步清 0;当启动/暂停为低电平时秒表开始计时,为高电平时暂停,变低后在原来的数值基础上再计数。(3)百分秒、秒和分钟信号用七段 LED 显示。(4)“毫秒计数器”采用 100 进制计数器,每累计 1000 毫秒(1 秒)产生一个“秒脉冲”信号,该信号将作为“秒计数器”的时钟脉冲。“秒计数器”采用 60 进制计数器,每累计 60 秒,发出一个“分脉冲”信号,该信号将被送到“分计数器”。“分计数器”采用 60 进制计时器,可实现对 60 分钟的累计。2.3 数字秒表设计原理数字秒表采用模块化设计:(1)输入信号:基准时钟 clk(20MHz),清零端 clr(高电平有效),启动/暂停信号 en_count(

4、低电平时启动,高电平时暂停)(2)计时器:以 10ms 为计时分辨率,每 10ms 产生一个“10 毫秒脉冲”信号,每 990ms 产生一个“秒脉冲”信号,每 60 秒产生一个“分脉冲”信号;(3)取数模块:对计时器输出的分、秒、十毫秒信号进行逐位取数,变成将在数码管上显示的十进制数;(4)编码模块:将分、秒、十毫秒的十进制数转换成数码管显示的编码;(5)数码管显示控制模块:每隔 3ms 使能更新不同数码管的数据,6 位数码管更新一次共用时 18ms,刷新频率大于 50HZ,利用人的视觉暂留,好像 6 位 LED 是同时点亮的,并不察觉有闪烁现象;(6)数码管地址选择模块:每隔 3ms 使能点亮不同的数码管,6 位数码管一共用时 18ms。三、开发环境开发环境:1、PC 机一台2、Windows XP 32 位操作系统3、Altera 公司的 Quartus II 9.0 软件4、基于 Cyclone II 型 EP2C8Q208C8 的开发板四、模块结构4.1 数字秒表RTL级电路module counter_top(clk,en_count,clr,row_scan_sig,col

《VHDL数字秒表格设计说明书》由会员re****.1分享,可在线阅读,更多相关《VHDL数字秒表格设计说明书》请在金锄头文库上搜索。

物业水电维修工作计划参考范文(四篇).doc

论以宿舍为基点开展大学生心理健康教育的重要性

2014年菲律宾最高融资初创企业

镇江骨科植入物项目可行性研究报告(模板范文)

酒店预防传染病应急预案1

人类与地理环境的协调发展全章教案

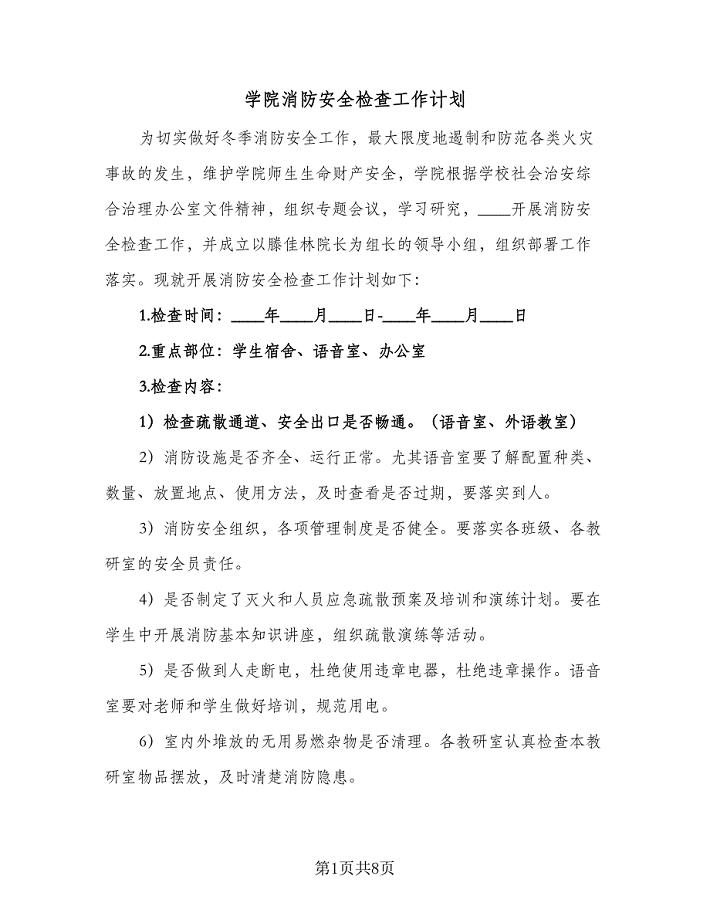

学院消防安全检查工作计划(2篇).doc

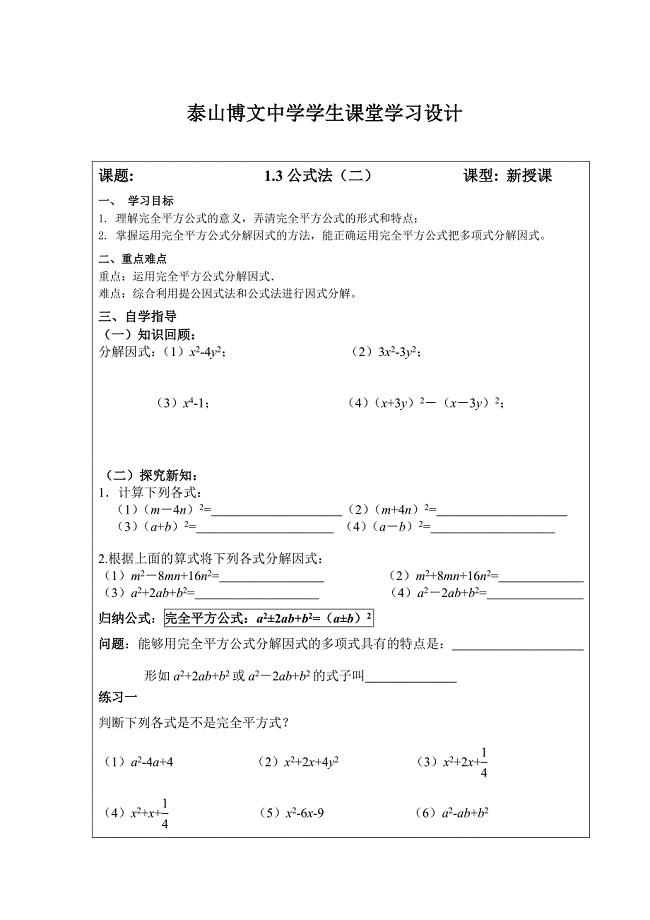

鲁教版数学八上1.3公式法学案2

(转)走进新课标

2023年餐厅员工述职报告

2023年毕业晚会节主持稿(2篇)

口腔科医生个人工作总结范文

建设局建设新农村经验材料 (6)

班主任开学典礼发言稿

初一下数学第一章总结

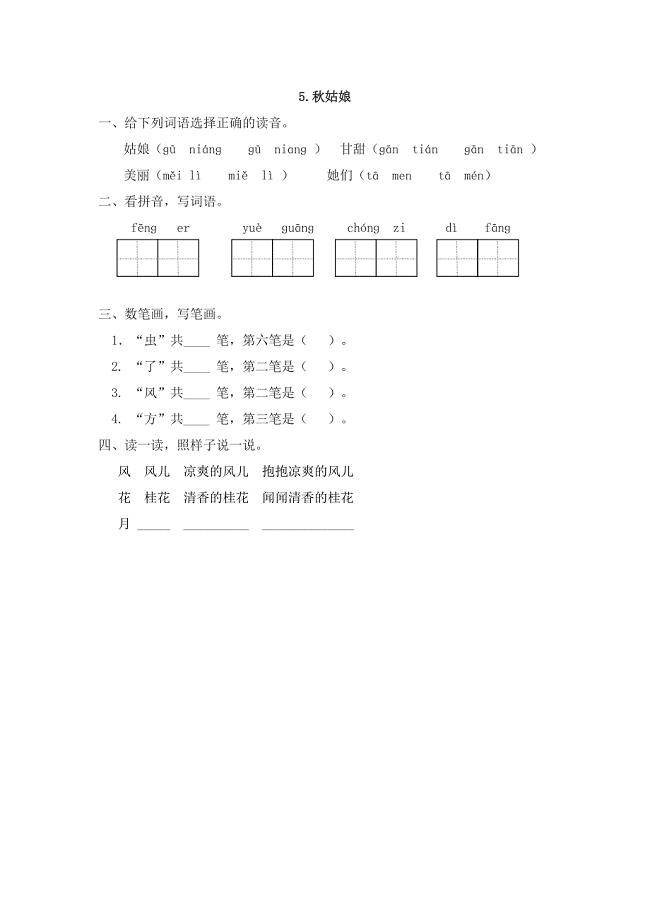

5秋姑娘课时练习题及答案

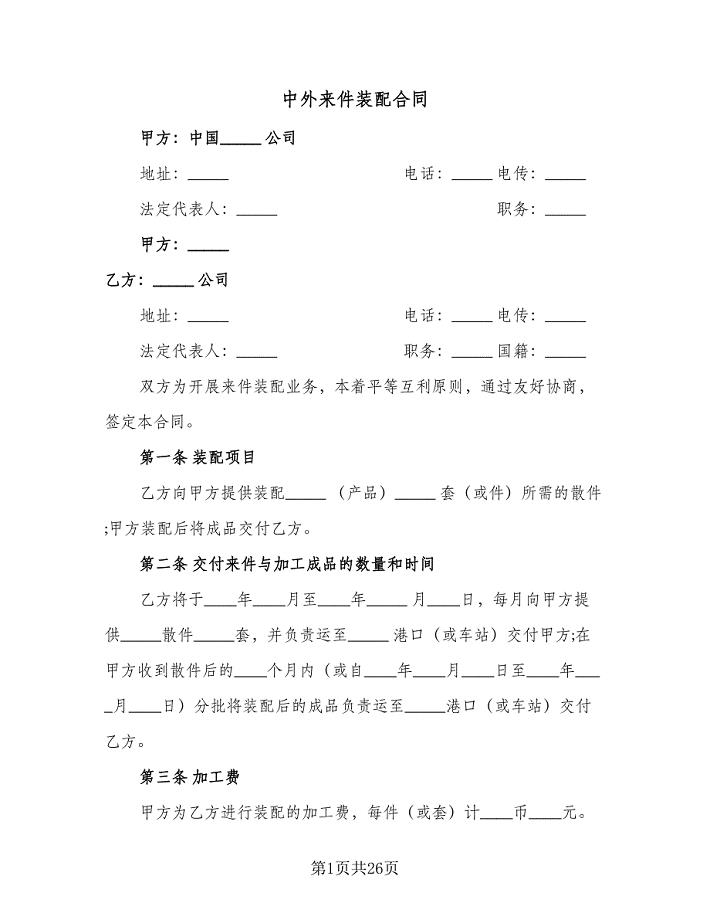

中外来件装配合同(7篇).doc

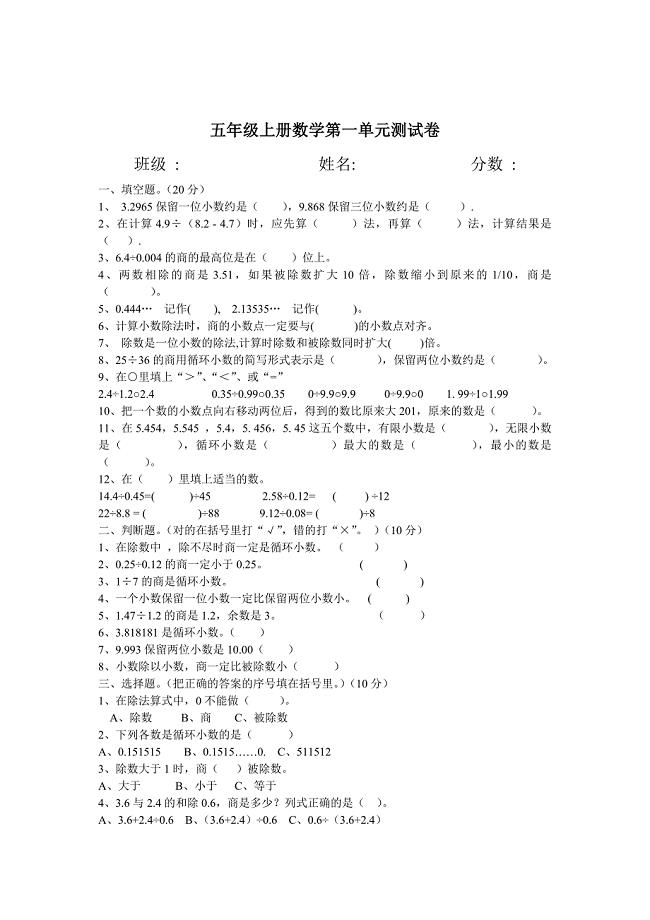

精校版【北师大版】五年级上册数学单元测试卷全套18页Word版

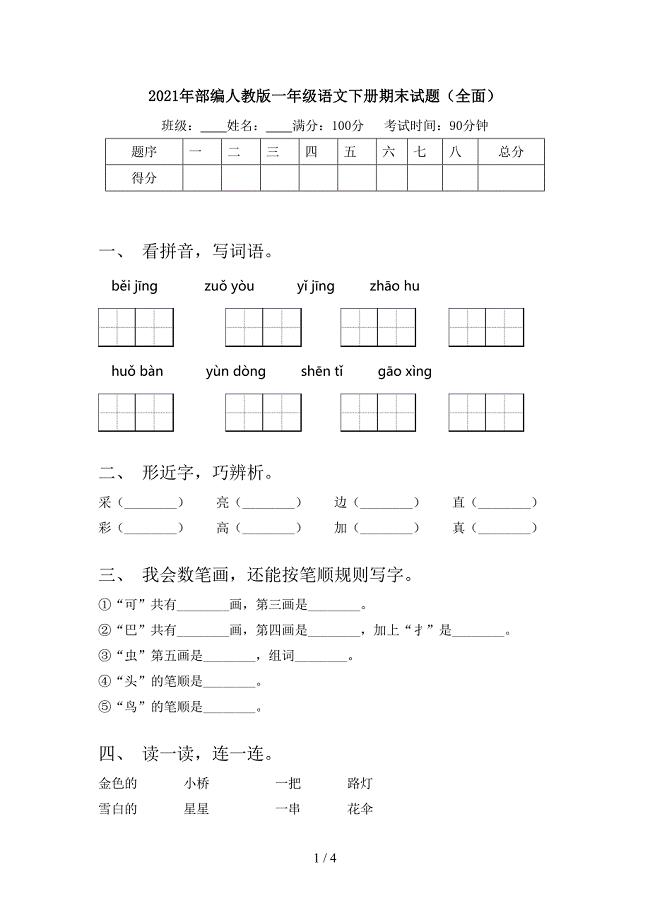

部编人教版一年级语文下册期末试题全面

板蓝根颗粒提取生产工艺规程

广东省深圳市普通高中毕业班高考数学一轮复习模拟试题: 07 Word版含答案

广东省深圳市普通高中毕业班高考数学一轮复习模拟试题: 07 Word版含答案

2023-03-21 11页

新编北师大版数学选修12教案:第1章独立性检验的基本思想及初步应用

新编北师大版数学选修12教案:第1章独立性检验的基本思想及初步应用

2024-03-04 4页

城市的良心记叙文阅读原文附答案

城市的良心记叙文阅读原文附答案

2023-08-16 6页

新版人教版小学英语各年级知识点总结材料

新版人教版小学英语各年级知识点总结材料

2022-12-14 60页

雨刮器性能耐久试验台

雨刮器性能耐久试验台

2022-09-21 13页

2023年计算机职称考试模块窗口操作与应用程序复习资料

2023年计算机职称考试模块窗口操作与应用程序复习资料

2023-04-02 7页

长市八极拳的传承现状与发展对策研究1

长市八极拳的传承现状与发展对策研究1

2023-01-16 12页

海南省洋浦中学八年级生物上学期期末考试试题新人教版

海南省洋浦中学八年级生物上学期期末考试试题新人教版

2023-01-13 5页

美露防静电地板MERO)的安装规范

美露防静电地板MERO)的安装规范

2022-12-02 4页

一题多解对培养学生思维能力的影响

一题多解对培养学生思维能力的影响

2023-12-16 7页