一种ARM+DSP协作架构的FPGA验证实现

6页1、摘 要:介绍了以 ARM+dsp 体系结构为基础的 FPGA 实现。在其上验证应用算法,实 现了由 ARM 负责对整个程序的控制,由 dsp 负责对整个程序的计算,最大程度地同 时发挥了 ARM 和 dsp 的各自优势。关键词:ARM dsp FPGAARM 通用 CPU 及其开发平台,是近年来较为流行的开发平台之一,而由 ARM+dsp 的双核体系结构,更有其独特的功能特点:由 ARM 完成整个体系的控制和流程操作, 由 dsp 完成具体的算法和计算处理。这样,不但可以充分地发挥 ARM 方便的控制优 势,同时又能最大限度地发挥 dsp 的计算功能。这在业界已逐渐成为一种趋势。本文的 FPGA 的 Demo 验证,是在基于一款 dsp 内核处理器的研发基础上,对其 功能进行验证的一个小目标识别算法的实现。考虑到软件环境仿真的速度以及仿真 模型的局限性,用 FPGA 进行硬件协同验证。这样,既能够保证仿真的真实性,又能 够快速发现实际问题,减少不必要的流片次数,加快开发的进程,这对于一个大规 模的 SoC 设计,已经成为不可或缺的手段之一,而且对节约成本也有很大好处。 1 系统体系结构

2、双核系统的体系结构如图 1 所示。1.1 内嵌 ARM 内核的 EPXA1 芯片及其特点图 1 中,包含 ARM922T 内核的开发平台选用的是 Altera 公司的 excalibar 系列, 本验证实现选用的型号是EPXA1。EPXA1是一款带有100万门可重配置PLD的ARM Core+PLD 体系结构,可以通过 quartus II 软件工具来灵活配置 ARM Core 同外部的 端口连接,最大时钟频率能够达到 200MHz。 EPXA1 的高度集成化,不仅大大加快了 ARM 与片内各种资源的通讯速度,而且减小了硬件电路的复杂性、体积和功耗,真 正实现了 SOPC1。1.2 FPGA 硬件平台及其特点对于一个具体项目,FPGA芯片的选取要根据实际需求和特点来具体考虑。一般 应从逻辑资源需求、易扩展能力、信号质量以及成本等因素来考虑。如图 1 所示, 本次设计采用的两片FPGA分别为Xilinx公司的FPGA X3S5000和X2V6000,其容量 分别为 500 万门和 600 万门。选用这两块芯片正是基于逻辑资源需求的考虑。 FPGA X2V6000 面向高端应用,存储资源更

3、多,功能更强大,适用于性能要求较高的 dsp 内核,但其成本相对也较高;而FPGAX3S5000成本较低,适用于一般性能要求的模 块。两片FPGA都具备三个扩展槽,可做接口扩展,同时也能作为调试测试点用。1.3 双核体系结构设计特点具体来讲,整个体系结构是指通过人为设计电路图,外部选用不同的FPGA器件 来下载生成特定功能的外部硬件电路,在电路图上对应相应的端口标号;同时, ARM Core可以通过quartus II工具方便地连接不同的端口标号,编译运行生成相应的 配置文件;ARM的启动代码中用以上的的配置文件信息来配置PLD,从而实现ARM 同外部硬件电路即两片FPGA的连接3。FPGA X3S5000中下载固化AHBC硬件电路 以及外部SRAM Memory,而FPGA X2V6000中下载固化dsp Core以及支持AMBA协议 的 Wrapper。这种体系结构能够充分利用硬件资源,合理的版图位置方便了 ARM和dsp对外部 SRAM的访问,同时可快捷地实现ARM的控制功能,而且预留的扩展槽能够较为方便 地进行功能扩展和调试。dsp Core的Wrapper能够快速响应ARM的

4、控制请求,调动 dsp Core 进入不同的工作状态。2 系统工作流程及特点系统工作流程图如图2所示,介绍如下。2.1 ARM负责准备阶段ARM从Flash中运行启动代码,通过配置PLD来连接FPGA X3S5000中的AHBC, 目的在于ARM通过AHBC同FPGA X2V6000中的dsp Core进行交互。代码唤醒外部DMA通过以太网口从PC机端搬运第一帧待处理的图像数据,放到 双核公用的外部SRAM memory既定的地址段中。然后,ARM Core通过AHBC控制FPGA X2V6000 中的 dsp Core。这里需要说明两点:(1) FPGA 开发板的的图像传输是通过专门配置的带有 LXT972 芯片的以太网口 与 PC 机的以太网口进行交互, 如图 3 所示。图 3 左边的以太网子板即图 1 中的 Ethernet 模块。(2) dsp Core顶层的wrapper是支持AMBA协议的TOP Module,其中包括一个 Debug Sub-Moduleo ARM就是通过读写Debug Sub-Module的控制寄存器来控制dsp Core 的启动、停止等工作状态的。所以

《一种ARM+DSP协作架构的FPGA验证实现》由会员枫**分享,可在线阅读,更多相关《一种ARM+DSP协作架构的FPGA验证实现》请在金锄头文库上搜索。

地基加固施工方案(完整资料)

新版委托加工协议书

诈骗的二审辩护词怎么写

“父与女 张秀亚”阅读训练及答案

农产品买卖协议参考模板(二篇).doc

2021小学副校长述职报告范文

教师继续教育工作计划标准范文(四篇).doc

毕业论文基本稿终极版

大学生网络安全意识调查报告

【施工方案】人行道砖施工方案

创业大赛创业计划书

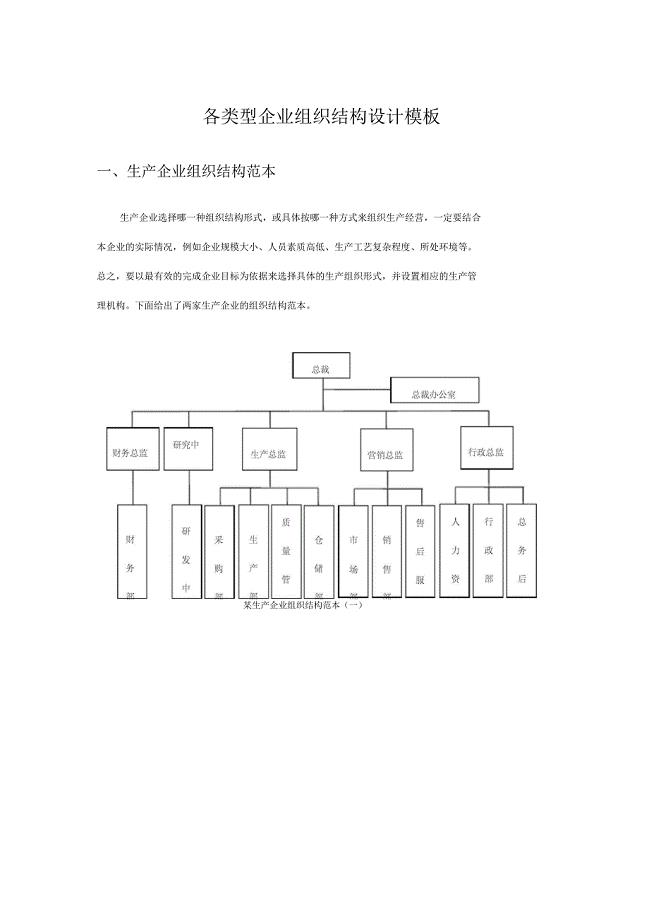

企业组织结构图模板

单位借款协议书5篇

2023年教师信访工作条例心得体会5篇

特易贷CEO周建:助 力 小微 企业 成长不能仅是“凑热闹”

如何让民间游戏成为幼儿园新的生长点

模板、脚手架工程

202_年证券公司个人试用期工作总结范文

基于单片机的直流电机调速系统设计论文

浙江省杭州市高三数学下学期模拟试题理12无答案

12、天气预报基本技能

12、天气预报基本技能

2023-07-03 12页

高产黄精种植技术

高产黄精种植技术

2023-02-02 4页

烟花爆竹应急救援预案

烟花爆竹应急救援预案

2023-08-26 6页

MATLAB等高线命令

MATLAB等高线命令

2023-09-11 6页

激光切割质量控制

激光切割质量控制

2023-03-05 22页

高速公路公司安全生产隐患排查治理专项行动阶段工作总结

高速公路公司安全生产隐患排查治理专项行动阶段工作总结

2022-12-10 32页

2020云计算基础知识测试题及答案

2020云计算基础知识测试题及答案

2022-12-11 72页

电气安全知识培训题库及答案

电气安全知识培训题库及答案

2023-06-06 7页

炼钢生产技术从入门到精通

炼钢生产技术从入门到精通

2023-10-13 20页

1 价格变化的原因及稳定物价的措施和原因

1 价格变化的原因及稳定物价的措施和原因

2022-12-20 11页