电磁兼容的设计方法介绍

16页1、电磁兼容的设计方法介绍(35)七阻抗的大小 在前次的共模和异模讨论中有提到共模Vcm电压的产生是和共模电流及接地阻抗的大小有关也就是 VCM = ICM X RG一般来说Icm的电流往往不是我们所能控制但是RG却是可以透过接地和屏蔽的方式来降低因为能适当的降低RG则相对的VCM就会降低而噪声的辐射自然就跟着减小至于要使得ICM 降低通常要处理到时脉频率(Clock)以及IC组件上的电压这样往往会明显影响到产品的功能和稳定性除非不得已一般是不考虑如此的做法。 从阻抗的观点来看首先就是要讨论到电路板上的阻抗就是一般典型的layout走线每英寸(Inch)约有20nH的电感存在也就是2.45公分长的走线其线上所存在的电感将近有20nH。 线上的阻抗跟对策有很大的关系很多问题就在这个地方通常要注意的有两个问题第一个就是电感第二个就是频率。 从电感上来说当走线愈长则相对上的电感也就会愈高这就是一般在Layout时常常会提到的一个观念Clock的走线要尽量短不可走的太长不过实际的layout上也不一定是如此。 另外一个重点就是从频率的角度来看假设信号是跑1MHz时线上的阻抗为1 那幺当信号变成10

2、0MHz时则线上的阻抗便不会是1 可能变成100 而当信号变成1GHz时那这时的阻抗可能达到1000 。 这个1K 的阻抗会使得原先相对于1MHz的VCM增加了1000倍的电压强度也就是同样的电路layout但是跑不同的信号频率时整个噪声的能量是不同。 这也就是为什幺从一般的电路设计圈往往根本无法看出EMI的问题因为电路图上所考虑的都是Clock信号的处理并不是针对高频谐波的噪声所规划因此很难从产品设计的 电路图要找出EMI的问题如果信号是跑1MHz从电路图上可以逐步的确认其信号的流向以及特性但是相对于1000MHz的谐波噪声则根本完全无法从电路图中分析得来因为它的路径和方向并不是照着电路图的信号径流程来走。 另外一个最常被忽略的阻抗问题就是接触压力的问题很多金属产品在机壳接缝和密合的地方看起来虽然皆有导通事实上对高频的噪声来说可能还是没有完全导通也就是它所存在的阻抗很大。 很多人会习惯用电表去量两个接触是否有导通事实上电表的导通只是针对直流电去测量这和实际上跑的100MHz或是1GHz噪声是不同的接触压力的阻抗会随着两金属面之间压力的增加而降低一般来说用销螺丝上锁来固定两金属面接触的

3、方法这时的压力阻抗是最小。 而常常被用来做为加强接地及屏蔽效果的铜箔或铝箔在使用上也必须要注意正确的铜箔贴完后要用力的把它压平(铜箔压平时千万别直接用手去压容易割伤)因为铜箔的胶虽然是导电胶但是没有把铜箔压到很平对高频的阻抗会有很大的差别有时在噪声的抑制的效果甚至会差到10dB以上。 图十二即为一个图标的说明在两个金属面之间所存在的压力阻抗左图为两金属面并没有很强的密合压力这时虽然低频都有导通可是对高频的信号来说只有部分的导通而在右图因为两金属面间能有密合的压力存在所以高低频的导通效果都很好。 阻抗低除了相对所产生的共模电压降低外对于一些高频噪声导流到大的接地面上也是有很大的帮助在许多高噪声的组件上一般的处理除了隔离的方式外都是用疏导的方法如果隔离无法达到降低噪声的效果则可以使用疏导的方式让组件上的噪声能快速的流到大的接地面上这时如果彼此连接的阻抗很高则这些组件上的噪声就不容易快速的流到接地面。八典型电路应用的说明 在讨论了许多共模异模和阻抗的问题这里我们针对一个典型的电路来做一个说明。 事实上常常处理EMI修改的工程人员都了解一件事情就是实务上的对策方法和一般书本文章介绍的方法都有很

4、大的一段距离这是因为通常在研究讨论时为了方便起见一开始就会省略了许多的参考因素但是实际上的电子产品不可能是如此的。 在此我们以图十三的一个典型的电路来说明在图中有两个反向器分别处理不同的信号反向器1是当作一个时脉的缓衡器(clock buffer)而反向器2则是在I/O电缆上驱动一个输出信号在电路板上的电源供应的铜线其每英寸约有20nH对100MHz频率而言走线的阻抗每英寸约在10到20之间。 由于这两个反向器都是使用相同的Vcc及Ground回路所以即使在输出的反向器2其本身所驱动的是一个没有震荡的信号但是反向器1所产生的共模电压还是会透过走线使得反向器2输出信号随着时脉信号而上下震荡。 此共模信号的能量是和反向器2无关在这个例子中 其可能达到200 milli伏特这种电压所产生的辐射很容易超过一般EMI的限制规格。 这个例子说明了我们在对策时很容易忽略的问题许多人在发现I/O部分噪声很高就会把修改的重点放在反向器2的上面 但是事实上整个共模噪声电压主要是由反向器1所造成。如果从Vcc及Ground回路的观点来看可以很清楚的了解由于反向器2的电源的和接地都是从反向器1这边过来的所以对

《电磁兼容的设计方法介绍》由会员壹****1分享,可在线阅读,更多相关《电磁兼容的设计方法介绍》请在金锄头文库上搜索。

2014华师在线计算机考试答案

农村信用社网上银行业务知识试题与答案

高三高考百日冲刺宣誓词

2023年个人月工作总结12篇(最新个人月工作总结)

交通安全管理主题策划方案(2篇)

加油站连锁营销方案

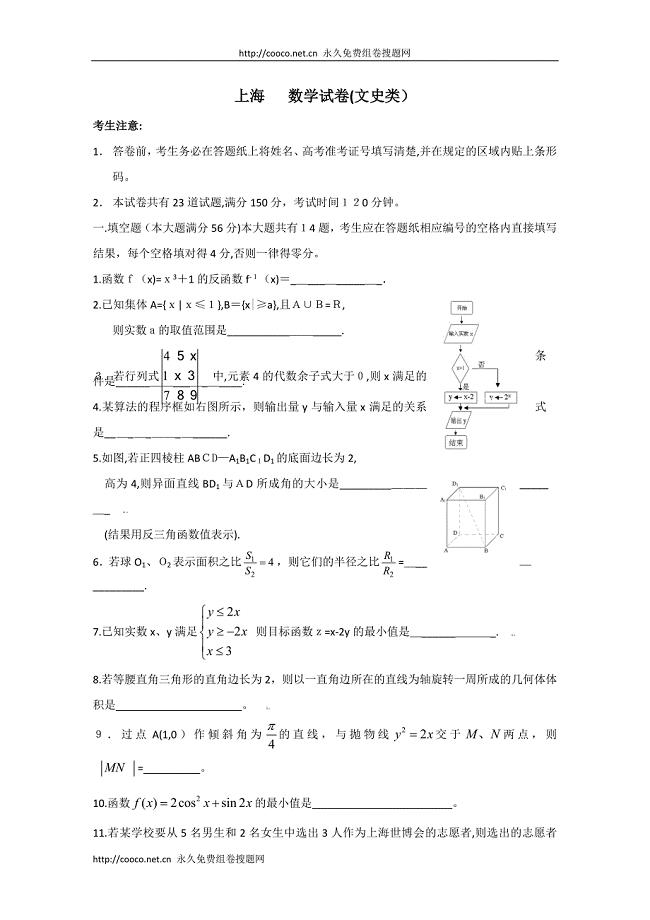

普通高等学校招生全国统一考试数学卷上海.文含答案高中数学

马庄镇中心小学桶装饮用水专项整治自查报告

豫农人生态农业可行性报告

印刷有限公司人力资源手册

检验员工作总结

公司聚餐领导发言稿

2022年新学期小学生国旗下讲话稿范文十一篇

加盟连锁销售合同书(8篇).doc

高考单词分类记忆

2023年党支部建设自查报告范文精选5篇

2023学校食品卫生安全工作计划范文(4篇).doc

热门期中考试的作文合集10篇

2017华师在线《计算机基础》作业及答案

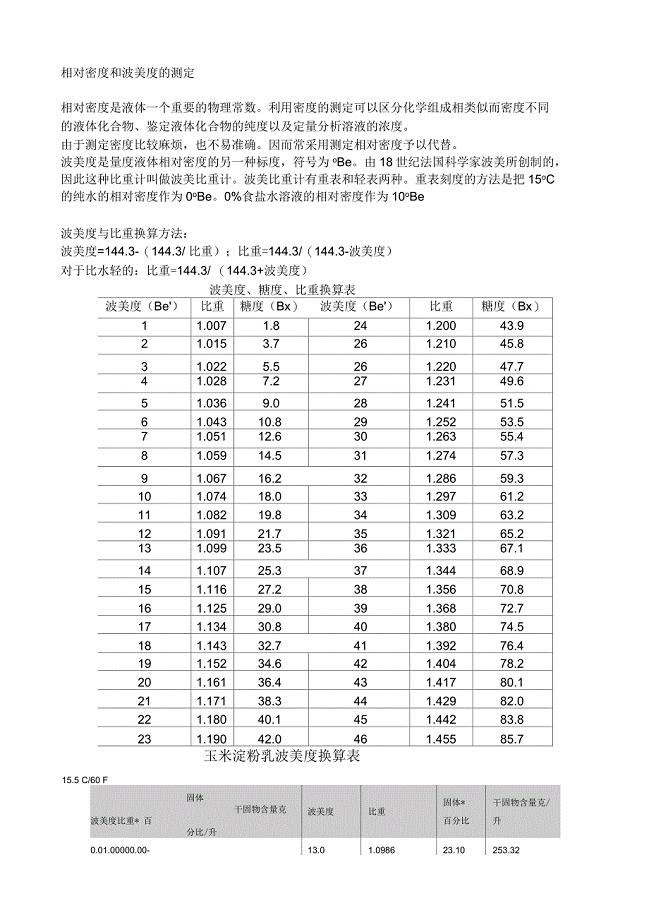

波美度糖度比重换算表

促进金融业发展若干政策措施

促进金融业发展若干政策措施

2022-10-03 4页

制氢装置安装工程施工组织设计

制氢装置安装工程施工组织设计

2022-09-06 96页

郑东新区白沙组团同德路道路工程白沙路青年路项目监理

郑东新区白沙组团同德路道路工程白沙路青年路项目监理

2023-07-24 87页

乌鲁木齐关于成立胶粘剂公司可行性报告

乌鲁木齐关于成立胶粘剂公司可行性报告

2023-02-05 107页

心系杭州公交伤者新昌电力职工热血融情

心系杭州公交伤者新昌电力职工热血融情

2023-01-18 2页

配置java环境变量(详细)

配置java环境变量(详细)

2023-01-21 4页

家庭分工明细表

家庭分工明细表

2022-08-21 4页

地基基础、主体分部及竣工验收流程

地基基础、主体分部及竣工验收流程

2023-06-05 4页

蓝蝶苑安全施工组织设计

蓝蝶苑安全施工组织设计

2022-11-05 80页

几类等值线的判读方法

几类等值线的判读方法

2023-11-07 8页