六十进制计数器的设计与仿真报告

13页1、 可编程器件实验报告六十进制计数器姓 名: 学 号: 班 级: 提交日期: 概要本次实验主要以学习使用MAX+plusII软件,编写六十进制计数器源程序,并对其进行时序仿真,得到仿真波形。目录前言第一章 VHDL语言介绍1.1 VHDL发展史1.2 VHDL的特点第二章 六十进制计数器的设计与仿真2.1 六十进制计数器源程序2.2 运用软件设计过程2.3 时序仿真体会前言本项实验通过六十进制计数器的设计与仿真,学习VHDL语言及VHDL文本输入设计方法,编写六十进制计数器源程序,应用MAX+PlusII软件进VHDL文本输入设计与波形仿真。写出源程序,并写出设计与仿真过程。第一章 VHDL语言介绍1.1 VHDL发展史硬件描述语言(hardware description language,HDL)是电子系统硬件行为描述,结构描述,数据流描述的语言.目前,利用硬件描述语言可以进行数字电子系统的设计.随着研究的深入,利用硬件描述语言进行模拟电子系统设计或混合电子系统设计也正在探索中.国外硬件描述语言种类很多,有的从Pascal发展而来,也有一些从C语言发展而来.有些HDL成为IEEE标准

2、,但大部分是企业标准.VHDL来源于美国军方,其他的硬件描述语言则多来源于民间公司.可谓百家争鸣,百花齐放.这些不同的语言传播到国内,同样也引起了不同的影响.在我国比较有影响的有两种硬件描述语言:VHDL语言和Verilog HDL语言.这两种语言已成为IEEE标准语言.电子设计自动化(electronic design automation,EDA)技术的理论基础,设计工具,设计器件应是这样的关系:设计师用硬件描述语言HDL描绘出硬件的结构或硬件的行为,再用设计工具将这些描述综合映射成与半导体工艺有关的硬件配置文件,半导体器件FPGA则是这些硬件配置文件的载体.当这些FPGA器件加载,配置上不同的文件时,这个器件便具有了相应的功能.在这一系列的设计,综合,仿真,验证,配置的过程中,现代电子设计理论和现代电子设计方法贯穿于其中.以HDL语言表达设计意图,以FPGA作为硬件实现载体,以计算机为设计开发工具,以EDA软件为开发环境的现代电子设计方法日趋成熟.在这里,笔者认为,要振兴我国电子产业,需要各相关专业的人士共同努力.HDL语言的语法语义学研究与半导体工艺相关联的编译映射关系的研究,

3、深亚微米半导体工艺与EDA设计工具的仿真,验证及方法的研究,这需要半导体专家和操作系统专家共同努力,以便能开发出更加先进的EDA工具软件.软件,硬件协同开发缩短了电子设计周期,加速了电子产品更新换代的步伐.毫不夸张地说,EDA工程是电子产业的心脏起搏器,是电子产业飞速发展的原动力.本书从应用的角度向国内广大读者介绍VHDL编程技术,让大家掌握HDL编程,了解FPGA结构,学会使用EDA工具,为集成电路前端设计打下基础.VHDL语言的英文全名是Very High Speed Integrated Circuit Hardware Description Language,即超高速集成电路硬件描述语言.HDL发展的技术源头是:在HDL形成发展之前,已有了许多程序设计语言,如汇编,C,Pascal,Fortran,Prolog等.这些语言运行在不同硬件平台和不同的操作环境中,它们适合于描述过程和算法,不适合作硬件描述.CAD的出现,使人们可以利用计算机进行建筑,服装等行业的辅助设计,电子辅助设计也同步发展起来.在从CAD工具到EDA工具的进化过程中,电子设计工具的人机界面能力越来越高.在利用

4、EDA工具进行电子设计时,逻辑图,分立电子原件作为整个越来越复杂的电子系统的设计已不适应.任何一种EDA工具,都需要一种硬件描述语言来作为EDA工具的工作语言.这些众多的EDA工具软件开发者,各自推出了自己的HDL语言.HDL发展的社会根源是:美国国防部电子系统项目有众多的承包公司,由于各公司技术路线不一致,许多产品不兼容,他们使用各自的设计语言,使得甲公司的设计不能被乙公司重复利用,造成了信息交换困难和维护困难.美国政府为了降低开发费用,避免重复设计,国防部为他们的超高速集成电路提供了一种硬件描述语言,以期望VHDL功能强大,严格,可读性好.政府要求各公司的合同都用它来描述,以避免产生歧义.由政府牵头,VHDL工作小组于1981年6月成立,提出了一个满足电子设计各种要求的能够作为工业标准的HDL.1983年第3季度,由IBM公司,TI公司,Intermetrics公司签约,组成开发小组,工作任务是提出语言版本和开发软件环境.1986年IEEE标准化组织开始工作,讨论VHDL语言标准,历时一年有余,于1987年12月通过标准审查,并宣布实施,即IEEE STD 10761987LRM8

《六十进制计数器的设计与仿真报告》由会员re****.1分享,可在线阅读,更多相关《六十进制计数器的设计与仿真报告》请在金锄头文库上搜索。

打造高效的营销团队

信息时代办公室里不应该有个人隐私-信息时代

拓展训练_团队游戏大全(含图片)

泌尿学习笔记完整

安全技术交底——履带式挖掘机

新版部编本二年级上册语文第一至三单元内容含课文口语交际及语文园地全部教案

高中语文 2.6《辛弃疾词两首》宋词名篇赏析素材 新人教版必修4

小学语文课外阅读卡(模板)

2019年知名企业产品跟踪及取样批次的隔离精华版

傲慢与偏见读后感800字

二手设备买卖合同15篇

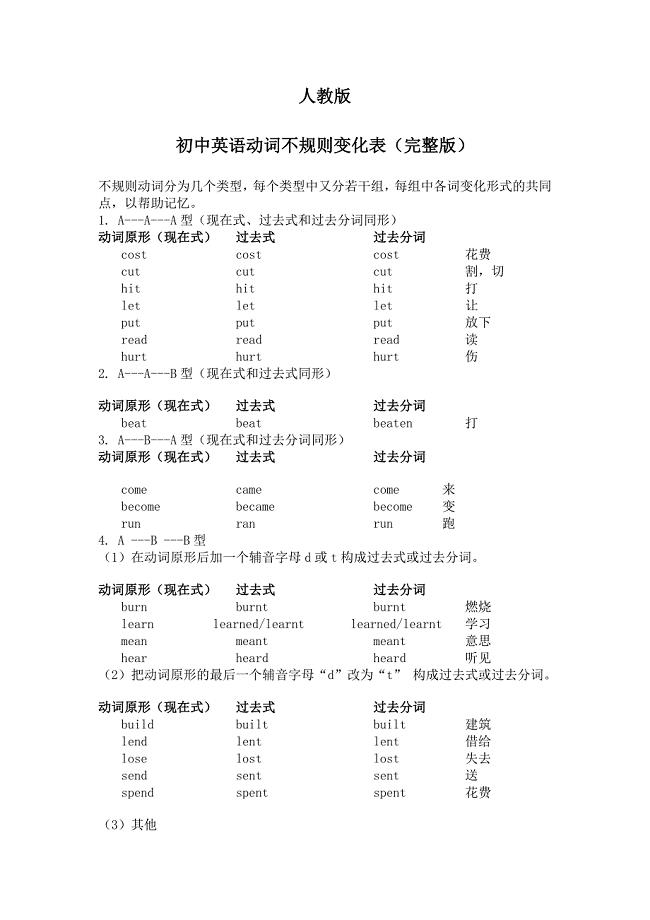

人教版初中英语动词不规则变化表

2023幼儿园中班班务工作计划下学期精编(三篇).doc

蔬菜冷藏保鲜库项目商业计划书写作参考

公司办公室工作总结及计划

离婚后财产纠纷办案指引

2022年以舞蹈为主题的演讲稿高中

![广东惠州龙门县投资促进中心公开招聘政府购买服务岗位人员(同步测试)模拟卷[3]](https://union.152files.goldhoe.com/2022-12/23/adfaf087-25bf-47c3-a024-88b49f9050e4/pic1.jpg)

广东惠州龙门县投资促进中心公开招聘政府购买服务岗位人员(同步测试)模拟卷[3]

2023年教师个人工作计划(6篇).doc

![[融资租赁的优势有哪些]](https://union.152files.goldhoe.com/2023-5/4/100f25aa-472c-4a4d-9c48-5093acb892b2/pic1.jpg)

[融资租赁的优势有哪些]

高考英语二轮阅读理解能力提升演练08

高考英语二轮阅读理解能力提升演练08

2023-04-30 7页

新版陕西省渭南市尚德中学高三第二次月考地理试卷含答案

新版陕西省渭南市尚德中学高三第二次月考地理试卷含答案

2023-11-18 14页

译林版9年级英语上册教案课件第5课Unit5知识梳理

译林版9年级英语上册教案课件第5课Unit5知识梳理

2023-11-09 4页

五年级语文上册文言文阅读与理解考点练习语文版

五年级语文上册文言文阅读与理解考点练习语文版

2024-02-25 6页

信息化综合运维体系

信息化综合运维体系

2023-08-03 22页

201x年11月浙江选考化学试卷和答案

201x年11月浙江选考化学试卷和答案

2023-07-26 12页

园林绿化质量保证措施

园林绿化质量保证措施

2023-08-13 7页

深圳大族激光数控激光切割机G3015CS2200方案书lxpeng

深圳大族激光数控激光切割机G3015CS2200方案书lxpeng

2023-06-05 27页

财务报表分析习题

财务报表分析习题

2022-09-28 5页

“我和医院”演讲比赛精简版

“我和医院”演讲比赛精简版

2023-03-27 6页