基于FPGA的异步收发器程序的设计说明

20页1、毕业设计设计题目 基于FPGA的异步收发器设计学 院:物理科学与工程技术学院 专 业: 电子信息工程 年 级: 10级 姓 名: 淑珍 指导教师: 王 永 祥 职 称: 副 教 授 (2013 年 6月)学院教务处制基于FPGA的异步收发器设计 学院 物理科学与工程技术学院 电子信息工程 扬 指导老师: 王永祥摘要:文章简要介绍了UART的基本功能,采用Verilog HDL语言作为硬件功能的描述,运用模块化设计方法设计了通用异步收发器的发送模块、接收模块和波特率发生器。实现了基于FPGA的UART基本功能设计,并给出了UART的软件编程实例.关键字:Verilog HDL;FPGA;UARTBased on SCM ultrasonic ranging system Design( YiChun University Physical science and engineering institute of technologyLi Yang)Abstract: this paper briefly introduces the basic function of UART, the

2、 Verilog HDL language as a description of the hardware function, using modular design method to design the general asynchronous transceiver module, receive send the module and baud rate generator. Realized the basic function of UART which based on FPGA , and gives the UART software programming examples. Key word: Verilog HDL; FPGA; UART; A / 引言21 . UART简介21.1 UART结构21.2 UART的帧格式21.3 UART的基本原理22 UART的设计与实现32.1 UART发送器32.2 UART接收器42.3数码管动态显示52.4 波特率发生器62.5 UART设计总模块63.FPGA UART系统组成74.模块设计84.1. 顶层模

3、块84.2波特率发生器104.3 UART发送器114.4 UART接收器155结语176.参考文献18引言由于微电子学和计算机科学的迅速发展,给EDA(电子设计自动化)行业带来了巨大的变化。特别是进入20世纪90年代后,电子系统已经从电路板级系统集成发展成为包括ASIC、FPGA/CPLD和嵌入系统的多种模式。可以说EDA产业已经成为电子信息类产品的支柱产业。EDA之所以能蓬勃发展的关键因素之一就是采用了硬件描述语言(HDL)描述电路系统。就FPGA和CPLD开发而言,比较流行的HDL主要有Verilog HDL、VHDL、ABEL-HDL和 AHDL 等,其中VHDL和Verilog HDL因适合标准化的发展方向而最终成为IEEE标准。下面的设计就是用VHDL来完成实现的。1 . UART简介UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是一种应用广泛的短距离串行传输接口。UART允许在串行链路上进行全双工的通信。 UART主要有由数据总线接口、控制逻辑、波特率发生器、发送部分和接收部分等组成。功能较为简单,但使

4、用方便、占用资源少,可以灵活地嵌入到各种设计之中。串行外设用到的RS232-C异步串行接口,一般采用专用的集成电路即UART实现。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。1.1 UART结构UART主要有由数据总线接口、控制逻辑、波特率发生器、发送部分和接收部分等组成。1.2 UART的帧格式UART是异步通信方式,发送方和接收方分别有各自独立的时钟,传输的速度由双方约定,使用起止式异步协议。起止式异步协议的特点是以每一个字符为单位进行传输,字符之间没有固定的时间间隔要求,每个字符都以起始位开始,以停止位结束。帧的格式如图一所示,每一个字符的前面都有一位起始位(低电平,逻辑值0),字符本身有5到8比特数据位组成,接着是一位校验位(也可以没有校验位),最后是一位(或一位半、二位)停止位,停止位后面是不定长度的空闲位。停止位和空闲位都规定为高电平,这样就保证了起始位开始处一定有一个下降沿。从图中可以看出,这种格式是靠起始位和停止位来实现字符的界定或同步的,故称为起止式协议。UART的帧格式的示意图如图一所示:图一 基本UART帧格式1.3 UART的基本原

《基于FPGA的异步收发器程序的设计说明》由会员大米分享,可在线阅读,更多相关《基于FPGA的异步收发器程序的设计说明》请在金锄头文库上搜索。

007药理学练习题-第七章胆碱受体阻断药.doc

生产系统安全环保管理考核办法

【小学生优秀日记范文】 优秀日记大全400字以上.docx

高等数学基本公式.doc

东莞数字农业技术研发项目投资计划书

2023年企业母亲节活动策划方案与企业法律顾问工作计划汇编

大学学生会部长竞选演讲稿15篇.doc

2016年高考必考英语语法大全

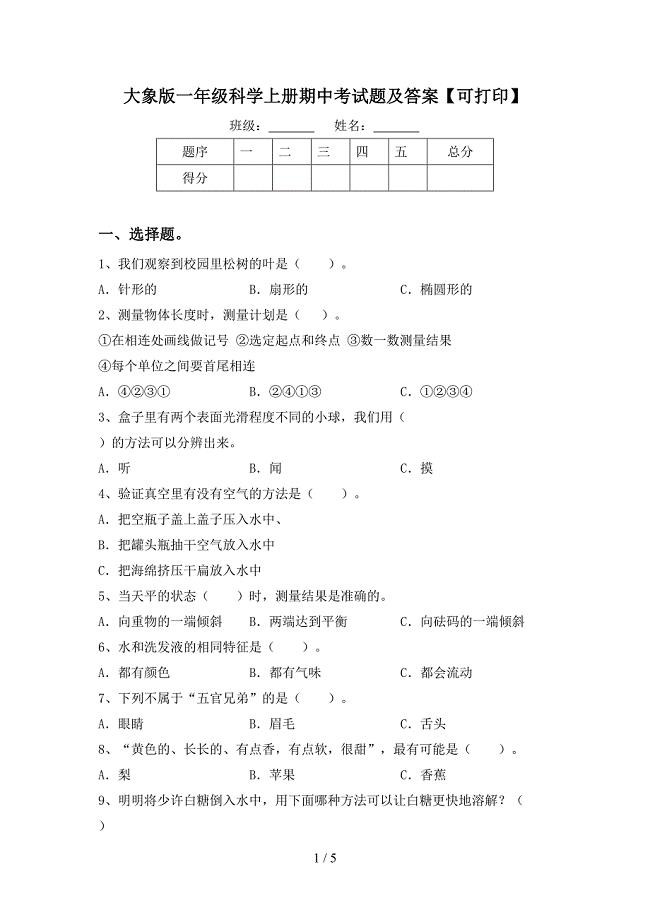

大象版一年级科学上册期中考试题及答案【可打印】.doc

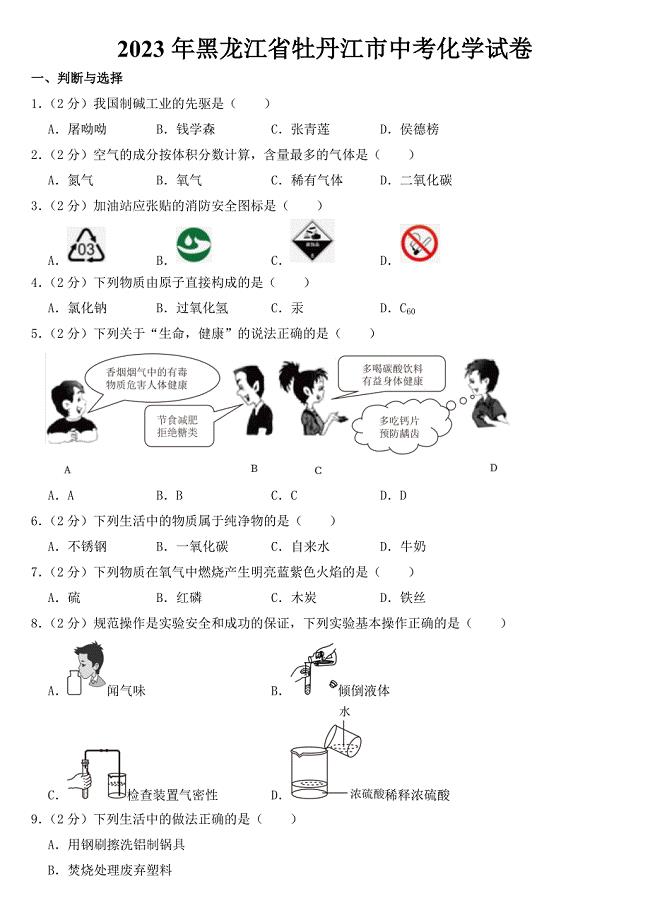

2023年黑龙江省牡丹江市中考化学试卷【含答案】.docx

2022人教版六年级上册数学期末卷含答案【黄金题型】.docx

精编【疫情期间大学生的责任担当】疫情下青年的责任与担当

弥漫性间质性肺疾病的临床诊断思路与程序.doc

安全例会会议制度

2023年交通运输工作意见.docx

李镇西:回眸我的三十年.doc

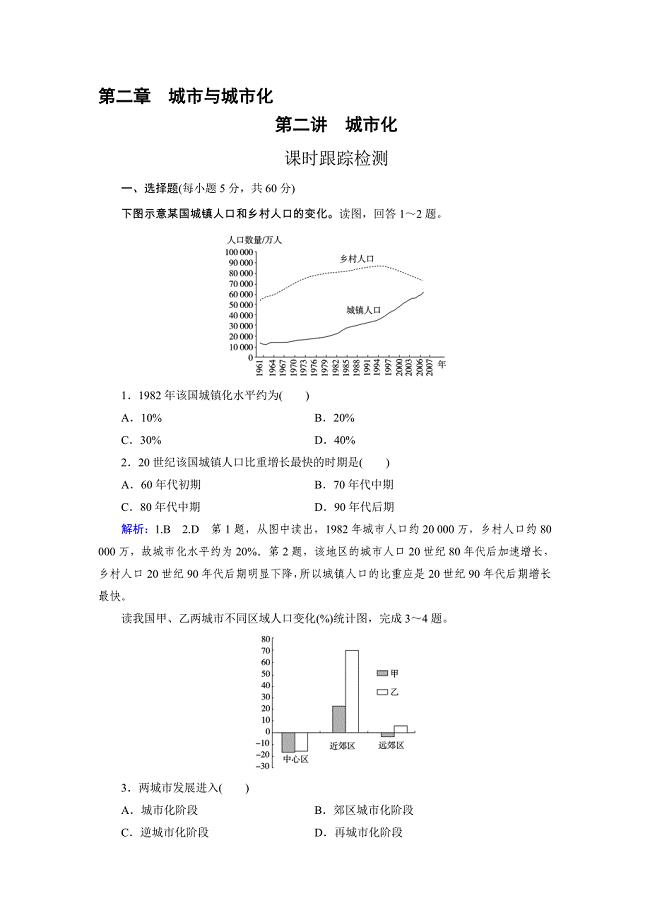

高三人教版地理总复习 人文地理 第2章 第2讲 课时 城市化Word版含解析高考汇编

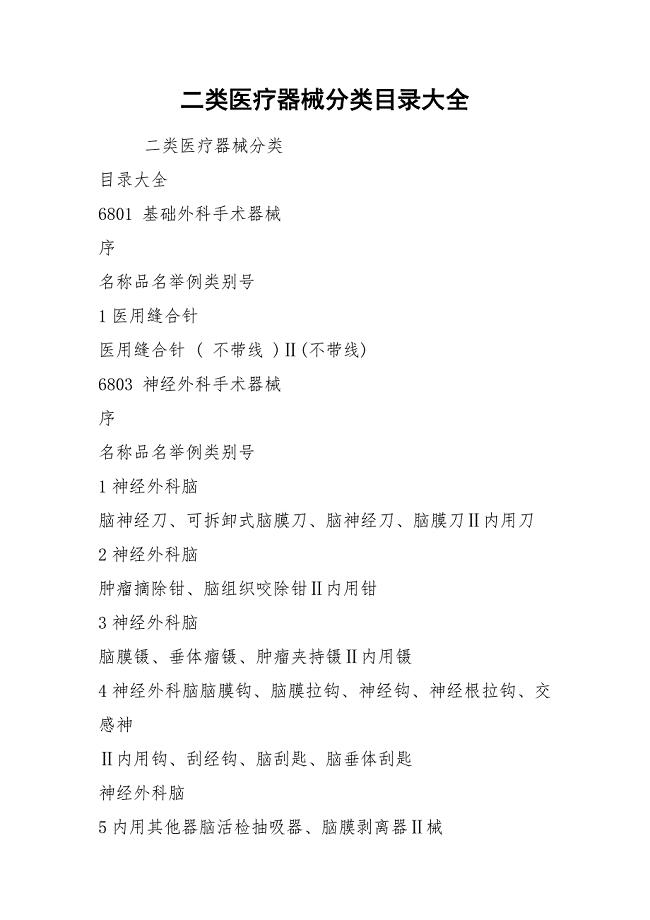

二类医疗器械分类目录大全

二年级下册数学期末测试卷加答案(综合题).docx

公司仓储物流部年终工作总结.doc

白落梅经典语句之八.docx

白落梅经典语句之八.docx

2022-11-28 6页

员工晋级加薪制度.doc

员工晋级加薪制度.doc

2024-01-08 7页

网站制作技术员专业简历.docx

网站制作技术员专业简历.docx

2022-10-14 10页

留学英国本科和硕士连读的要求.docx

留学英国本科和硕士连读的要求.docx

2022-09-15 8页

宿松县春润食品有限公司商业计划书.doc

宿松县春润食品有限公司商业计划书.doc

2023-08-02 27页

文字分镜Word表格.doc

文字分镜Word表格.doc

2023-11-06 21页

高低压招标书.doc

高低压招标书.doc

2023-05-12 44页

哄小孩子入睡的童话故事大全.docx

哄小孩子入睡的童话故事大全.docx

2023-08-22 5页

2022学生万能检讨书800字范文.docx

2022学生万能检讨书800字范文.docx

2023-08-21 6页

2021广告牌施工合同范文.docx

2021广告牌施工合同范文.docx

2023-08-13 5页