基于cpld的频率测量计

52页1、基于CPLD的频率测量计摘 要本文主要论述了利用CPLD进行测频计数,单片机实施控制实现等精度频率计的设计过程。该频率计利用等精度的设计方法,克服了基于传统测频原理的频率计的测量精度随被测信号频率的下降而降低的缺点。等精度的测量方法不但具有较高的测量精度,而且在整个频率区域保持恒定的测试精度。该频率计利用CPLD来实现频率的测量计数。利用单片机完成整个测量电路的测试控制、数据处理和显示输出。本文详细论述了硬件电路的组成和单片机的软件控制流程。其中硬件电路包括键控制模块、显示模块、输入信号整形模块以及单片机和CPLD主控模块。设计器件采用Atmel公司的单片机AT89C51和Altera公司的MAX7000系列EPM7128SLC84-15芯片。键控制模块设置1个开始键和3个时间选择键,键值的读入采用一片74LS165来完成;显示模块用8只74LS164完成LED的串行显示;被测信号经限幅后由两级直接耦合放大器进行放大,再经施密特触发器整形后输入CPLD;标准频率采用40MHz有源晶振动实现;单片机软件用汇编语言编写,软件模块对应于硬件电路的每一个部分,还包括部分数据计算和转换模块。关键

2、词:单片机,CPLD,频率计,测频,等精度THE DESIGN OF FREQUENCY MEASUREMENT BASED ON CPLDAbstractThe reach pape rmainly discusses the design process of equal-accuracy frequency meter that uses CPLD to count the frequency measurement and frequency meter is also controled by single chip computer. The frequency meter makes use of equal-accuracy design that can overcome the disadvantage of traditional measuring principle, which precision declines as measured signal frequency does. The equal-accuracy measurement not on

3、ly has higher measuring precision, but also can keep invariable measuring precision in whole area of frequency.This frequency meter uses CPLD to realize the measuring count of frequency. Single chip computer completes the test control、data processing and display output of the system.This essay discusses the compose of hardware circuit and software control flow of single chip computer in detail. Hardware circuit includes key control module、display module, plastic module of input signal、single chi

4、p computer control module and CPLD main control module.The frequency meter adopts single chip computer AT89C51 of Atmel company and EPM7128SLC84-15 of Altera company. Key control module has 1 function key and 3 time selection key. A chip 74LS165 completes the key value input. Display module uses eight 74LS165s to realize the serial display of LED. First, the measuring signal amplitude is limited. Second, the single is amplified by two class direct coupling amplifier. Finally, the signal inputs C

《基于cpld的频率测量计》由会员壹****1分享,可在线阅读,更多相关《基于cpld的频率测量计》请在金锄头文库上搜索。

行政办公室主任岗位职责(五篇).doc

重酒石酸卡巴拉汀胶囊-详细说明书与重点

静压预应力管桩试桩及检测要求

机械设计课程设计(二级减速器)直齿轮.doc

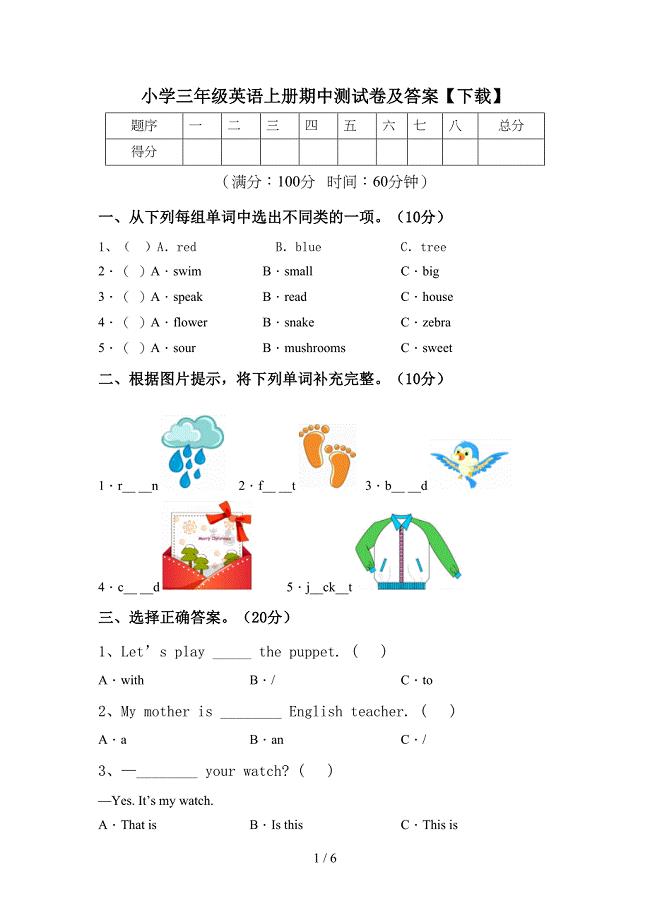

小学三年级英语上册期中测试卷及答案【下载】.doc

汇金城住宅楼一期_工程监理月报.doc

水平铸造机更新及技术改造立项总结.doc

2022年酒店董事长年会致辞.docx

新人教版四年级语文下册期中试卷附答案(2套).docx

CDMA技术的应用和发展.doc

治疗骨质疏松的药物研究进展 (2).doc

建设LED显示屏、多媒体设备生产制造项目资金申请报告写作模板

小学生作业展评活动总结

第十章循环系统.doc

2023年经验交流会新闻稿多篇.docx

医院下乡义诊活动总结(2篇).doc

生物亲缘关系探索.doc

【教育资料】小学五年级语文:春光染绿我们双脚(2).doc

服装销售个人工作计划范文.docx

有氧呼吸教案

外周血正常白细胞形态

外周血正常白细胞形态

2022-12-19 9页

电信学院毕业论文模板

电信学院毕业论文模板

2023-02-10 23页

路灯工程的施工组织设计

路灯工程的施工组织设计

2022-09-25 101页

省级课题开题报告书

省级课题开题报告书

2022-10-27 13页

如何选取合适的电缆口诀和表格

如何选取合适的电缆口诀和表格

2022-09-18 4页

豪放飘逸的李白诗专题测试精

豪放飘逸的李白诗专题测试精

2022-12-02 14页

数据库原理在线作业4

数据库原理在线作业4

2022-12-18 8页

第二学期小学语文教研组工作总结

第二学期小学语文教研组工作总结

2023-10-14 5页

低温甲醇洗净化工艺

低温甲醇洗净化工艺

2023-09-28 8页

液氨知识.doc

液氨知识.doc

2024-01-08 6页