基于VHDL计时抢答器设计

45页1、大庆师范学院本科毕业论文(设计)摘 要抢答器作为一种电子产品,早已广泛应用于各种智力和知识竞赛场合,是竞赛问答中一种常用的必备装置,从原理上讲,它是一种典型的数字电路,电路结构形式多种多样,可以利用简单与非门构成,也可以利用触发器构成,也可以利用单片机来完成。本设计是基于VHDL语言控制的八路抢答器,通过分析抢答器的工作原理,设计包括抢答程序及在相应的器件平台上完成输入、编译、综合应用等不同功能的单元模块,并具体介绍了每一单元模块的具体设计思路与结构,利用单片机的定时器或计时器定时和计数的原理,将软硬件有机的结合起来,使得系统它能够正确的计时,同时使数码管能够正确的显示时间。且在设计完成后给出仿真来增强设计的真实感。关键词:VHDL语言;抢答器;仿真10AbstractThe contest as a kind of electronic products, has long been widely applied in all kinds of intelligence and knowledge competition situation, is a kind of common

2、competition q&a necessary device, from the principle of speaking, it is a kind of typical digital circuit, the circuit structure form varied, can use simple sr and form, also can use a flip-flop, also can use single chip microcomputer to complete. The design is based on VHDL language control for 8 vies to answer first, through the analysis of the working principle of vies to answer first, design including vies to answer first program and in the corresponding device platform complete input, compi

3、lation, comprehensive application and so on the different function of the unit module, and introduced the each unit of the specific module design and structure, of the microcontroller timer or timer timing and count principle, software and hardware organic combine, the system can be correctly it time, at the same time make digital tube can be correctly show time. And after the completion of the design are given in the design of the realism to strengthen.Keywords: VHDL language; Digital time vies

4、 to answer first device; The simulation目 录第一章 引言11.1 背景11.2 VHDL语言简介1第二章 设计的基本要求与要点22.1 八路数字计时抢答器的设计要求22.2 系统设计要点2第三章 八路数字计时抢答器设计33.1 工作原理33.2 硬件设计中各模块的设计43.2.1概述43.2.2抢答器鉴别模块43.2.3译码模块53.2.4定时器模块53.2.5报警模块53.3 单元电路VHDL设计63.3.1VHDL实体设计63.3.2关于VHDL构造体的设计部分63.3.3译码模块VHDL程序73.3.4定时模块VHDL程序83.3.5报警模块VHDL程序9第四章 仿真验证114.1 仿真验证114.2 设计电路各模块仿真图114.2.1抢答鉴别模块仿真及元件图114.2.2译码模块仿真及元件图124.2.3计数模块仿真及元件图124.2.4报警模块仿真及元件图13第五章 心得与体会14参 考 文 献15第一章 引言1.1 背景抢答器是举办各种娱乐活动、开展智力竞赛时常用的一种设备。抢答器有很多设计方法,既可用传统的集成电路PCB(印制电路板

《基于VHDL计时抢答器设计》由会员m****分享,可在线阅读,更多相关《基于VHDL计时抢答器设计》请在金锄头文库上搜索。

红楼梦人物名字谐音

学年新教材高中生物第章基因的本质第节DNA是主要的遗传物质练习含解析新人教版必修第二册.docx

2010年高考最新作文素材分类:求知成事

全水低密度热塑性聚氨酯泡沫的制备.doc

钢筋结构吊装专项方案

一年级下学期小学语文期末真题模拟试卷RM2.docx

《啪嗒砰》玩家心得详细攻略.doc

小学班主任工作经验交流范例.docx

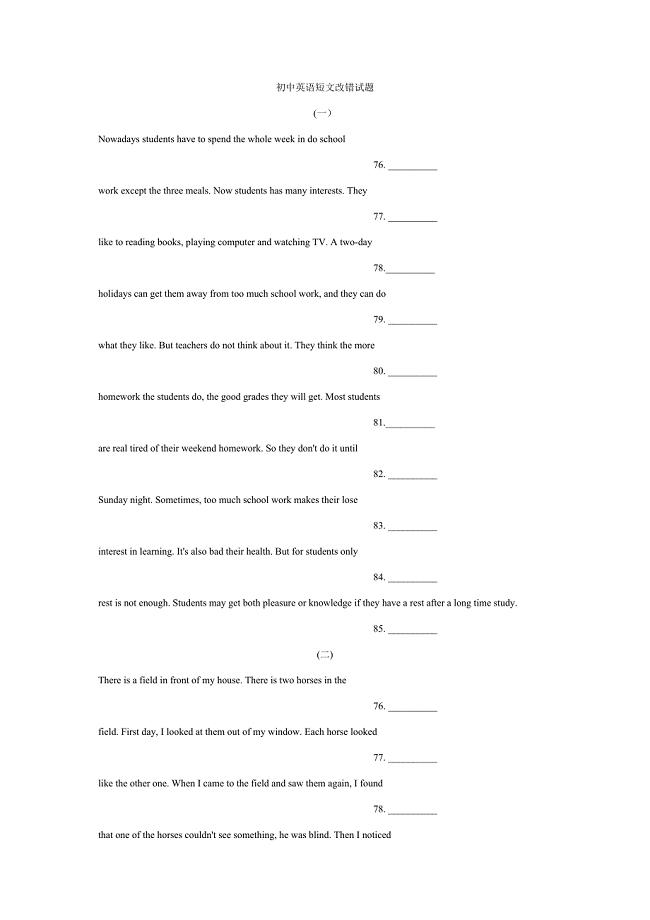

(完整)初中英语短文改错.doc

学生会主席优秀辞职报告

妇女节创始人克拉拉蔡特金简介.docx

蓝领入职流程图.doc

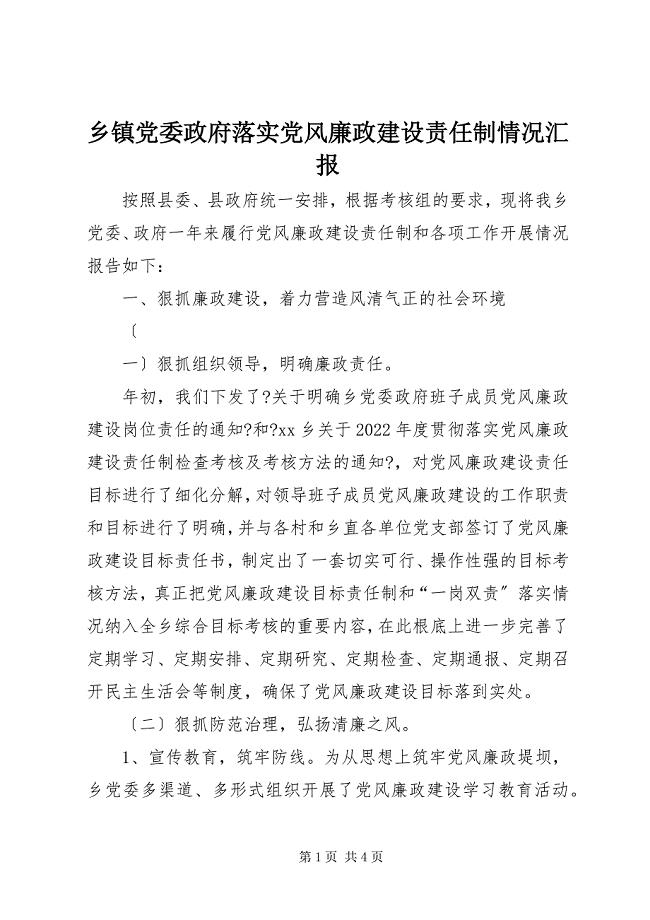

2023年乡镇党委政府落实党风廉政建设责任制情况汇报.docx

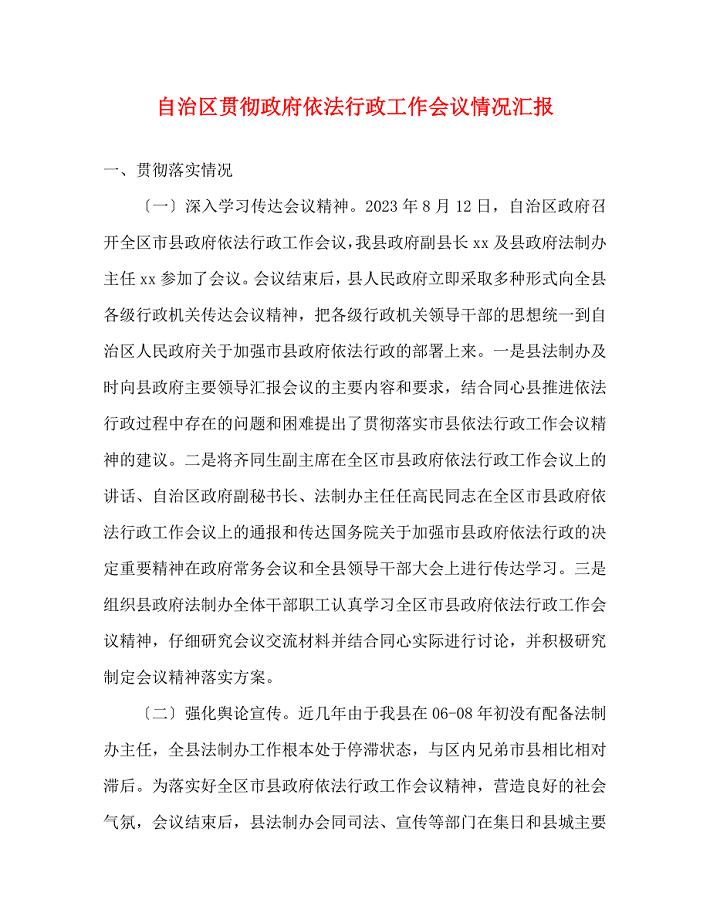

2023年自治区贯彻政府依法行政工作会议情况汇报.docx

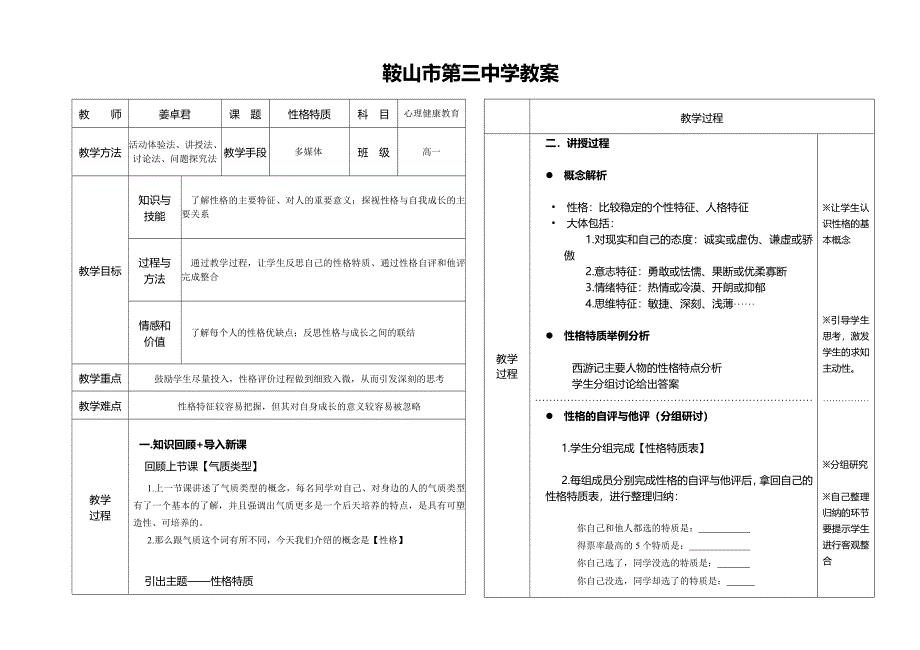

心理健康教育教学案例6.doc

![2、学会查“无字词典”[教学].doc](https://union.152files.goldhoe.com/2023-11/23/9198daa6-00dd-4f99-b83c-6adf28107136/pic1.jpg)

2、学会查“无字词典”[教学].doc

幼儿园环境创设方案马婵

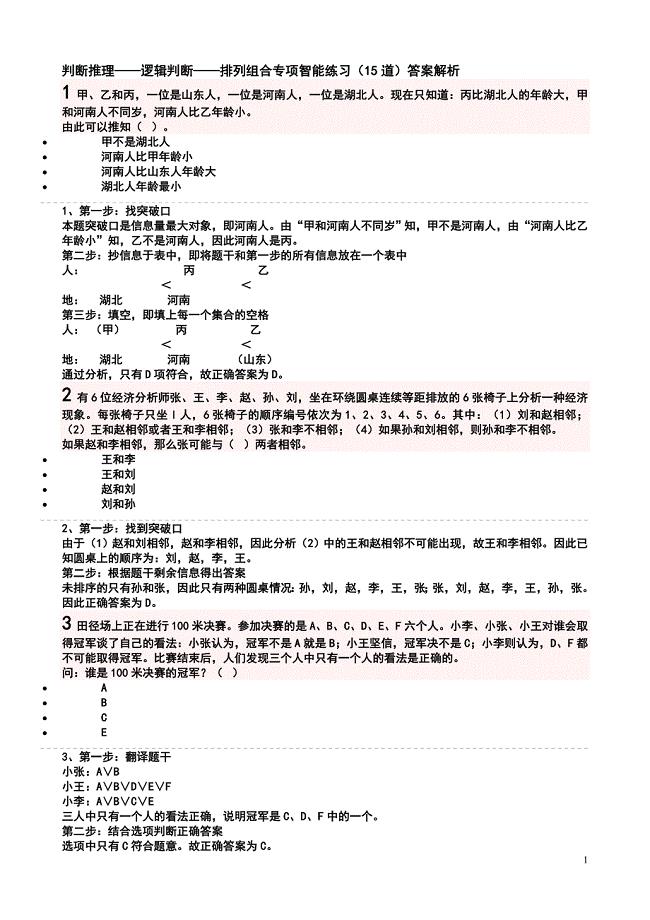

逻辑判断-排列组合.doc

车间考核标准管理

智囊太公孔子

福寿两全保险(利差返还型)条款.docx

福寿两全保险(利差返还型)条款.docx

2023-08-13 16页

汽车维修合同.docx

汽车维修合同.docx

2023-03-28 7页

浙江省房屋中介委托合同(出售出租).docx

浙江省房屋中介委托合同(出售出租).docx

2023-07-13 9页

讲话精神的发言稿.docx

讲话精神的发言稿.docx

2024-02-03 3页

外文翻译--平衡梁的剪力和弯矩.doc

外文翻译--平衡梁的剪力和弯矩.doc

2023-02-25 5页

讲话发言稿结尾.docx

讲话发言稿结尾.docx

2023-10-07 3页

复学国旗讲话发言稿.docx

复学国旗讲话发言稿.docx

2023-01-12 3页

31.流动商贩管理模式新探索(天选打工人).docx

31.流动商贩管理模式新探索(天选打工人).docx

2023-04-25 31页

大学生自助厨房学姐陪你比赛加油!(天选打工人).docx

大学生自助厨房学姐陪你比赛加油!(天选打工人).docx

2023-11-01 17页

农产品订单合同.docx

农产品订单合同.docx

2024-03-20 4页