Cache(高速缓存)与主存一致性初探毕业论文

21页1、本科生毕业论文(设计)Cache(高速缓存)与主存一致性初探院系名称信息工程系姓名姓 名学号2008341142专业计算机科学与技术专业指导教师导师 教授2012年3月25日1摘要存储器是具有“记忆”功能的部件,它在计算机系统中占有十分重要的地位。存储器的基本功能是存放以二进制形式表示的程序与数据。如何设计容量大、速度快且造价低的存储器,一直是计算机发展中的关键问题,目前还没有哪一种存储器功能完全满足计算机系统对存储器的需求。因此,计算机系统通常配备分层结构的存储系统,以满足容量、速度和造价等方面的要求。衡量存储器有三个指标:容量、速度和价格/位。一般地说,速度高的存储器,每位价格也高,因此容量不能太大。所以存储器设计的约束有容量、速度和价格。容量似乎没有限制,不管容量多大,总要开发出应用程序来使用。为了获得更好的性能,存储器的速度必须能够跟上CPU,即当CPU执行指令时,不想让他停下来等待指令或操作数。价格问题也必须考虑,对于实用的系统,存储器的价格必须相对于其他部件是合理的。因此三个指标之间需要进行权衡。高速缓存系统中能否确保高速缓冲存储器和主存内容一致性,这个问题直接关系到整个计

2、算机系统的性能。这两部分的数据一致性问题产生的原因有二:其一,由于CPU对高速缓冲存储器的写入导致它的内容更新而主存内容陈旧;其二,由于I/O处理机或多处理机系统中某一处理机修改了主存内容导致高速缓冲存储器内容陈旧。针对不同原因,分析了写策略中七种解决方案,并就高速缓存系统采用的第二级脱片高速缓冲存储器,以及第三级脱片高速缓冲存储器结构数据一致性问题进行初步探讨。本文通过对存储器系统Cache(高速缓存)与主存的概念进行描述和目前两者之间一致性存在的一些问题进行研究。并分析在多处理机系统中,主存与各处理机私有Cache之间及各私有Cache之间存在的数据不一致性。对解决不一致性的方法:监听总线协议、基于目录的Cache一致性协议、软件控制方法等进行详细的定性分析,并指出各种方法的优缺点,供设计者参考;同时提出软件和硬件相结合的方法,能有效解决Cache的一致性问题。关键词:存储器;主存;缓存;一致性AbstractMemory is a memory function components , it in a computer system occupies a very import

3、ant position . The basic function of memory is stored in binary form of said programs and data . How to design capacity , speed is quick and low cost of memory , is always the key problems in the development of the computer , there is no memory function fully meet the needs of the memory of a computer system. Therefore, the computer system usually equipped with a layered structure of storage system, to satisfy the capacity, speed and cost requirements.Measure memory has three index : capacity ,

4、speed and price/a. Generally speaking , the high speed of memory, every price is high , therefore capacity can not be too big . So memory design constraints capacity , speed and price . There seems to be no limit capacity , no matter how much capacity , the total to develop applications to use . In order to obtain the better performance, the speed of the memory must be able to keep up with the CPU,and that is when the CPU executing instructions , dont want him to stop and wait for instructions o

《Cache(高速缓存)与主存一致性初探毕业论文》由会员鲁**分享,可在线阅读,更多相关《Cache(高速缓存)与主存一致性初探毕业论文》请在金锄头文库上搜索。

中考冲刺校长的讲话稿模板.doc

李宝元个人简介

第一课开国大典.docx

单位公司企业责任中心划分及职责.docx

2023年新版幼儿园幼教个人工作总结荟萃5篇.docx

国际贸易理论与实务案例汇编.docx

论文:课堂提问需要精心预设.doc

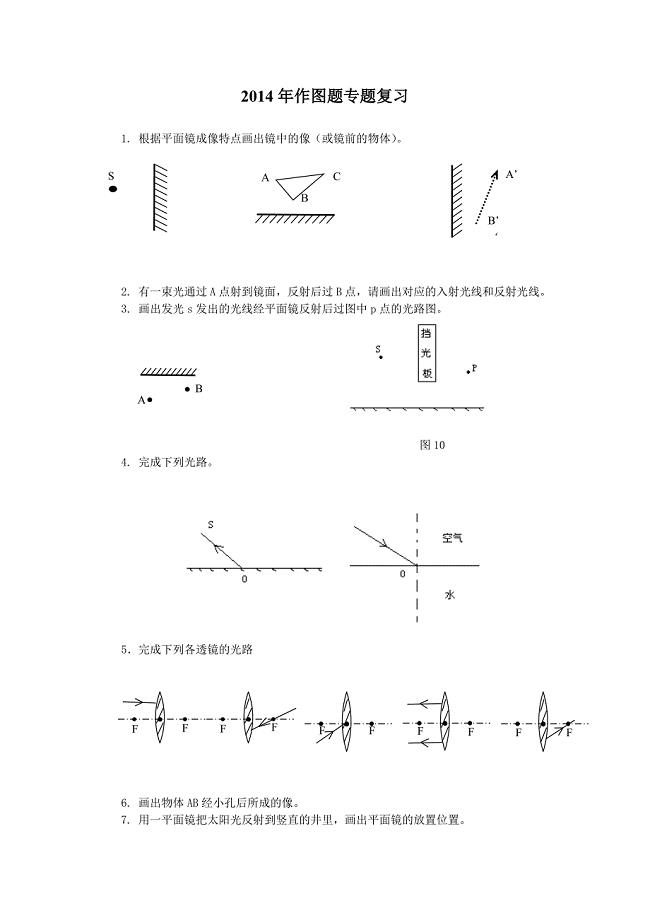

作图题专题复习

2023年春季园务工作总结(范文).doc

It,One,That三词之用法区别.doc

la la land 歌词.doc

2023年政治部副主任、干部(警务)处处长群众路线教育学习交流发言材料.docx

哈利波特与魔法石读后感(汇编17篇).docx

企业员工劳动合同范本

![家务劳动我能行[46].docx](https://union.152files.goldhoe.com/2023-6/8/15d70979-cc06-44aa-aaaf-23f4caf1419c/pic1.jpg)

家务劳动我能行[46].docx

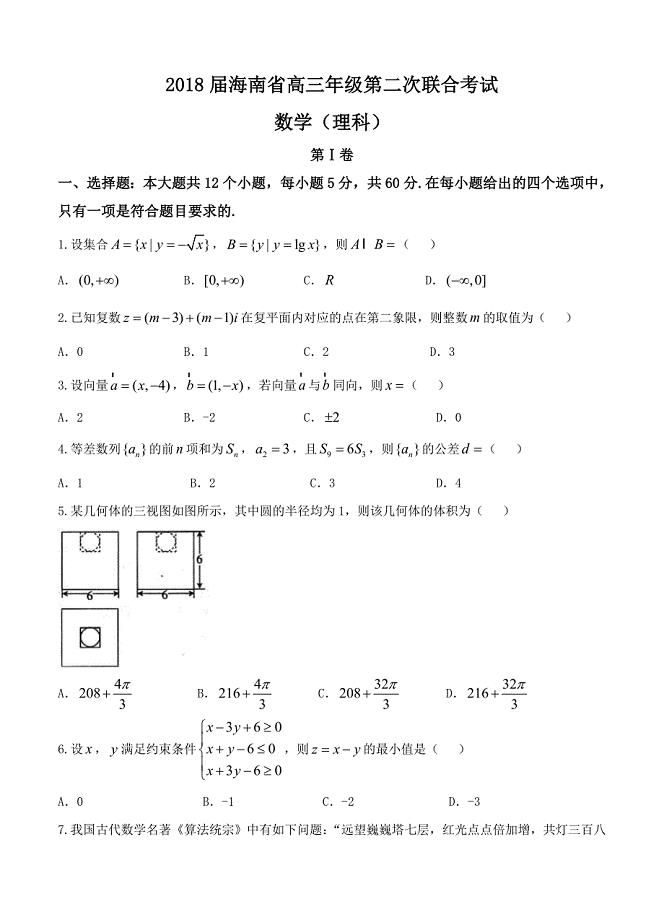

海南省高三第二次联合考试数学理试卷含答案

2023年企调队工作总结.docx

2023年辞职申请(报告).docx

第一章 服装成因.doc

基于单片机停车场自动停车升降系统设计资料.doc

徐志姣教学设计.docx

徐志姣教学设计.docx

2023-08-03 7页

榆林市幼儿园常规管理基本要求(试行).doc

榆林市幼儿园常规管理基本要求(试行).doc

2023-06-02 9页

有关于国庆节优秀日记(精选20篇)

有关于国庆节优秀日记(精选20篇)

2022-10-07 19页

温度和温度计学习学习教学1115092824.doc

温度和温度计学习学习教学1115092824.doc

2023-11-05 3页

我的成长感悟.doc

我的成长感悟.doc

2023-01-27 3页

时间像小马车教学设计.docx

时间像小马车教学设计.docx

2022-08-22 3页

小班科学活动有趣的睡姿.doc

小班科学活动有趣的睡姿.doc

2023-06-23 3页

《牛顿第一定律》学案.docx

《牛顿第一定律》学案.docx

2023-10-08 4页

北师大版小学数学一年级上册期末试卷 (3).doc

北师大版小学数学一年级上册期末试卷 (3).doc

2023-09-21 20页

二元一次方程练习题.doc

二元一次方程练习题.doc

2022-09-30 9页