FPGA跨时钟域信号设计

9页1、跨越鸿沟:同步世界中的异步信号页码,#/7跨越鸿沟:同步世界中的异步信号作者:Mike Stein , Paradigm Works开栏的话从本期起,EDN CHINA电子设计技术将正式推岀 技术论坛”这个新栏目。通过这个栏目,我们将向广大读者定期 推介来自业界领先的技术供应商的充满了设计灵思的、最前沿的、高质量的技术文章;同时也会采用一系列创新的形式促 进设计工程师与技术供应商的沟通与互动。这样以来,当每个月读者拿到EDN CHINA杂志时,就好象是足不岀户参加了一 个技术研讨会,享受了一顿丰盛的信息 大餐”虽说是新”栏目,但实际上作为它前身的 技术交流”一原先技术纵横”中的子栏目一一已经与读者相伴很多年了,这 种对新技术的传播方式也已经得到了读者和技术供应商双方的认同。技术交流中的文章在www.EDNC上的点击 率排名总是名列前茅就是一个很好的例证。现在我们将 技术交流”升格为一个独立的技术论坛”栏目,其最主要的用意就是 给这个栏目一个更广阔、更自由的发展空间。而对于技术交流”栏目所开创的刊网互动”的形式,我们仍将沿用。同时我们也将充分利用网络平台为读者提供更富于 想象力的交互式的

2、信息服务,比如读者可以将基于某篇文章的启发所迸发岀的灵感火花发布到 EDNC网站上,经 过我们的编辑整理则可以刊登在杂志上与更多的业内同仁分享。新的栏目是一种新的尝试,当然其发展也需要读者热心的支持。而实际上你会发现,你的参与意识越强,技术论坛”所给予你的越丰富一一这也正是我们的编辑理想所在。只有最初级的逻辑电路才使用单一的时钟。大多数与数据传输相关的应用都有与生俱来的挑战,即跨越多个时钟域的 数据移动,例如磁盘控制器、CDROM/DVD控制器、调制解调器、网卡以及网络处理器等。当信号从一个时钟域传送到另一个时钟域时,岀现在新时钟域的信号是异步信号。在现代IC、ASIC以及FPGA设计中,许多软件程序可以帮助工程师建立几百万门的电路,但这些程序都无法解决信 号同步问题。设计者需要了解可靠的设计技巧,以减少电路在跨时钟域通信时的故障风险。基础从事多时钟设计的第一步是要理解信号稳定性问题。当一个信号跨越某个时钟域时,对新时钟域的电路来说它就是一 个异步信号。接收该信号的电路需要对其进行同步。同步可以防止第一级存储单元(触发器)的亚稳态在新的时钟域里传 播蔓延。亚稳态是指触发器无法在某个规定

3、时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元 的输岀电平,也无法预测何时输岀才能稳定在某个正确的电平上。在这个稳定期间,触发器输岀一些中间级电平,或者可 能处于振荡状态,并且这种无用的输岀电平可以沿信号通道上的各个触发器级联式传播下去。对任何一种触发器,在时钟触发沿前后的一个小时间窗口内,输入信号必须稳定。这一时间窗口是多种因素的函数, 包括触发器设计、实现技术、运行环境以及无缓冲输岀上的负载等。输入信号陡峭的边沿可以将此窗口减至最小。随着时 钟频率的升高,会岀现更多有问题的时间窗口,而随着数据频率的提升,这种窗口的命中概率则会增加。FPGA制造商和IC晶片厂用“ MTBF来标识合格的触发器,并且确定它们的特性。“ MTBF (平均无故障时间)用统计方法描述了一个触发器的亚稳态特性,即确定某个触发器岀现故障的概率。在计算MTBF时,制造商部分基于输入信号改变导致触发器不稳定期间的时间窗口长度。另外,MTBF的计算还使用了输入信号的频率以及驱动触发器的时钟频率。在一个ASIC或FPGA库中,每种触发器都有时序要求,以帮助你确定容易出问题的窗口。建立时间” (S

4、etup time)是指在时钟沿到来之前,触发器输入信号必须保持稳定的时间。保持时间” (Hold time)则是指在时钟沿之后,信号必须保持稳定的时间。这些指标通常比较保守,以应对电源电压、工作温度、信号质量以及制造工艺等各种可能的差异。如果一个设 计满足了这些时序要求,则触发器岀现错误的可能性可以忽略不计。现代IC与FPGA设计中使用的综合工具可以保证设计能满足每个数字电路触发器对建立与保持时间的要求。然而, 异步信号却给软件提岀了难题。对新的时钟域来说,从其它时钟域传来的信号是异步的。大多数综合工具在判定异步信号 是否满足触发器时序要求时遇到了麻烦。因为它们不能确定触发器处于非稳态的时间,所以它们也就不能确定从一个触发 器通过组合逻辑到达下一个触发器的总延迟时间。所以,最好的办法是使用一些电路来减轻异步信号的影响。信号同步信号同步的目的是防止新时钟域中第一级触发器的亚稳态信号对下级逻辑造成影响。简单的同步器由两个触发器串联而成,中间没有其它组合电路。这种设计可以保证后面的触发器获得前一个触发器输岀时,前一个触发器已退岀了亚稳 态,并且输出已稳定。设计中要注意将两个触发器放得尽可能

《FPGA跨时钟域信号设计》由会员新**分享,可在线阅读,更多相关《FPGA跨时钟域信号设计》请在金锄头文库上搜索。

内部审计人员工作总结(4篇).doc

评三好学生关键事迹

企业人事规章制度大全

货运场管理制度

最好玩的国王作文(通用3篇).doc

智慧旅游可行性分析报告.docx

垃圾处理场施工组织方案.docx

植物调查报告.doc

正式文件书写格式

2023年《雷雨》第二课时教学片断评析 教案教学设计.doc

关于员工劳动合同合集6篇

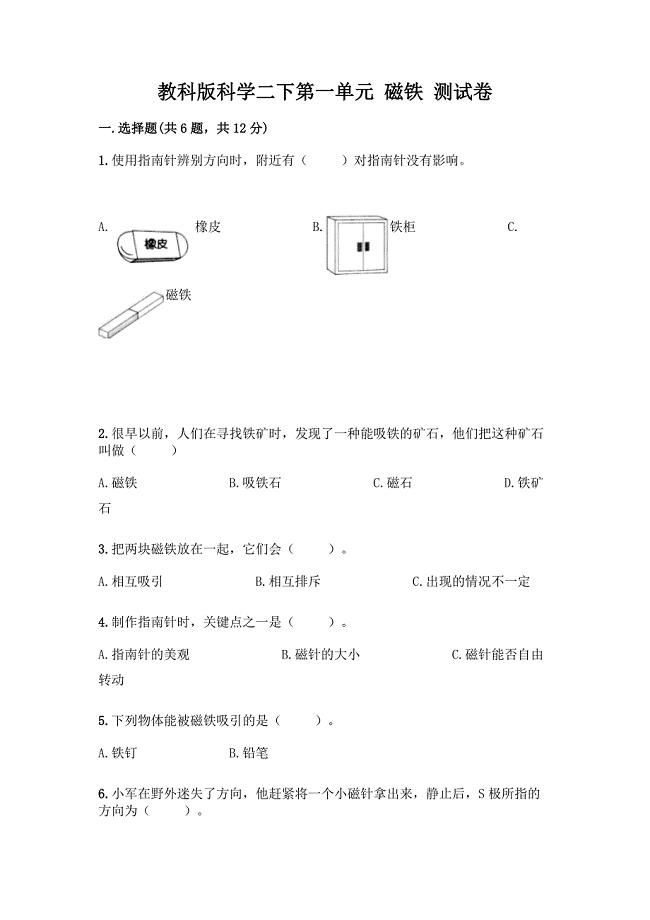

教科版科学二下第一单元-磁铁-测试卷-精品(A卷).docx

协会2023年工作总结4篇.doc

英语中表示颜色词语的特殊含义

出租车租车合同标准版(三篇).doc

学校房屋租赁合同通用版

理科考试试卷.doc

个人商品房装修协议书范文(九篇)

环保监理工作制度.doc

乘法交换律和乘法结合律.docx

2023年自愿转让协议(4份范本)

2023年自愿转让协议(4份范本)

2022-09-29 9页

初三化学第二学期教学计划范本(2篇).doc

初三化学第二学期教学计划范本(2篇).doc

2023-06-11 8页

幼儿园帮扶工作计划范文(2篇).doc

幼儿园帮扶工作计划范文(2篇).doc

2022-10-08 4页

浙江省瑞安市塘下镇新华中学八年级汗青与社会上册 第四单位 第二课 汉唐乱世第4课时教案 人教版合集

浙江省瑞安市塘下镇新华中学八年级汗青与社会上册 第四单位 第二课 汉唐乱世第4课时教案 人教版合集

2023-05-18 3页

秋思洇漫岁月的河流

秋思洇漫岁月的河流

2022-10-03 2页

《可以救命的一氧化碳》选择题答案

《可以救命的一氧化碳》选择题答案

2023-07-15 4页

2023医院护理的个人工作计划参考范本(三篇).doc

2023医院护理的个人工作计划参考范本(三篇).doc

2023-05-19 7页

今天的天气适合说情话

今天的天气适合说情话

2022-08-19 5页

2022寒假实践报告2000字

2022寒假实践报告2000字

2023-06-02 2页

【名校资料】【人教版】小学六年级数学下期中质量检测题

【名校资料】【人教版】小学六年级数学下期中质量检测题

2023-05-10 3页