计算机组成原理题(附答案)

21页1、计算机组成原理题解指南第一部分:简答题第一章 计算机系统概论1说明计算机系统的层次结构。计算机系统可分为: 微程序机器级, 一般机器级 (或称机器语言级) , 操作系统级, 汇编语言级, 高级语言级。第四章 主存储器1主存储器的性能指标有哪些?含义是什么?存储器的性能指标主要是存储容量. 存储时间、存储周期和存储器带宽。在一个存储器中可以容纳的存储单元总数通常称为该存储器的存储容量。存取时间又称存储访问时间,是指从启动一次存储器操作到完成该操作所经历的时间。存储周期是指连续两次独立的存储器操作(如连续两次读操作)所需间隔的最小时间。存储器带宽是指存储器在单位时间中的数据传输速率。2. DRA防储器为什么要刷新?DRA防储器采用何种方式刷新?有哪几种常用的刷新方式?DRA防储元是通过栅极电容存储电荷来暂存信息。由于存储的信息电荷终究是有泄漏的,电荷数又不能 像SRA所储元那样由电源经负载管来补充,时间一长,信息就会丢失。为此必须设法由外界按一定规律给栅 极充电,按需要补给栅极电容的信息电荷,此过程叫“刷新” 。DRAMI用读出方式进行刷新。因为读出过程中恢复了存储单元的MO跚极电容电荷,

2、并保持原单元的内容,所以读出过程就是再生过程。常用的刷新方式由三种:集中式、分散式、异步式。3什么是闪速存储器?它有哪些特点?闪速存储器是高密度、非易失性的读/写半导体存储器。从原理上看,它属于ROMS存储器,但是它又可随机改写信息;从功能上看,它又相当于RAM所以传统ROMf RAM勺定义和划分已失去意义。因而它是一 种全新的存储器技术。闪速存储器的特点: ( 1)固有的非易失性,( 2 )廉价的高密度,( 3)可直接执行,( 4)固态性能。4.请说明SRAM勺组成结构,与 SRAM1比,DRAMfc电路组成上有什么不同之处?SRAM储器由存储体、读写电路、地址译码电路、控制电路组成,DRAME需要有动态刷新电路。第五章 指令系统1在寄存器寄存器型,寄存器存储器型和存储器存储器型三类指令中,哪类指令的执行时间最长?哪类指令的执行时间最短?为什么?寄存器 - 寄存器型执行速度最快, 存储器 - 存储器型执行速度最慢。 因为前者操作数在寄存器中, 后者操作数在存储器中,而访问一次存储器所需的时间一般比访问一次寄存器所需时间长。2一个较完整的指令系统应包括哪几类指令?包括:数据传送指令、算

3、术运算指令、逻辑运算指令、程序控制指令、输入输出指令、堆栈指令、字符串指令、特权指令等。3什么叫指令?什么叫指令系统?指令就是要计算机执行某种操作的命令一台计算机中所有机器指令的集合,称为这台计算机的指令系统。第六章 中央处理部件CPU1指令和数据均存放在内存中,计算机如何从时间和空间上区分它们是指令还是数据。时间上讲,取指令事件发生在“取指周期” ,取数据事件发生在“执行周期” 。从空间上讲,从内存读出 的指令流流向控制器(指令寄存器) 。从内存读出的数据流流向运算器(通用寄存器) 。 2.简述CPU的主要功能。CPU主要有以下四方面的功能:(1)指令控制程序的顺序控制,称为指令控制。(2) 操作控制CPU管理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应部件,从而控制这些部件按指令的要求进行动作。(3) 时间控制对各种操作实施时间上的控制,称为时间控制。(4) 数据加工对数据进行算术运算和逻辑运算处理,完成数据的加工处理。3.举出CPU中6个主要寄存器的名称及功能。CPU有以下寄存器:(1)指令寄存器(IR):用来保存当前正在执行的一条指令。(2) 程序计数器(PC)

4、 :用来确定下一条指令的地址。(3)地址寄存器(AR):用来保存当前CPU/f访问的内存单元的地址。(4) 缓冲寄存器(DR) :作为CPUffi内存、外部设备之间信息传送的中转站。 补偿CPUffi内存、外围设备之间在操作速度上的差别。 在单累加器结构的运算器中,缓冲寄存器还可兼作为操作数寄存器。(5)通用寄存器(AQ:当运算器的算术逻辑单元(ALU执行全部算术和逻辑运算时,为ALU提供一个工作区。(6) 状态条件寄存器:保存由算术指令和逻辑指令运行或测试的结果建立的各种条件码内容。除此之外,还保存中断和系统工作状态等信息,以便使CPUffi系统能及时了解机器运行状态和程序运行状态。4比较水平微指令与垂直微指令的优缺点。(1) 水平型微指令并行操作能力强、效率高、灵活性强,垂直型微指令则较差。(2) 水平型微指令执行一条指令的时间短,垂直型微指令执行时间长。(3) 由水平型微指令解释指令的微程序, 具有微指令字比较长, 但微程序短的特点, 而垂直型微指令正好相反。(4) 水平型微指令用户难以掌握,而垂直型微指令与指令比较相似,相对来说比较容易掌握5什么是指令周期?什么是机器周期?什么

《计算机组成原理题(附答案)》由会员公****分享,可在线阅读,更多相关《计算机组成原理题(附答案)》请在金锄头文库上搜索。

幼儿园老师个人进修计划模板(二篇).doc

平凡的世界读后感

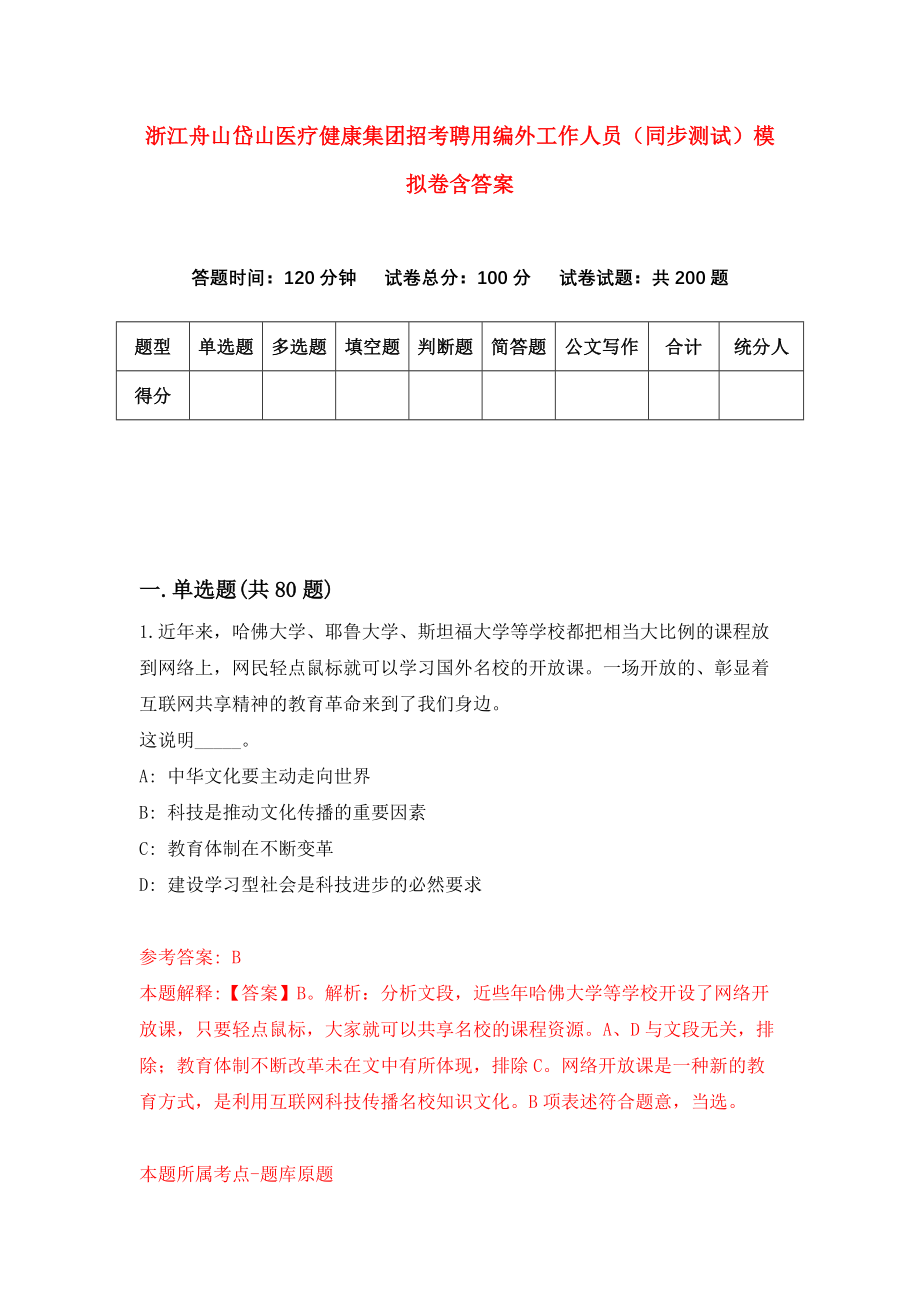

浙江舟山岱山医疗健康集团招考聘用编外工作人员(同步测试)模拟卷含答案(5)

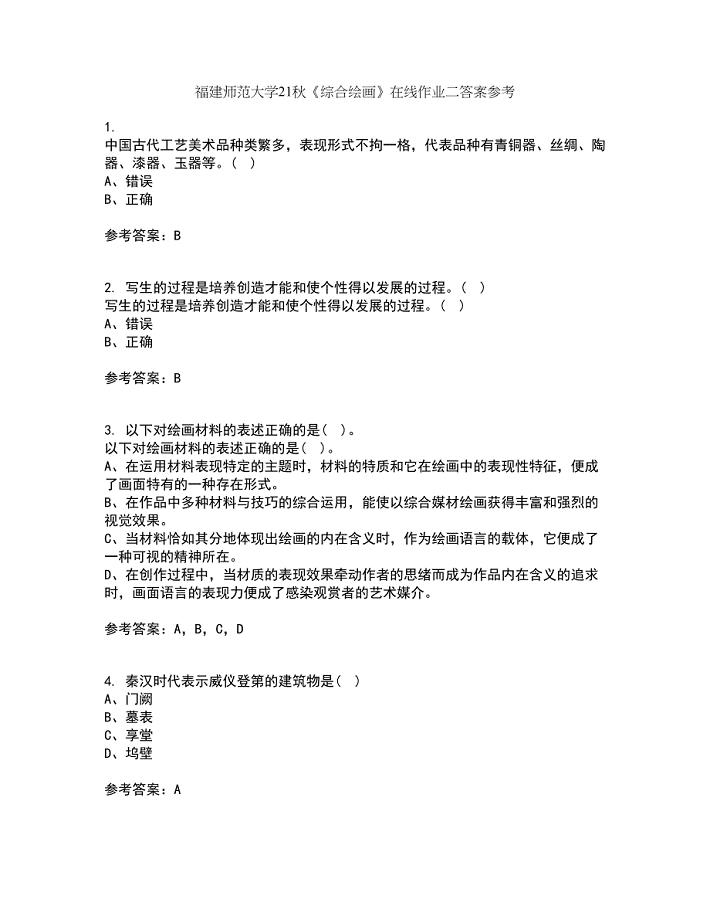

福建师范大学21秋《综合绘画》在线作业二答案参考11

专题讲座资料(2021-2022年)工程技术研究中心总结汇报

谈初中数学创新思维的培养

农业综合开发办公室工作总结

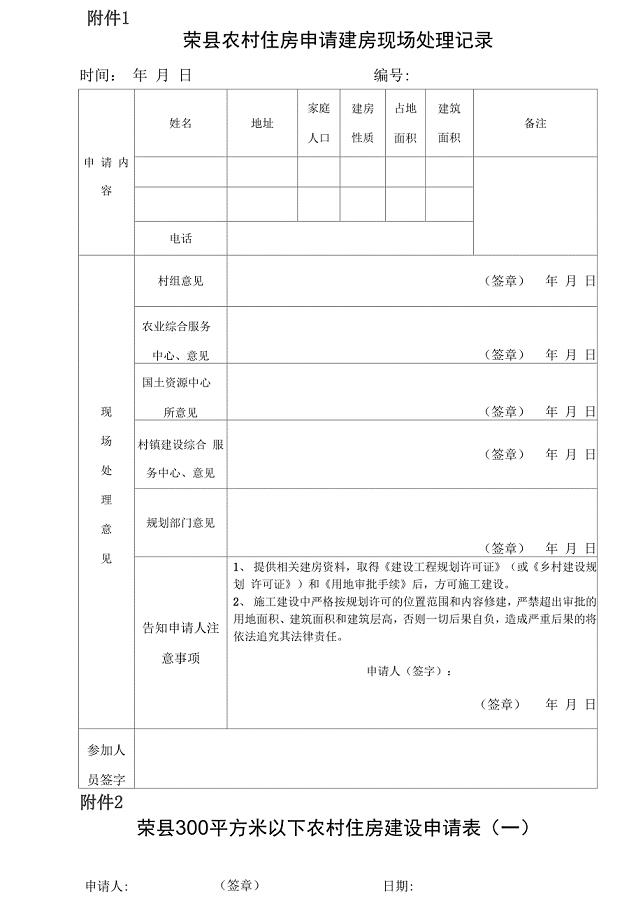

农村宅基地批准书

医疗器械经营管理制度

计算机网络实验报告

基础护理学练习试卷1

居民自治各项新版制度

双十一活动策划5篇

游泳池臭氧消毒

2022年乒乓球社团活动工作总结

佳能尼康数码相机镜头标识的含义

教师跟岗学习心得体会_教师跟岗学习心得

大型商场闭路电视监控系统

2023年医生个人总结模板(4篇).doc

企业承诺书4

大面积脑梗死流程.doc

大面积脑梗死流程.doc

2023-09-28 1页

2020年全国卷英语答题卡

2020年全国卷英语答题卡

2023-09-28 2页

基层反映做好基层社会治理工作的几点建议

基层反映做好基层社会治理工作的几点建议

2023-04-06 7页

企业文化建设实施方案(经典)

企业文化建设实施方案(经典)

2023-06-22 16页

党建工作年终述职报告范文.doc

党建工作年终述职报告范文.doc

2023-07-20 4页

煤矿掘进工程质量验收制度

煤矿掘进工程质量验收制度

2023-12-07 6页

吊车吊装计算

吊车吊装计算

2023-11-24 11页

公司安全管理制度(完整版)

公司安全管理制度(完整版)

2024-01-12 7页

广州市新版信息技术四年级下册教学设计.doc

广州市新版信息技术四年级下册教学设计.doc

2023-09-22 20页

中国通信管道行业发展研究报告.docx

中国通信管道行业发展研究报告.docx

2023-06-25 10页