实验一组合逻辑电路的设计

8页1、实验一 组合逻辑电路的设计一、实验目的:1、 掌握组合逻辑电路的设计方法。2、 掌握组合逻辑电路的静态测试方法。3、 加深FPGA设计的过程,并比较原理图输入和文本输入的优劣。4、 理解“毛刺”产生的原因及如何消除其影响。5、 理解组合逻辑电路的特点。二、实验的硬件要求:1、 EDA/SOPC实验箱。2、 计算机。三、实验原理1、组合逻辑电路的定义数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。通常组合逻辑电路可以用图1.1所示结构来描述。其中,X0、X1、Xn 为输入信号, L0、L1、Lm为输出信号。输入和输出之间的逻辑函数关系可用式1.1表示:组合逻辑电路X0XnL0Lm图 1.1 组合逻辑电路框图L0=F0(X0,X1,Xn)Lm=F0(X0,X1,Xn)(1.1)2、组合逻辑电路的设计方法组合逻辑电路的设计任务是根据给定的逻辑功能,求

2、出可实现该逻辑功能的最合理组 合电路。理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求;(2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表,建立起逻辑模型;然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。组合电路的基本设计步骤可用图1.2来表示。图 1.2 组合电路设计步骤示意图图3、组合逻辑电路的特点及设计时的注意事项组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。(实际电路中还要考虑器件和导线产生的延时)。组合逻辑电路设计时应尽量避免直接或间接的反馈,以免出现不确定的状态或形成振荡。如右图设计的基本触发器,当输入S、R从“00”变为“11”时,无法确定Q和Q的值。组合逻辑电路容易出现“毛刺”,这是由于电路“竞争冒险”产生的。如图1

3、.3所示,图中与门的两个输入分别由信号 A 经过不同路径传递而来。按照理想情况分析,电路输出端应该始终为 L=A A =0。考虑到信号在逻辑门中的传输延迟,A 到达与门输入端的时间始终落后于 A。图 3.2-1(b)的波形显示,信号 A的四次变化都产生了竞争。但这四次竞争引起的结果是不一样的。第一次和第三次竞争造 成输出错误,第二次和第四次竞争则没有造成输出错误。换言之,只有第一次和第三次竞争引起了冒险,产生了尖峰干扰。图 1.3 竞争冒险实例由于“毛刺”的影响,应避免使用组合逻辑电路直接产生时钟信号,也应避免将组合逻辑电路的输出作为另一个电路的异步控制信号。如右图,本意是设计一个计数范围为“05”的六进制计数器,即输出QD、QC、QB、QA从5“0101”变到6“0110”时,与门输出“1”,控制“CLR”异步复位到“0000”,但是由于输出从3“0011”变到4“0100”时,QC先于QB从“0”变到“1”,导致短暂的“0111”出现,使与门输出“1”,引起复位,从而使实际的电路计数范围为“03”,与设计的初衷相悖。用VHDL描述组合逻辑电路时,所有的输入信号都应放在敏感信号表中。

《实验一组合逻辑电路的设计》由会员m****分享,可在线阅读,更多相关《实验一组合逻辑电路的设计》请在金锄头文库上搜索。

班主任的个人述职报告范文集锦6篇

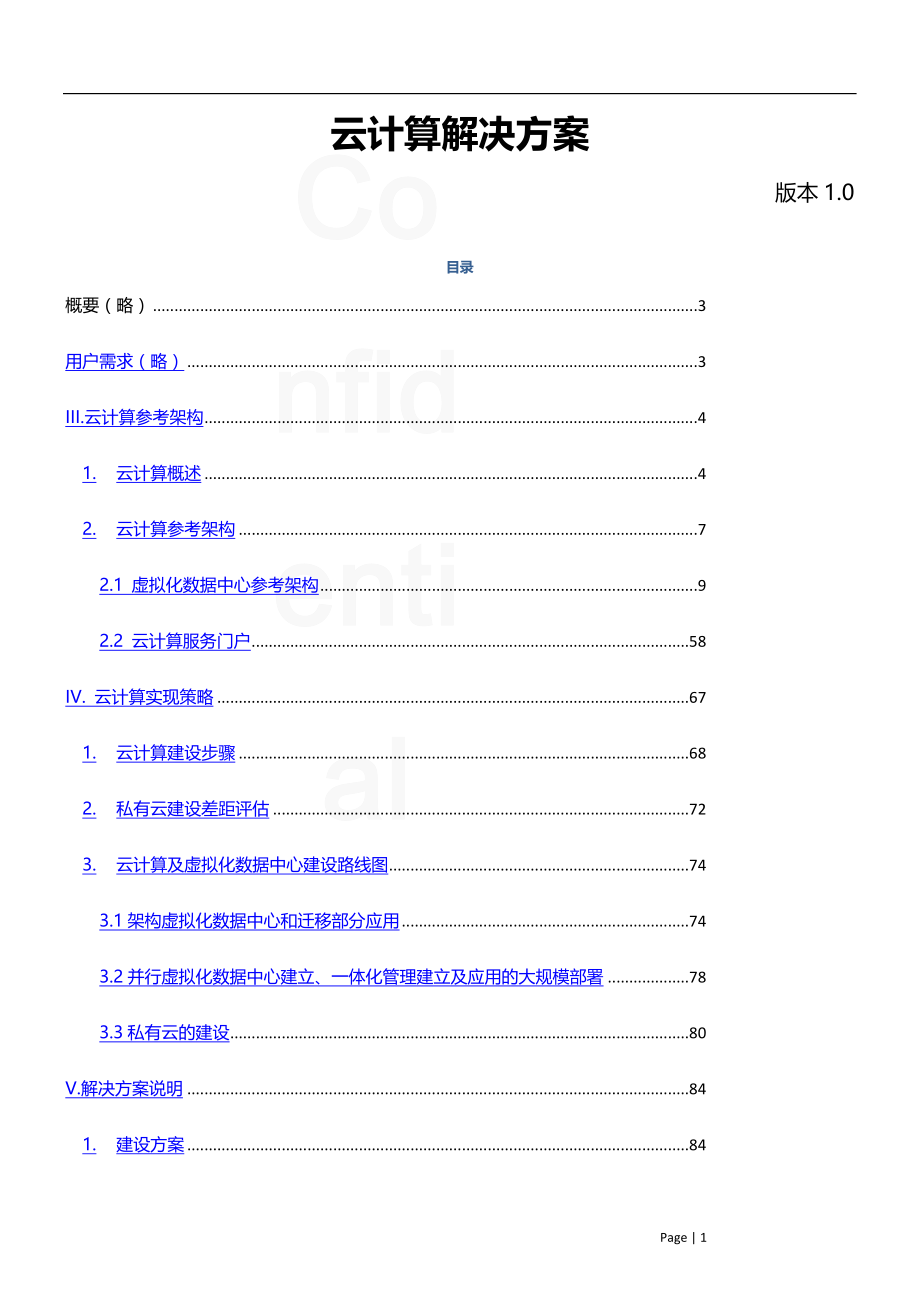

云计算平台建设方案模板

措洼水电站引水隧洞开挖支护技术交底

DZW646014625A型锅炉的设计与计算

中级银行从业资格考试《个人理财》考试历年真题汇编(精选)含答案56

阳泉洗碗机研发项目申请报告

繁荣寄宿制小学减负增质的具体措施

消防慰问信

金地集团实测实量指引(共63页)

幼儿园中班美术活动:烂漫的樱花

电动门调试作业指导书

幼儿园保教工作计划范文

上海市工程建设规范建设工程绿色施工节约型工地管理规范

教师师德师风建设总结范本(二篇).doc

我的好朋友400字

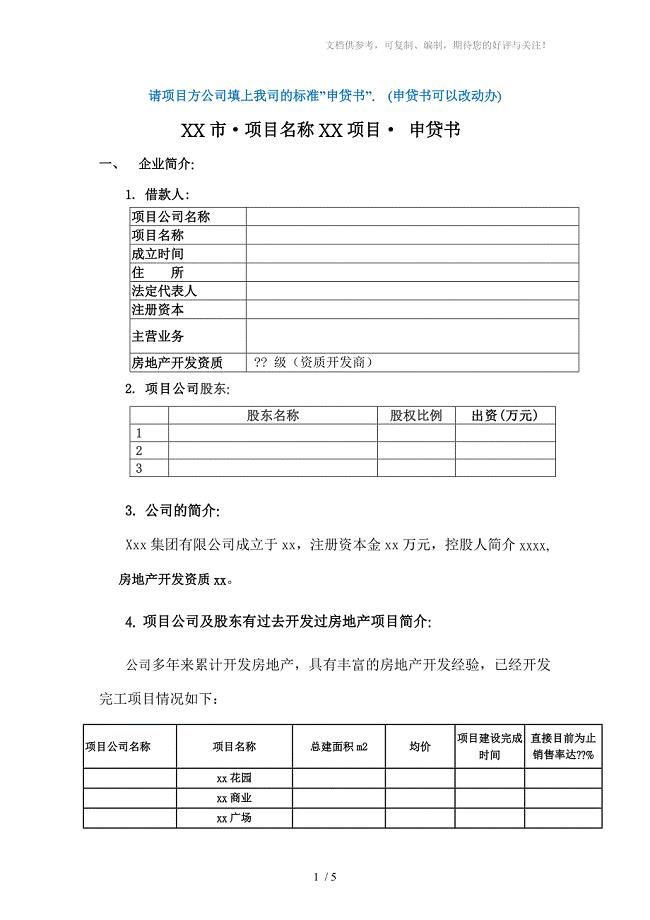

房地产-填上标准,申贷书(已有房产)

皮卡租赁合同范本

大一新生英语的自我介绍

计算商末尾有0且有余数的除法

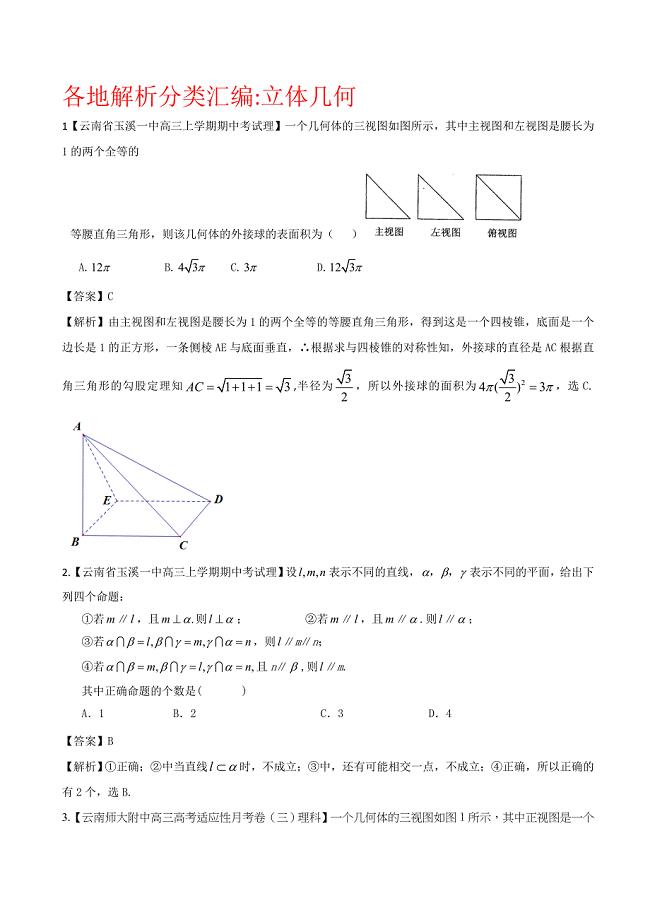

最新各地名校试题解析分类汇编一理科数学:7立体几何

三焦不通老病缠身!教你打通三焦的简单方法

三焦不通老病缠身!教你打通三焦的简单方法

2023-04-27 4页

叶2017年廉村镇扶贫通村公路建设项目

叶2017年廉村镇扶贫通村公路建设项目

2024-02-27 31页

【建筑施工方案】扣件式钢管外架施工方案

【建筑施工方案】扣件式钢管外架施工方案

2023-02-18 20页

电池电量检测方法

电池电量检测方法

2023-07-27 4页

【整理版施工方案】绿化工程冬季施工方案

【整理版施工方案】绿化工程冬季施工方案

2023-02-01 15页

中央空调多联机施工方案

中央空调多联机施工方案

2023-11-10 16页

宜家的一些资料

宜家的一些资料

2024-01-14 5页

主体结构工程施工方案培训课件

主体结构工程施工方案培训课件

2023-03-02 33页

《麦肯锡问题分析与解决技巧》精读

《麦肯锡问题分析与解决技巧》精读

2022-08-15 40页

中山林业宣传片拍摄方案

中山林业宣传片拍摄方案

2022-09-21 9页