74LS153译码器组合逻辑电路设计案例分析

3页1、74LS153译码器组合逻辑电路设计案例分析1、逻辑电路:D3、D2、DI、DO为数据输入端,Al、A0为地址信号输入端, Y为数据输出端,ST为使能端,又称选通端,输入低电平有效。下图7.10 为74LS153管脚排列示意图。该芯片中存在两个4选1数据选择器。6531C01C11C21C31Y7102 2 2 2 C C C C3 2 102Y14-2AB1-015 口1G2G图7.10 74LS153 管脚排列表7.5为74LS153的功能表。输入输出使能 端GABC3C2C1C0Y1XXXXXX0000XXX00C0000XXX11001XX0X0C1001XX1X1010X0XX0C2010X1XX10110XXX0C30111XXX1当使能端G有效时,输出等于地址信号A、B所选择的数据信号。可得输出函数表达式 为.Y 二 m C + mC + m C + mC。o0112 233对于一个n选1的数据选择器,其输出函数为:Y = mC + . + mCo 0nn二、用数据选择器实现组合逻辑函数实现原理:数据选择器是一个逻辑函数的最小项输出:Y 二 m C + . + m C =

2、尹一 m co 0 n n 0 ii = 0而任何一个n位变量的逻辑函数都可变换为最小项之和的标准式。对照函数表达式和相应的数据选择器输出函数表达式,可以实现用数据选择器来表示逻辑函数。实现步骤:(1) 根据函数变量选择合适的数据选择器,一般变量个数n个,选择2n选1的数据选择 器。(2) 将被表示的函数转换成标准与或表达式。(3) 写出选择的数据选择器的输出函数。(4) 对比两函数,使数据选择器的地址端和函数变量一一对应(高位对高位),表达式中 出现的最小项相应的输入数据C为1,否则为0。(5) 画逻辑电路图。例:用数据选择器和门电路实现Y = AB + AC的组合逻辑电路。(1) 选择数据选择器:选8选1数据选择器74LS151。(2) 标准与或表达式Y = AB + AC = ABC + ABC + ABC = m + m + m657(3) 写出数据选择器输出函数Y 二 m C + m C + m C + m C + m C + m C + m C + m Co 01 12 23 34 45 56 67 7(4) 对照上述两表达式,令 A=A2,B=A1,C=A0,则 m 二 m,所以,C0=G=C2=C3=C4=0;nn01234C5=C6=C7=1。(5) 画逻辑电路,如图 7.11 所示。v图 7.11 逻辑电路图

《74LS153译码器组合逻辑电路设计案例分析》由会员cn****1分享,可在线阅读,更多相关《74LS153译码器组合逻辑电路设计案例分析》请在金锄头文库上搜索。

2023年民办非企业单位登记

大连理工大学21春《商法》在线作业三满分答案98

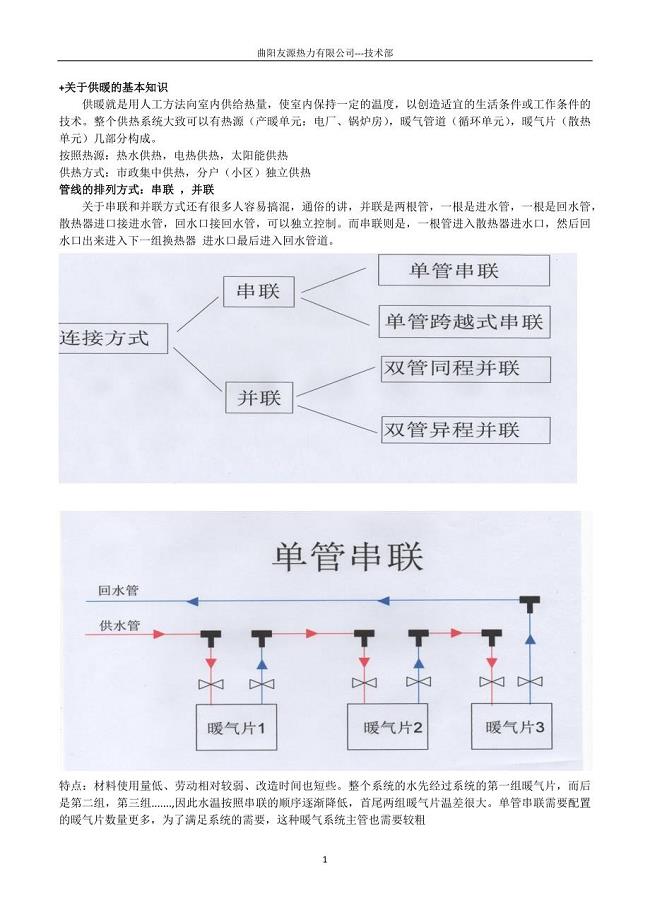

暖气片的连接方式

幼儿园健康优秀教案:繁忙的马路.doc

银川关于成立石英产品公司可行性研究报告

县统计局XX年度预防职务犯罪工作总结.docx

小学学校晨检制度范文(四篇).doc

苦儿流浪记读后感范文.doc

下齿槽神经阻滞麻醉第三个注射点创立与应用

2023年xx医德医风学习心得新编.docx

离婚补充协议书简单版(9篇)

危害分析和关键控制点(HACCP)体系及其应用准则

2023年青春励志教师演讲稿.docx

中考必背的30篇英语作文之一

2023庆元旦迎新年红领巾广播稿范文.docx

2023年公司财务个人述职报告.docx

2023年牧区饲草料种植现场观摩会致辞.docx

银行暑期社会实习报告

“公司个人计划”个人工作计划范本(二篇).doc

出口退税流程148479201

重大灾害事故的心理救援

重大灾害事故的心理救援

2024-01-10 6页

红绿灯模型

红绿灯模型

2023-03-18 2页

陈设设计在室内空间中的应用

陈设设计在室内空间中的应用

2022-11-25 22页

肺腺癌术后中药调理厉害的中医在哪里

肺腺癌术后中药调理厉害的中医在哪里

2023-08-19 1页

铁路重力式挡土墙检验批样表

铁路重力式挡土墙检验批样表

2023-12-24 13页

《流域综合开发与可持续发展

《流域综合开发与可持续发展

2022-07-28 7页

聚类算法比较

聚类算法比较

2022-12-22 9页

IGBT模块的故障与驱动电路的关系

IGBT模块的故障与驱动电路的关系

2023-04-03 10页

蓄电池基本常识100问(1-20)

蓄电池基本常识100问(1-20)

2023-09-12 3页

销售人员服务理念

销售人员服务理念

2023-06-17 1页