数字电路应用实验指导书

40页1、数字电路应用实验指导书上海大学机电一体化工程中心2015年12月目 录一、 概述二、 实验一 比较器三、 实验二 码制转换器四、 实验三 加法器五、 实验四 优先编码器六、 实验五 七段译码器七、 实验六 计数器八、 实验七 移位寄存器九、 实验八 综合实验十、 附录A开发套件核心板ETL-005介绍十一、 附录B ETL-005管脚位置约束十二、 附录C QuartusII软件介绍一、 前言数字电路应用课是数字电路A的后续课程,本书是数字电路应用课的配套实验指导书。主要内容集中在用集成电路和Verilog语言进行时序逻辑电路设计,实验内容与数字电路A的实验内容对应,实验旨在使学生学会用硬件设计语言Verilog进行数字逻辑电路中常用逻辑功能模块的设计,大规模集成电路FPGA/CPLD的开发过程,实验内容与数字电路A的实验相对应,学习用不同方法设计数字逻辑功能电路、解决简单的实际工程问题的基本技能。 本指导书的实验使用的装置为“易上手”系列FPGA开发套件和微型计算机组成的数字电路实验系统。在FPGA/CPLD的实验中,培养学生学习和掌握Verilog语言,以及它的开发环境Quartu

2、sII的操作过程。与数字电路A的内容相对应,数字电路应用课的实验最终也要构成如下图所示的颗粒灌装系统: 其工作原理和流程如下:(1)通过拨码开关设置每瓶要装糖果的个数(两位十进制),通过编码器转换为BCD码,存入到寄存器中,寄存器的值可以通过一个译码器显示在七段数码管1上;(2)灌装的颗粒通过灌装装置上的漏斗落入下面传送带上的瓶中,漏斗上装有检测颗粒下落的光电传感器,每下落一个糖果,传感器发送一个脉冲,控制系统中的计数器对该脉冲进行计数,计数的结果与预置的每瓶灌装的颗粒数进行比较, 比较可以使用二进制或者BCD码,如果比较器两个输入的码制不同,需事先进行码制转换(将BCD转为二进制或者二进制转为BCD码);比较结果相等则使计数器停止计数,同时该信号控制关闭漏斗开关,停止颗粒下落,启动传送带换瓶等待下一次灌装。系统中加法器负责统计当前灌装总量,其数值送入寄存器寄存,寄存器的值可以通过码制转换和译码器显示在七段数码管2上。(3)新瓶到位也由光电传感器检测,检测到瓶子以后,停止传送带移动,将计数器清零后启动计数器准备新一轮计数,打开漏斗开关进行新的灌装。系统重复执行步骤(2)过程。同数字电路

3、A,本课程的实验仍采用分别设计系统中的功能模块,最终综合拼接的方法。开发套件核心板ETL-005的简单说明和各芯片管脚约束见附件A和B。实验一 比较器实验目的 (1) 熟悉Verilog语言的基本结构,了解基本运算符和赋值(2) 熟悉QuartusII的开发环境建立,以及仿真过程(3) 学会用Verilog语言实现组合逻辑电路的方法(4) 用Verilog语言设计组合逻辑电路的比较器实验内容编写设计比较器的Verilog代码并仿真实验步骤和要求设计比较器,如下图所示:设计一个八位数比较器,输入为糖果计数器输出信号counter3:0和寄存器信号binReg3:0,输出信号bEQU为数据相等信号,输出信号bBig为counter数据大于binReg数据信号,输出信号bSmall为counter数据小于binReg数据信号。具体功能要求如下:两个输入数据为相等时,相等信号bEQU输出为1,否则输出为0; counter数据大于binReg数据时,输出信号bBig为1,否则为0;counter数据小于binReg数据信号时输出信号bSmall为1,否则为0。电路管脚与信号定义如下:信号连接器

《数字电路应用实验指导书》由会员m****分享,可在线阅读,更多相关《数字电路应用实验指导书》请在金锄头文库上搜索。

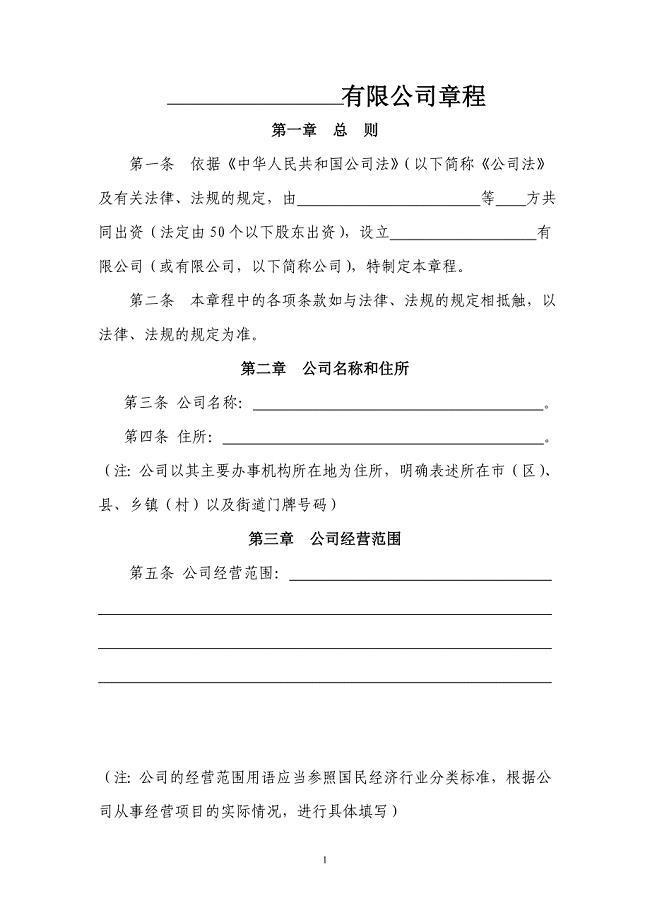

高新区-最新公司章程多人章程.doc

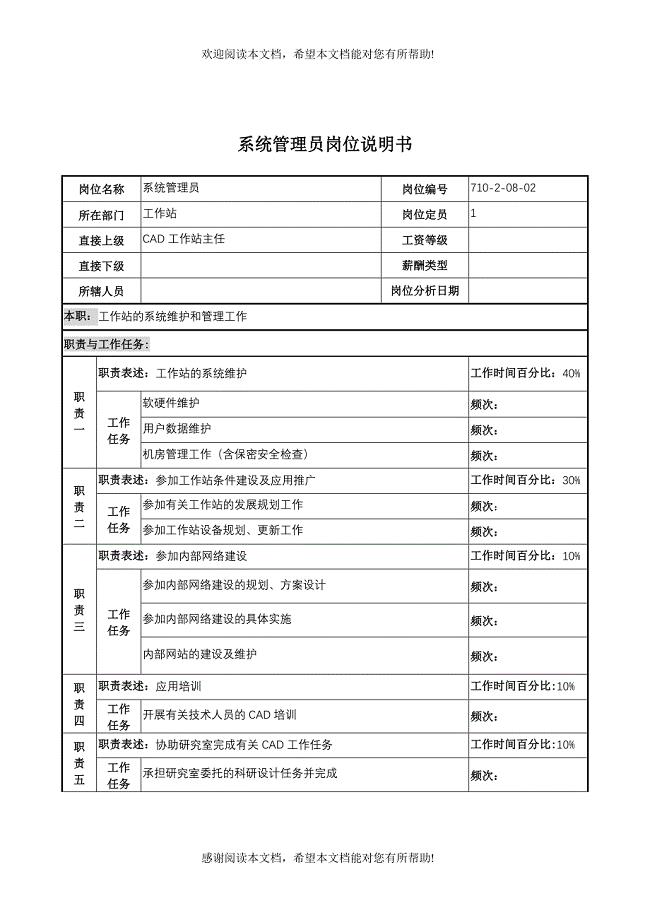

XX重工研究所CAD工作站系统管理员岗位说明书

2023年上半年个人述职报告.docx

2023年家长学校学学工作计划.docx

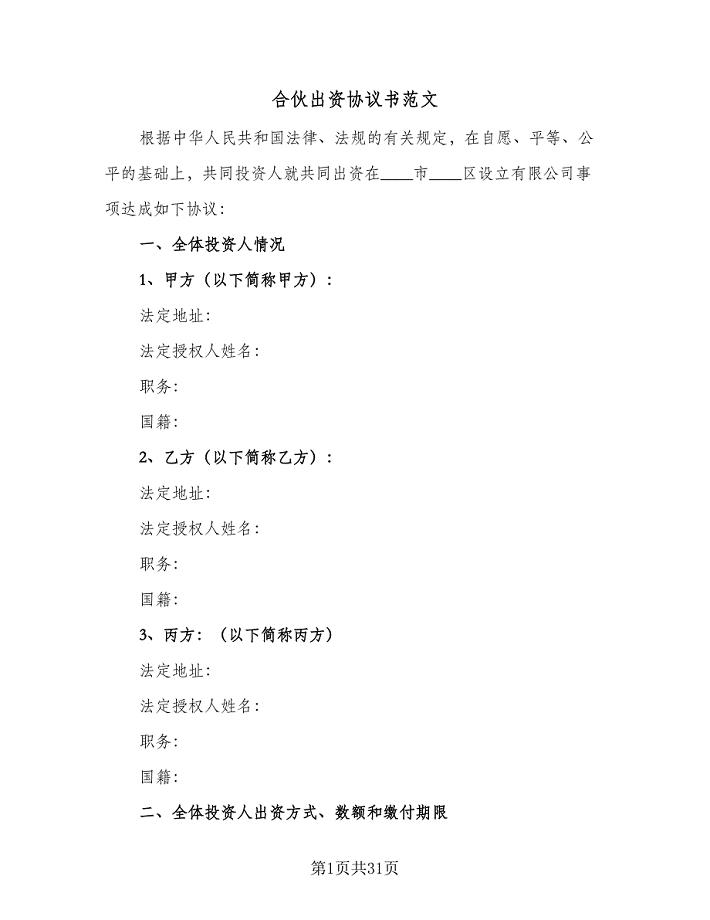

合伙出资协议书范文(九篇)

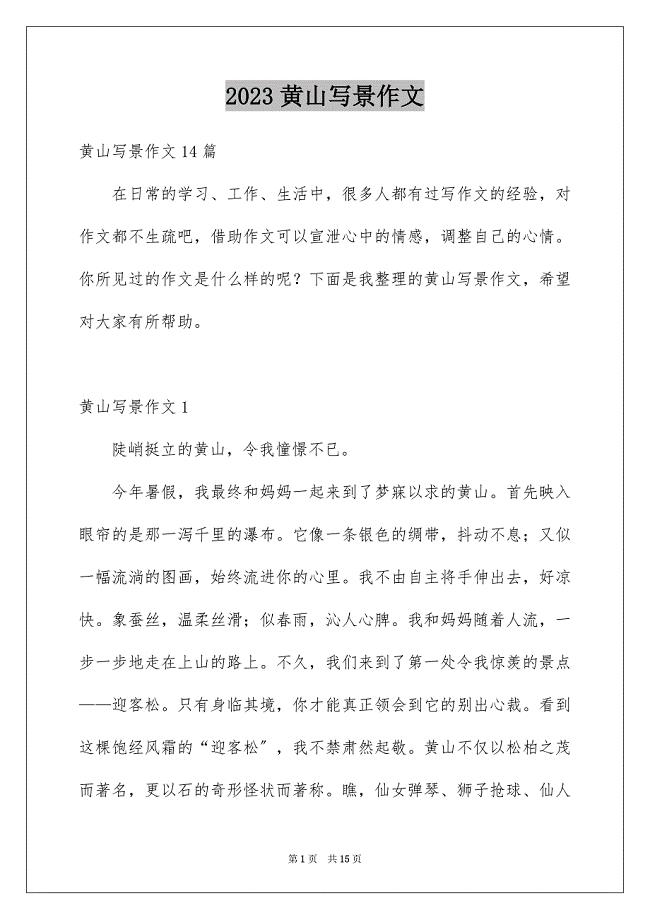

2023黄山写景作文8范文.docx

张家口关于成立反光材料技术服务公司可行性报告_模板范本

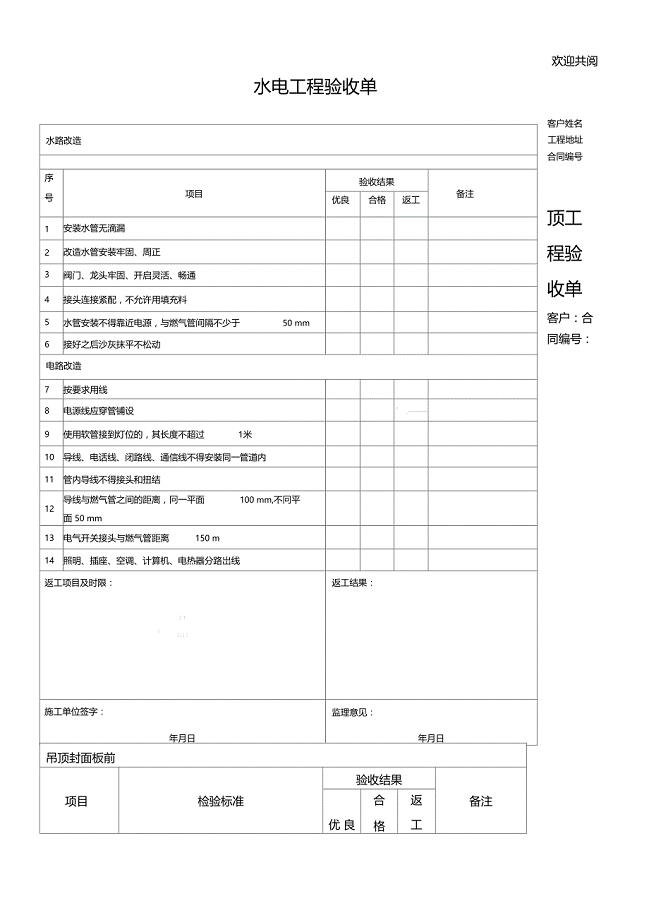

装饰公司验收表格模板格

2023年班主任工作班级小组建设的反思.docx

2023年办公室工作总结乡镇规划办公室工作总结范文.docx

2023年乡镇全年计生工作总结汇报.docx

企管部2023年度工作计划(4篇)

2023年妈妈我爱您作文1.docx

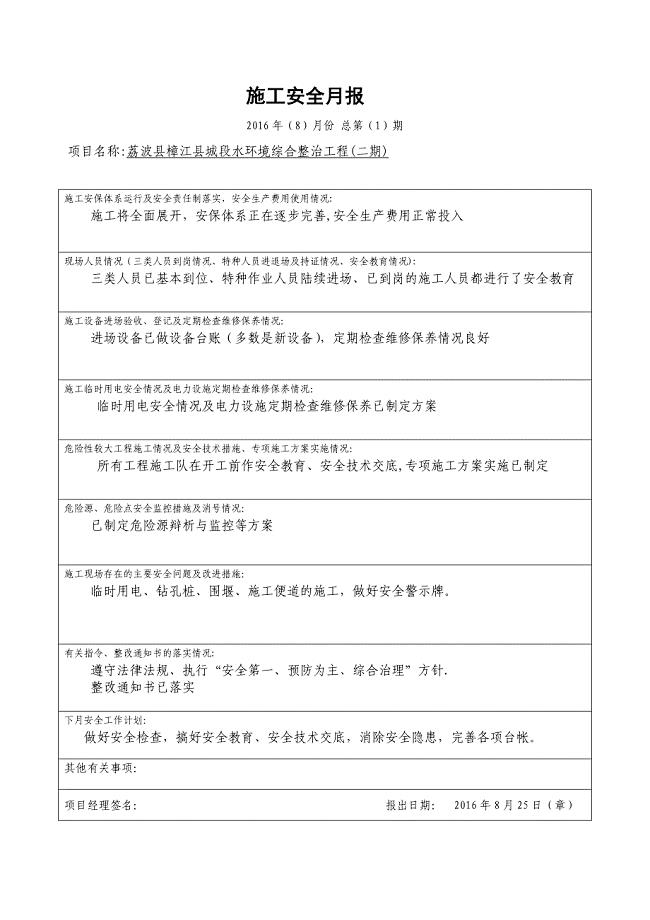

施工安全月报-----------AQ.doc

装饰公司章程范本最新

学校捐款倡议书范文3篇.doc

对两学一做常态化实践与思考.docx

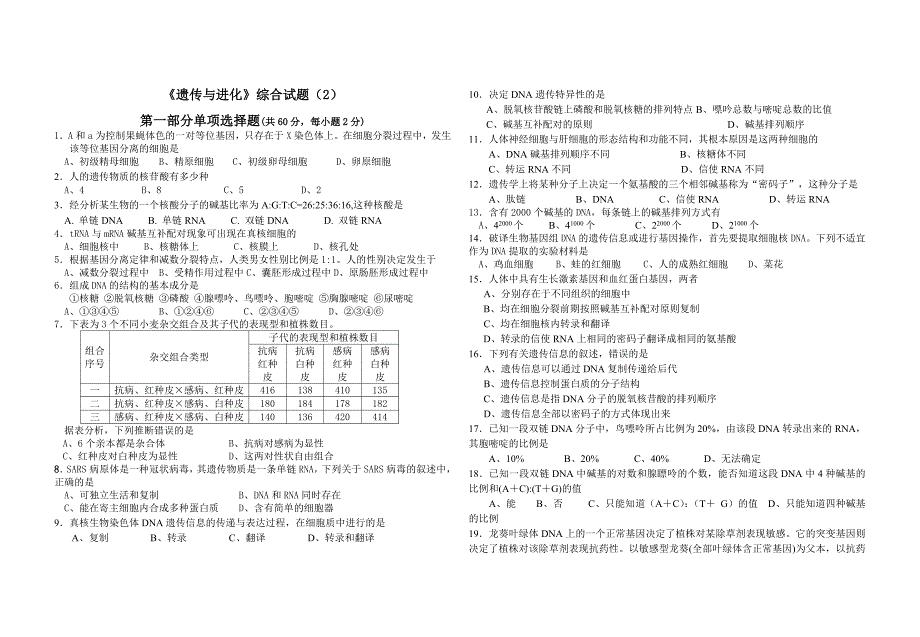

进化遗传与综合试题2

2023年竞税务处主任演讲 (2).DOCX

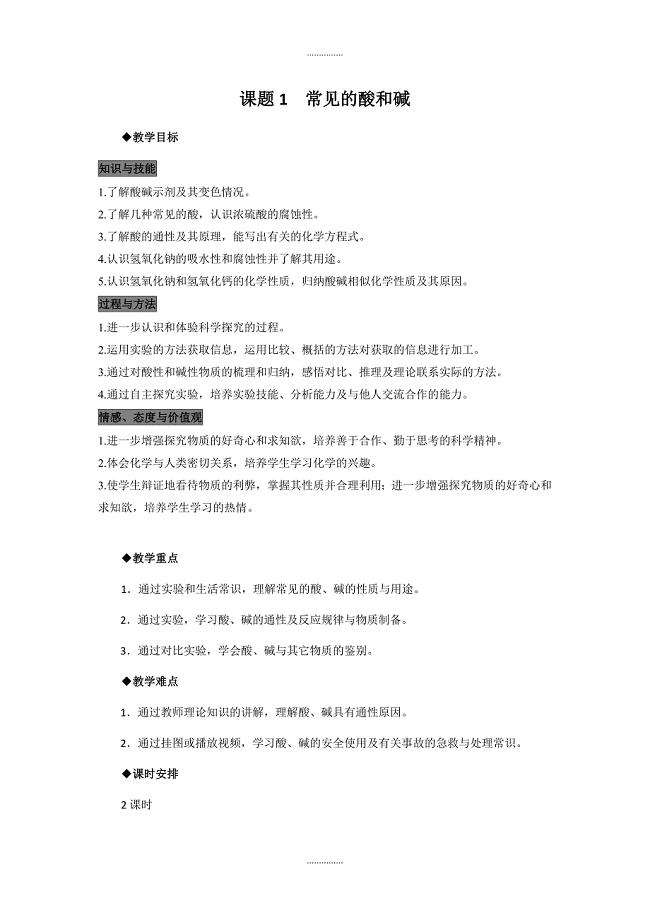

新人教版九年级下册化学:全册精品示范教案 第十单元 酸和碱课题1常见的酸和碱

竞聘统计核算员的演讲稿.doc

竞聘统计核算员的演讲稿.doc

2023-06-25 3页

三角函数高考试题精选(含详细答案)-

三角函数高考试题精选(含详细答案)-

2022-10-29 20页

上市公司戴帽摘帽条件

上市公司戴帽摘帽条件

2023-01-29 4页

生育登记服务表(新)

生育登记服务表(新)

2023-07-16 3页

党建联系点工作开展情况总结 --

党建联系点工作开展情况总结 --

2023-03-12 3页

电大中级财务会计二形成性考核册答案

电大中级财务会计二形成性考核册答案

2023-03-06 12页

SG-Y3停车场计费管理系统实验实训装置

SG-Y3停车场计费管理系统实验实训装置

2024-01-23 3页

公务员考试录用工作总结

公务员考试录用工作总结

2023-06-17 5页

学校(幼儿园)卫生管理工作台账(一)

学校(幼儿园)卫生管理工作台账(一)

2023-12-25 32页

个人外汇题库

个人外汇题库

2023-01-28 19页