基于FPGA等精度频率计设计

45页1、摘 要本文设计的等精度频率计,主要硬件电路由复杂可编程逻辑(FPGA)和单片机AT89C51构成。FPGA完成各种时序逻辑控制、计数功能;单片机AT89C51作为系统的主控部件,实现整个电路的测试信号控制、数据运算处理、键盘扫描和控制数码管的显示输出。将单片机AT89C51的控制灵活性及FPGA芯片的可编程性相结合,采用十进制数字显示,实现了测量信号的频率、周期等基本功能。关键词:等精度频率计;可编程逻辑器件;VHDL;单片机AT89C51. / 文档可自由编辑打印AbstractThis paper introduces a method to design precision frequency meter based on equal precision measuring principle. The main circuit is composed of complex programmable logic (FPGA) and AT89C51. The complex programmable logic device completes sequential logic

2、control, and the counting function. AT89C51 works as the chief controller, which controls test signals of whole circuit, proceses data, scans keyboard and controls digital to display. The system combines the flexibility of AT89C51 and programmable chip FPDA, displays with decimal figures. Keywords:Equal precision frequency meters;FPGA;VHDL;MCU目 录引 言71概 述81.1等精度频计的简介和意义81.2FPGA的简介81.2.1可编程逻辑器件FPGA的基本结构81.2.2FPGA的设计方法与要求91.2.4FPGA设计工具102 .等精度频计的原理分析112.1 等精度频计的原理113. 硬件电路设计133.1总体方案设计133.2测频模块的工作原

3、理及设计143.2.1 FPGA测频专用模块逻辑设计143.2.2测频/测周期的实现153.2.3控制部件设计163.2.4计数部件设计163.2.5脉冲宽度测量和占空比测量模块设计163.3单片机主控模块173.3.1 AT89C51单片机性能173.3.2单片机控制电路193.4外围电路设计203.4.1键盘接口电路203.4.2显示电路204.软件设计224.1本系统FPGA模块的顶层设计224.2 FPGA模块仿真224.3单片机的汇编语言编程234.3.1单片机主程序234.3.3键盘扫描、时间值输入及计数值计算子程序245.附录256.附图457.结束语468.致 谢47参考文献48引 言在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。数字式频率计的测量原理有两类:一是直接测频法,即在一定闸门时间内测量被测信号的脉冲个数;二是间接测频法即测周期法,如周期测频法。直

4、接测频法适用于高频信号的频率测量,通常采用计数器、数据锁存器及控制电路实现,并通过改变计数器阀门的时间长短在达到不同的测量精度;间接测频法适用于低频信号的频率测量,本设计中使用的就是直接测频法,即用计数器在计算1S内输入信号周期的个数。数字频率计是数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。 采用FPGA现场可编程门阵列为控制核心,通过硬件描述语言VHDL编程,在QuartusII仿真平台上编译、仿真、调试 ,并下载到FPGA芯片上,通过严格的测试后,能够较准确地测量方波、正弦波、三角波、矩齿波等各种常用的信号的频率,而且还能对其他多种物理量进行测量。1概 述1.1 等精度频计的简介和意义频率检测是电子测量领域的最基本也是最重要的测量之一, 频率信号抗干扰强,易于传输, 可以获得较高的测量精度, 所以测频率方法的研究越来越受到重视, 本设计是基于FPGA等精度率数字

《基于FPGA等精度频率计设计》由会员ni****g分享,可在线阅读,更多相关《基于FPGA等精度频率计设计》请在金锄头文库上搜索。

2023年地方税务局收入工作总结.docx

英语人教版必修3练习:Unit 3 Period 2 Learning about Language Word版含解析精修版

献爱心捐款募捐倡议书.doc

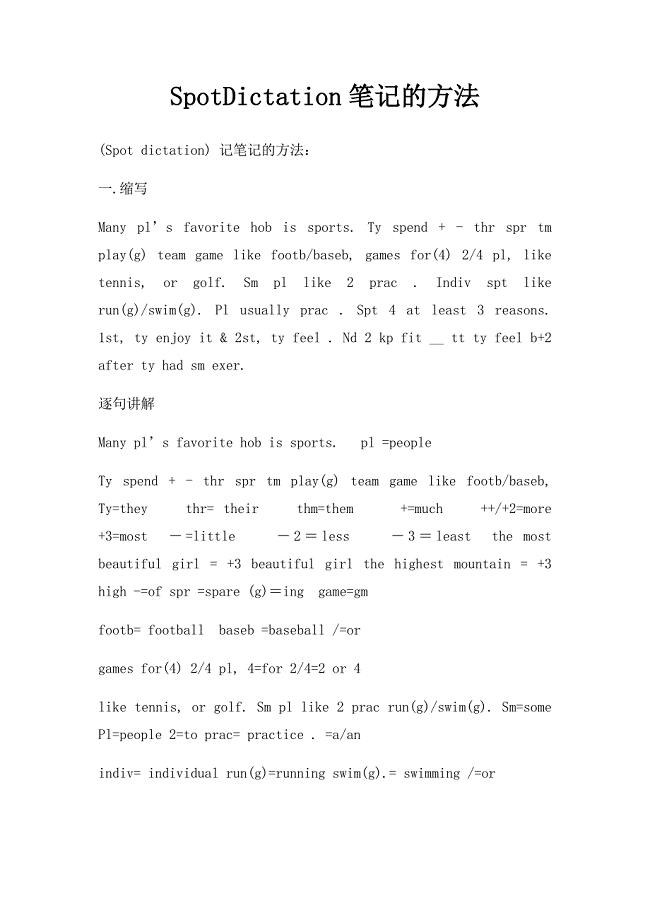

SpotDictation笔记的方法

2022关于描写景作文3篇

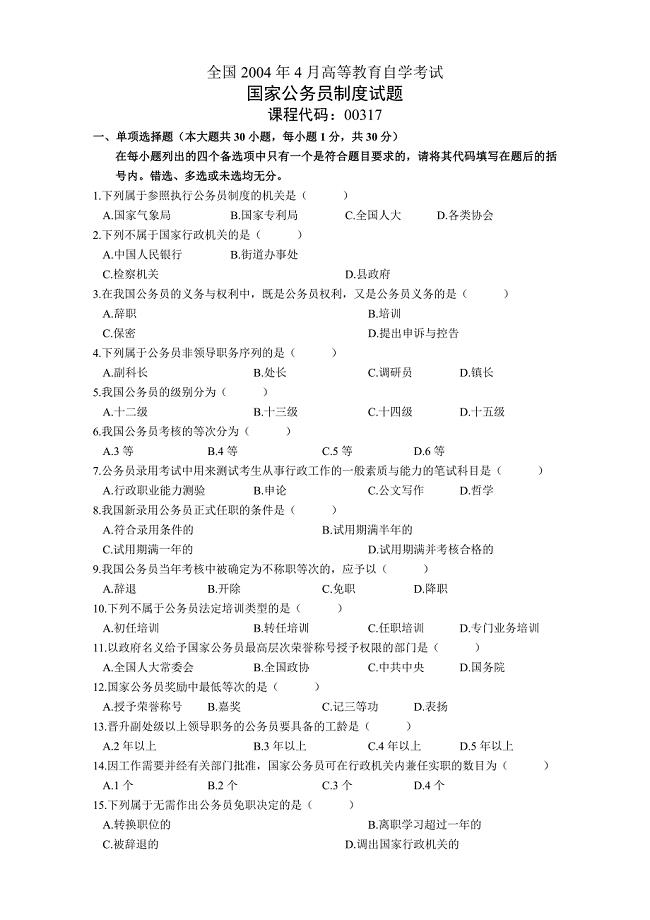

国家公务员制度及答案同名

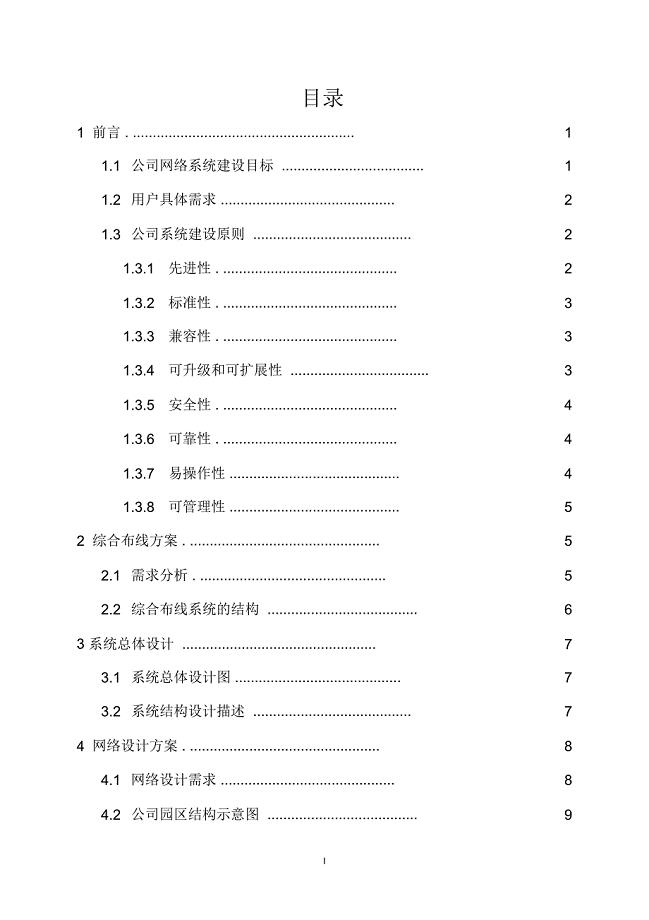

某公司网络系统集成方案设计

司法行政全年工作要点.docx

2023年国土局纪检监察工作要点.docx

咨询工具之客户体质调查

学习经济法的体会

2023年石油分公司质量月活动总结范文.doc

酒店电脑部的办公室工作总结范文.doc

2022星巴克圣诞节营销活动方案

精选物流业年终工作总结范文合集6篇

包村干部个人工作总结.docx

五年级列方程解决问题教学设计.doc

2023年论我国古建筑征收程序的完善.docx

包装bbet

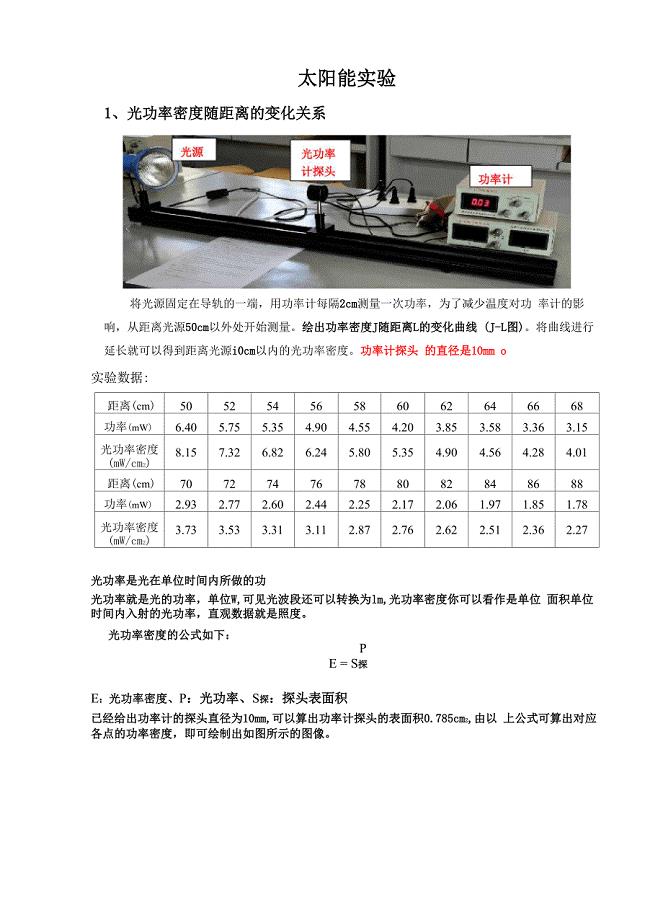

太阳能实验

我国幼小衔接的策略探析

我国幼小衔接的策略探析

2023-10-01 7页

园林植物保护问题以及应对措施

园林植物保护问题以及应对措施

2023-08-01 4页

电子商务立法推动网络经济发展

电子商务立法推动网络经济发展

2023-12-09 3页

建筑工程成本控制即时化探讨

建筑工程成本控制即时化探讨

2023-12-21 6页

吨每天线路板废水处理工程设计毕业论文

吨每天线路板废水处理工程设计毕业论文

2023-07-28 49页

冬季低温下混凝土的施工

冬季低温下混凝土的施工

2023-08-15 48页

高中物理教学论文资料2高考评卷潜规则及应试策略

高中物理教学论文资料2高考评卷潜规则及应试策略

2024-01-27 3页

论南非宪法法院对艾滋病人平等权的保护从霍夫曼诉南非航空公司案谈起

论南非宪法法院对艾滋病人平等权的保护从霍夫曼诉南非航空公司案谈起

2022-11-06 8页

试论幼儿园游戏教学现状与相关问题解决策略

试论幼儿园游戏教学现状与相关问题解决策略

2023-09-06 5页

江苏某中学办公楼设计论文计算书

江苏某中学办公楼设计论文计算书

2023-12-20 166页