半定制设计——74LS169计数器功能模块分析

30页1、数字集成电路课程设计实践教学要求与任务: 74ls169计数器:(1)74LS169计数器功能模块;(2)工作时钟10kHz即可;(3)使用SMIC工艺库smic18mm_1P6M完成设计;(4)完成全部流程:设计规范文档、模块设计、代码输入、功能仿真、约束与综合、布局布线、时序仿真、物理验证等。工作计划与进度安排:第1-2天:讲解题目,准备参考资料,检查、调试实验软硬件,进入设计环境,开始设计方案和验证方案的准备;第3-5天:完成设计,经指导老师验收后进入模块电路设计(验收设计文档);第6-9天:完成模块电路代码输入,并完成代码的仿真(验收代码与仿真结果);第 9-10天:约束设计,综合(验收约束与综合结果);第11-12天:布局布线,完成版图(验收版图结果);第13-14天:物理验证、后仿真,修改设计(验收物理验证结果和时序仿真结果);第15天:整理设计资料,验收合格后进行答辩。摘 要计数器74ls169 为可预置的 4 位二进制同步加/减计数器。当置入控制端(LOAD)为低电平时,在CLOCK上升沿作用下,输出端dout(QAQD)与数据输入端din(AD)相一致。169 的计数

2、是同步的,靠CLOCK同时加在 4 个触发器上而实现。当ENP和ENT均为低电平时,在CLOCK上升沿作用下QAQD同时变化,从而消除了异步计数器中出现的计数尖峰。当计数方式控制(U/D)为高电平时进行加计数,当计数方式控制(U/D)为低电平时进行减计数。169 有超前进位功能。当计数溢出时,进位端(RC OUT)输出一个低电平。本文介绍了在Design Compiler下进行逻辑综合和脚本相关约束,然后根据DC综合后的网表,使用Encounter进行自动布局布线,再使用ModelSim进行功能后仿真、分析后仿真波形得出结果。完成了功能和时序仿真,从而保证了设计的功能与时序的正确性。关键词 计数器;Verilog HDL;tcl;仿真; Design Compiler;逻辑综合;Encounter;物理验证;后仿真;I目 录引 言11 功能描述及电路设计21.1 电路性能21.2 电路接口21.3 电路结构32功能仿真42.1 仿真的功能列表42.2 顶层仿真平台与激励42.3 电路功能仿真结果53约束及逻辑综合73.1 约束策略73.2 脚本73.3 综合文件93.4 综合环境103

3、.5 综合过程104 布局布线134.1 文件准备134.2 布局布线过程144.3 物理验证165 后仿真186 总结19参考文献20附录一21附录二23附录三26附录四27引 言集成电路是电子工业的基础。以集成电路为基础的电子信息产业的发展,对国民经济发展、产业技术创新能力的提高及现代国防建设都具有极其重要的作用。而集成电路设计业则是集成电路产业链的核心。随着集成电路技术的发展,集成电路设计的手段也经历了从手工设计到计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)。在20世纪90年代开始逐步发展到电子设计自动化(Electronics Design Automation,EDA)阶段。CAD/EDA工具已经成为当今集成电路设计和制造流程中的必不可少的部分1。Synopsys是为全球集成电路设计提供电子设计自动化(EDA)软件工具的主导企业。为全球电子市场提供技术先进的IC设计与验证平台,致力于复杂的芯片上系统(SoCs)的开发。同时,Synopsys公司还提供知识产权和设计服务,为客户简化设计过程,提高产品上市速度。Cadenc

4、e公司的电子设计自动化(Electronic Design Automation)产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,PCB设计和硬件仿真建模等。Cadence公司工具SoC encounter是一完整的设计平台,可以完成从RTL输入到GDS输出的所有半定制IC设计流程。我们在设计中主要采用其版图规划(Floorplan)、布局(placement)、布线(route)、时钟树综合(CTS)、信号完整性分析(SI),以及RC提取等功能,也就是完成后端设计。本设计采用Verilog HDL语言描述,设计一个计数器,Design Compiler进行约束及综合。Design Compiler的操作有Tcl命令来实现,使用Encounter进行布局布线,还要用Modelsim进行功能仿真和后仿真,实验环境为Linux操作系统。完成一次RISC程序存储器的全流程设计。1 功能描述及电路设计1.1 电路性能四位二进制同步计数器74LS169真值表见下图1.1.其中LD为置数端,当其为低电平时,

《半定制设计——74LS169计数器功能模块分析》由会员jiups****uk12分享,可在线阅读,更多相关《半定制设计——74LS169计数器功能模块分析》请在金锄头文库上搜索。

建立安全生产长效机制-共创和谐平安输气管道

土石方爆破工程设计方案

康师傅百货商场制度汇编之退换货管理办法

庙头中学2012年中考百日誓师大会学生代表发言稿

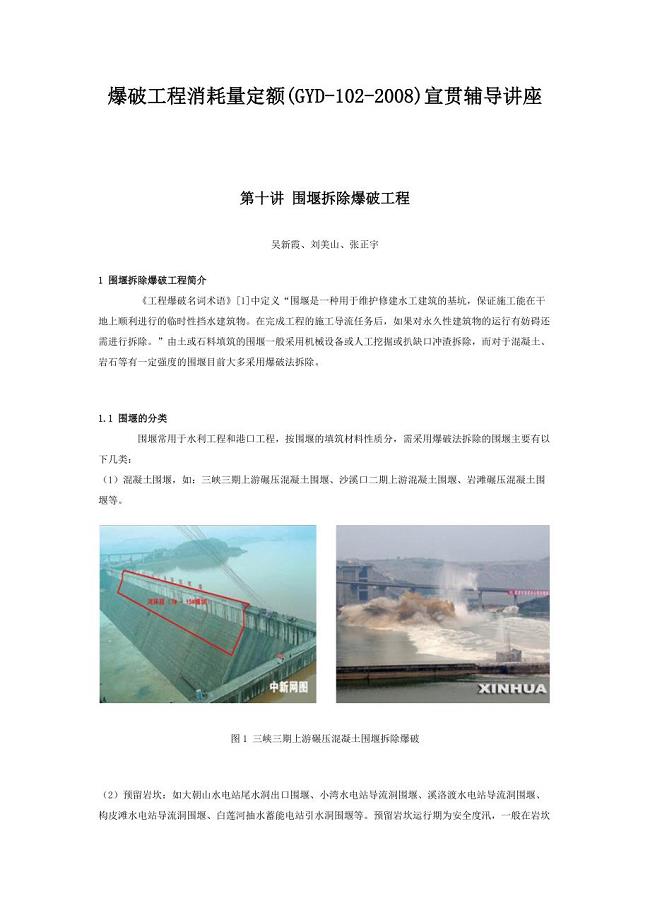

围堰拆除爆破工程

华能洱源马鞍山风电场工程土石方爆破管理制度

国资委:全面开展管理提升活动-为培育世界一流企业奠定坚实基础

《专业技术人员职业发展与规划》电子书

应收票据审计方案

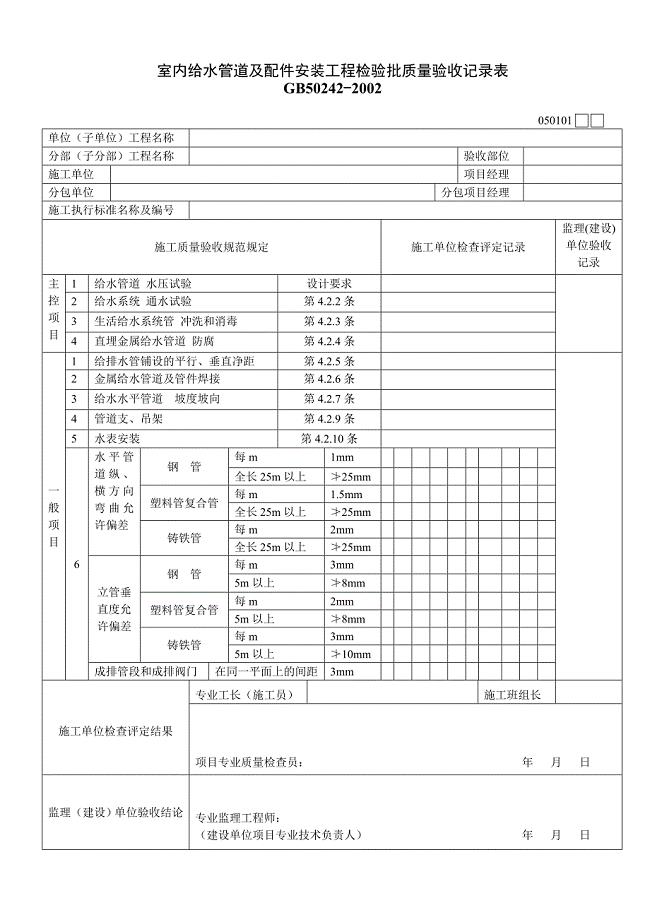

建筑给水排水与采暖工程质量验收用表

广播电视管理条例行政处罚裁量标准

广东电力系统调度运行操作管理规定

建筑给排水工程名词解释

幼儿园小班安全健康活动教案:宝宝误食后的急救

建业集团房屋建筑工程交房标准内容技术交底

建筑心理学论文(1)

康师傅百货商场制度汇编之工服管理程序009

建筑工程专业一级建造师继续教育培训结业报告20

廉洁风险防控回头看工作汇报材料

平台工作人员服务规范

小数数学题:简便计算11道练习题及参考答案A10

小数数学题:简便计算11道练习题及参考答案A10

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A7

小数数学题:简便计算11道练习题及参考答案A7

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A3

小数数学题:简便计算11道练习题及参考答案A3

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A5

小数数学题:简便计算11道练习题及参考答案A5

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A9

小数数学题:简便计算11道练习题及参考答案A9

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A6

小数数学题:简便计算11道练习题及参考答案A6

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A8

小数数学题:简便计算11道练习题及参考答案A8

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A1

小数数学题:简便计算11道练习题及参考答案A1

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A4

小数数学题:简便计算11道练习题及参考答案A4

2024-04-17 2页

小数数学题:简便计算11道练习题及参考答案A2

小数数学题:简便计算11道练习题及参考答案A2

2024-04-17 2页